基准集在嵌入式系统性能分析中的应用

王芳良,张伟功+,于立新,周海洋,庄 伟

(1.首都师范大学 信息工程学院,北京100048;2.北京微电子技术研究所,北京100076;3.北京市高可靠嵌入式系统技术工程研究中心,北京100048)

0 引 言

对嵌入式系统性能进行准确的量化分析,提供准确的性能指标,对充分发挥嵌入式处理器性能,了解嵌入式系统关键部件对系统性能的影响程度,提高嵌入式系统性能有着重要意义。基准程序法因直接、简单、低费用等优点被广泛地用于评估系统性能中,但一直以来对基准集的开发研究要远落后于对处理器设计的研究,尤其是面向工业控制、航空等领域的基准集更为落后。目前流行的基准集中SPEC CPU2006[1]和Linpack[2]主要用于通用处理器及大型处理器的定点浮点运算性能评估,但由于其对操作系统要求严格,很难应用于工业控制、航空领域无操作系统的嵌入式系统。Dhrystone[3]基准集被广泛应用于嵌入式处理器整数运算性能的评估,但代码量小,受编译器优化、库函数等因素的影响较大,测试结果已受到很大的质疑;MediaBench[4]基准集主要包含一些多媒体嵌入式应用程序,对嵌入式应用的覆盖面有限;EEMBC[5,6]基准集对嵌入式系统应用的覆盖很全面,但成本较高;MiBench[7]基准集覆盖了多种常见的嵌入式应用,但对编译器和系统库要求较高,移植和使用比较复杂;CoreMark[5,8-10]基准集是用来衡量嵌入式系统中心处理单元性能的标准,在设置上弥补了Dhrystone的不足,支持无操作系统的移植。非常适合工业控制、航空领域无操作系统的嵌入式系统的性能评估。Intel、Samsung Exynos、ARM、Freescale、IBM 等多款嵌入式处理器都采用CoreMark值作为处理器性能指标[11],但是国内还没有处理器厂商采用CoreMark基准集。本文将最新的应用于嵌入式处理器性能评估的CoreMark基准集移植到应用于工业控制的嵌入式系统中,通过改变嵌入式系统中的关键部件参数,来获得关键部件的性能加速比以及系统的最佳性能。

1 CoreMark基准集介绍

EEMBC 组 织 的Shay Gla-On 于2009 年 提 出 了 一 套CoreMark基准集,并且试图将其发展成为工业标准,从而代替陈旧的Dhrystone标准。CoreMark基准集是用来衡量嵌入式系统中心处理单元性能的标准。代码使用C 语言写成,移植性比较强,适合大部分的微控制器和微处理器。CoreMark基准集主要来自常用的一些算法,包含:列表操作 (寻找并排序),数学矩阵操作 (普通矩阵运算)和状态机 (用来确定输入流中是否包含有效数字),最后还包括CRC (循环冗余校验)[12]。

CoreMark基准集与Dhrystone相比有以下优势:①降低编译器对嵌入式系统性能的影响。通过对数据初始化、数据必须在运行时间内定义以及库函数调用不计入运行时间等规则来减少编译器对嵌入式系统性能的影响。②增加测试代码覆盖率与可预测性。CoreMark基准集没有采用简单的代码合成,而是由现实应用中的一些算法有机结合在一起。增加了测试代码的覆盖率和可预测性。③设定标准的运行条件和发布规则。CoreMark 基准集对如何运行CoreMark基准集以及如何输出测试结果做出了详细规定。必须输出编译器的型号、处理器型号、频率、Cache大小、有无操作系统,以及代码和数据的存储位置。这样测试结果才具有可比性。因此我们选择CoreMark基准集作为评测该嵌入式系统性能的基准集。

2 嵌入式系统环境搭建

嵌入式系统性能评测环境通常包括用于嵌入式系统评测的测试主机和将要被测评的嵌入式系统。测试主机通过串口与被测嵌入式系统进行数据的通信与交互。本文测试主机采用的是通用的PC,编译器采用的是GCC3.2.3。

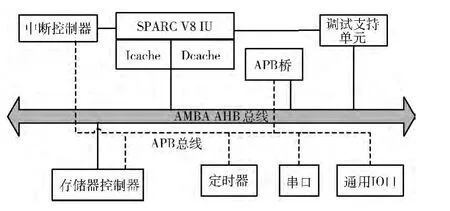

本文所用嵌入式系统采用的是一款Virtex5FPGA 开发板,将开源的基于SPARC V8体系结构的Leon2代码综合后烧写到FPGA 中。其结构框架如图1所示。

图1 嵌入式系统的结构框架

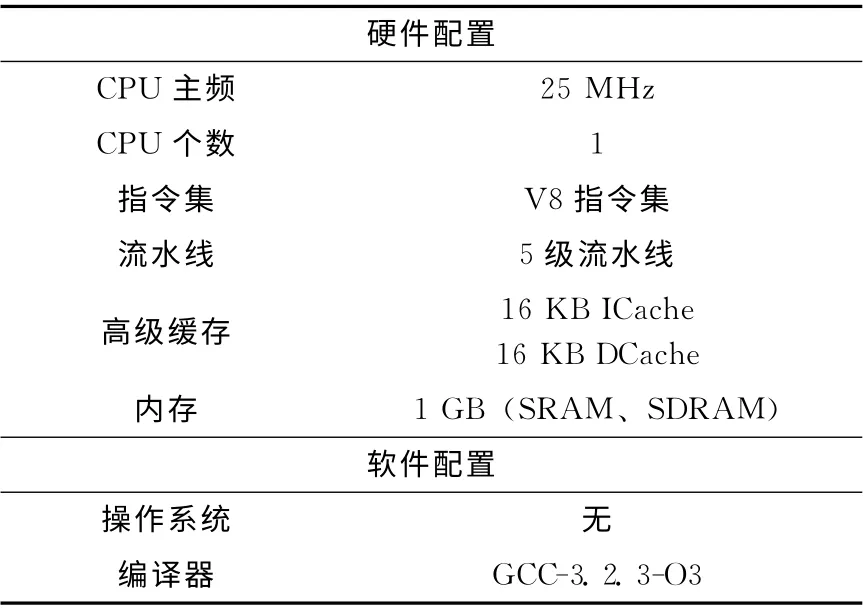

本文所述嵌入式系统测试环境配置见表1。以确保其他人根据这些条件能够得到相同的结果。这些条件包括硬件配置情况,也包括操作系统和编译器的版本等。

表1 嵌入式系统测试环境配置

3 CoreMark基准集的移植

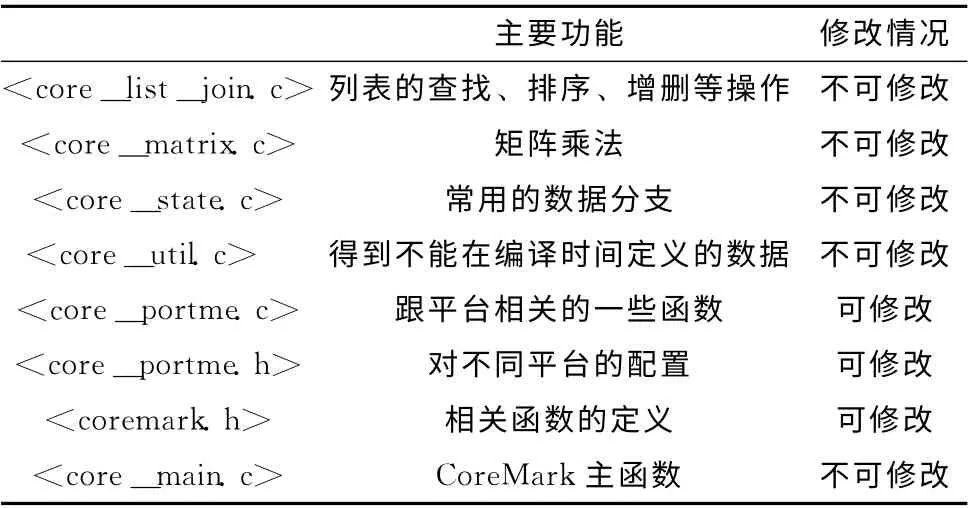

CoreMark基准集的移植分为有操作系统和无操作系统的移植。本文的移植是针对无操作系统情况下的移植过程。CoreMark基准集需要编译的文件见表2。

表2 CoreMark需要编译文件

根据本文所述的嵌入式处理器和嵌入式系统平台对CoreMark需要编译文件中的可修改部分进行设置。<core_portme.h>文件中主要是有关平台的宏定义,包括是否支持FLOAT,TIME_H,STDIO.H,CLOCK,以及PRINTF等操作。根据自己的平台对其进行配置。同时要设置所用编译器的版本以及编译类型标识。本文采用的是GCC_3.2.3,编译类型是-O3,所以需要设置为#define COMPILER_ VERSION gcc _ 3.2.3, # define COMPILER_FLAGS-O3。编译器和编译类型是CoreMark结果中重要的指标之一,所以必须进行修改。CoreMark基准集为了解决不同编译器的问题,对数据类型做了统一的定义,如果有不支持的数据类型可以在此进行修改,这样在工程中的其它文件中就可以保持数据类型的一致性,减少数据类型的修改。同时还要对线程数进行定义,本文采用的是单线程的,所以要在此文件中设置为#define MULTITHREAD 1。这样<core_portme.h>文件就修改完成。

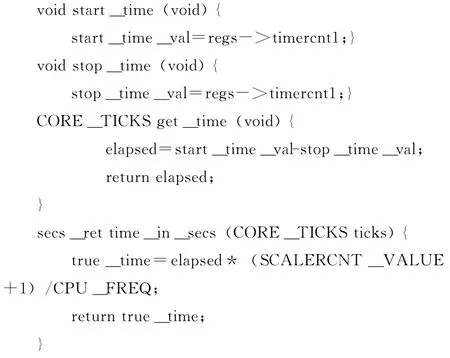

<core_portme.c>文件中主要包含了CoreMark基准集执行次数、处理器主频以及计算时间的函数。执行次数是通过seed4_volatile=ITERATIONS来进行修改的,次数可以任意修改,但是为了保证测试结果的正确性,要求必须使得运行时间在10-100秒之间,否则结果会报错。处理器主频通过一个简单的宏定义即可。关于时间计算的函数需要根据被测嵌入式系统的特点进行修改,文件中原本有的测试方法一般不适合现有的方式。这里需要对所用嵌入式系统的定时器进行操作,所以要在<core_portme.c>文件中先引入嵌入式系统的硬件配置文件。本文所述嵌入式系统采用的是24位定时器,每个定时器具有3个寄存器:预分频器、重载计数值寄存器和控制寄存器。预分频器为一个10位的减一计数器,由系统时钟定时,每个时钟周期减一。当产生下溢时,由预分频重载寄存器自动重新装载,同时产生定时脉冲,定时器的值就减一。每当定时器下溢时,就产生一个中断,通过设置定时器控制寄存器的加载位可以自动重载寄存器的值,同时定时器继续运行。为了不使中断的时间影响程序运行的整体时间,所以将定时器的重载值设置为最大,尽量避免中断。然后将文件中时间计算函数做了以下修改。

<coremark.h>文件中主要是有关函数和变量的定义,在<core_portme.c>文件中函数里用到的变量的定义都需在<coremark.h>文件中进行定义。

把以上文件修改完毕后,需要建立一个<main.c>文件作为工程的头文件,在这个文件中需要对所用嵌入式系统的相关寄存器进行初始化,然后再调用coremark_main()函数。这样整个移植过程就完成了。

4 测试方案及数据分析

由于嵌入式系统应用环境的特殊性,尤其是用于工业控制和航空领域的嵌入式系统,嵌入式系统的关键部件需要根据环境的需求配置成不同的值,而目前大部分嵌入式系统的性能指标都是在各个部件配置成最佳情况时测试所得,不能正确反映出嵌入式系统在不同环境下的性能。本文对嵌入式系统中SRAM、SDRAM、DCache、ICache、Burst模式以及影响它们内部的可配置因素进行分析,采用对比策略,改变其中1个参数,保持其它参数不变情况下,进行性能测试。得出嵌入式系统在不同的配置环境下的性能,可以为在特殊应用环境下的嵌入式系统提供性能对比的参数。同时可以获得某一参数的性能加速比,加速比是使用增强措施时完成整个任务的性能与不使用增强措施时完成整个任务的性能的比值[13,14]。加速比可以反映出该增强措施或关键部件对嵌入式系统整体性能提高的贡献值大小,加速比越大,表明增强措施对性能提高的效果越明显。借助性能加速比,可以量化的分析这一参数对整个嵌入式系统性能的影响程度。嵌入式系统设计者可以分析得出如何分配资源才能充分发挥处理器性能,提高嵌入式系统性能。为避免多个参数相互影响,在测试一个参数对嵌入式系统性能的影响时,关闭其它参数。

4.1 SRAM 对嵌入式系统性能的影响

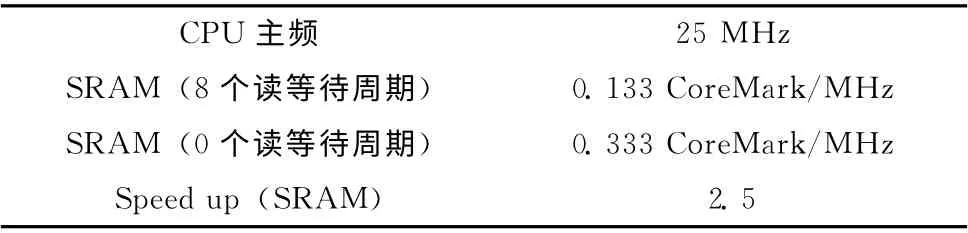

嵌入式系统中,当SRAM 选定后,影响SRAM 速度的可配置参数有读等待周期和写等待周期。研究SRAM 嵌入式系统性能影响时,为避免Burst模式、ICache和DCache对整体性能的影响,将Burst模式、ICache和DCache均关闭。同时把SRAM 的写等待周期设置为0,改变SRAM 的读等待周期,研究SRAM 的读等待周期对系统整体性能的影响。读等待周期分别为0和8个时钟周期时嵌入式系统的性能 (CoreMark/MHz)见表3。SRAM 读等待周期为0时的嵌入式系统性能明显高于读等待周期为8的性能,且加速比为2.5。在Burst模式、ICache和DCache均关闭的情况下,处理器每次读取数据都需要从SRAM 中获取,从处理器RTL级仿真中可以发现,SRAM 在0读等待周期和0写等待周期的情况下,处理器读取一个数据需要5个时钟周期。当读等待周期为8时,处理器读取一个数据需要13个时钟周期,时间是原来的2.6倍。通过从RTL 级的时序分析也证明了CoreMark 基准集测试的正确性。SRAM 的写等待周期同样影响整个系统的性能。其测试方法同读等待周期的测试方法相同,在此不再做详细的论证。因此,由上述测试结果,可以看出SRAM 的读写等待周期对嵌入式系统性能的影响程度。而一般情况下,SRAM 的读写等待周期都会默认设置为最大。用户在使用嵌入式系统时,为提高系统性能,要在时序允许的情况下,尽量把SRAM的读写等待周期设置为最小。

表3 SRAM、SDRAM 对嵌入式系统性能的影响

4.2 SDRAM 对嵌入式系统性能的影响

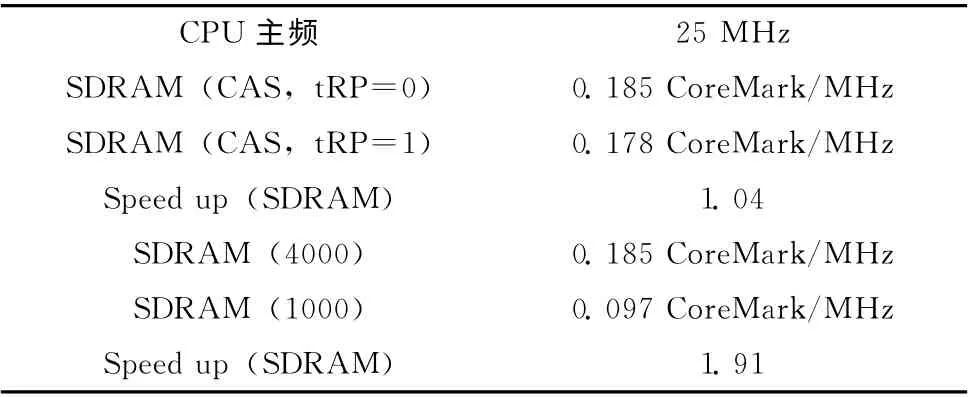

嵌入式系统中,当SDRAM 选定后,影响SDRAM 速度的主要有CAS 延迟、tRP、刷新间隔时间和刷新时间。同样为避免其它因素的干扰,将Burst模式、ICache 和DCache全部关闭。本嵌入式系统中采用的SDRAM 的刷新间隔时间所允许的最大时钟周期为4800,本次实验分别采用1000 和4000。而刷新时间为固定值不能修改。从SDRAM 读时序中可以分析得到CAS延迟和tRP 均置为0和均置为1时,SDRAM 读取一个数据分别需要8个和10个时钟周期,与刷新时间相比,CAS延迟和tRP 对系统性能的影响较小。为看到实验效果,所以将CAS延迟和tRP同时置1 或0。根据分析设计两套测试方案,分别评测CAS延迟、tRP和刷新间隔时间对嵌入式系统性能的影响。方案一:在刷新间隔时间设置为4000时,测试CAS延迟和tRP分别为0 和1 情况下嵌入式系统的性能。方案二:在CAS延迟和tRP 均为0 时,测试刷新间隔时间分别为1000和4000时嵌入式系统的性能。测试结果见表4。

表4 SDRAM 对嵌入式系统性能的影响

由表4的前3行数据,可以看出,在刷新间隔时间和刷新时间一定的情况下,CAS延迟和tRP 由全1变为全0时,嵌入式系统的性能有所提高,但是对嵌入式系统性能的影响不大,这与我们之前的预测是一致的。当CAS延迟和tRP一定的情况下,刷新间隔时间由1000变为4000时嵌入式系统性能得到了较大的提升。因为处理器从SDRAM 中读取一个数据的时间是由SDRAM 读时序的时间与定期刷新所花费的时间,当刷新间隔时间变大,处理器从SDRAM 中读取的数据的速度就会提升。所以用户在使用SDRAM 时,要根据SDRAM 的最大刷新间隔时间参数,将这个值尽量配置为最大,来提高嵌入式系统性能。同时在时序允许的情况下,可以将CAS延迟和tRP的值配置为0,适当的提高系统的性能。

在工程实践中,常常面临着选择SRAM 还是SDRAM来存储程序和数据。由表3 的SRAM (0 读等待周期)和表4中SDRAM (CAS和tRP均为0)的嵌入式系统性能可知,在Burst 模 式、ICache 和DCache 都 关 闭 的 情 况 下,SRAM 的读写速度要明显高于SDRAM 的速度,嵌入式系统的性能提高了1.8倍。这些数据可以帮助嵌入式系统设计者在特殊的应用环境中 (如不能打开Cache或Burst模式)做出合理的选择。

4.3 Burst模式对嵌入式系统性能的影响

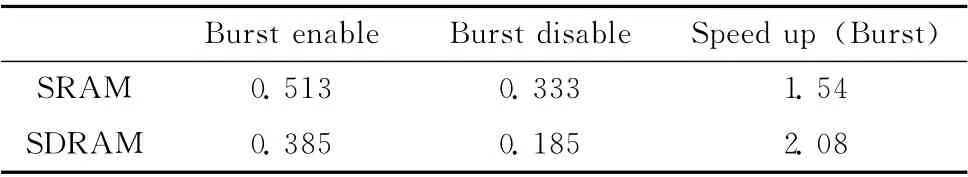

Burst模式是针对读写存储器太慢而设置,Burst模式可以一次性地读出成组数据到内部寄存器或Cache,一次读取数据的个数由Burst Length决定,常见有1,2,4和8。本文的嵌入式处理器采用的是Burst Length 为8 的取指Burst模式,对SRAM 和SDRAM 的取指操作都会起到作用。Burst模式打开后,处理器可以一次读取连续的8个数据,大大减少了取指周期,进而提高嵌入式系统的整体性能。为研究Burst模式对系统性能的影响程度,需要关闭ICache和DCache。分别测试在SRAM 和SDRAM 情况下Burst模式打开后系统的性能,结果见表5。

表5 Burst模式对嵌入式系统性能的影响

由表5可以看出,Burst模式打开后,嵌入式系统的性能得到了很大程度的提高,且在SDRAM 情况下系统性能的加速比要大于SRAM 情况下的加速比。根据嵌入式处理器RTL级SRAM 和SDRAM 在Burst模式下的时序图,处理器一次从SRAM 和SDRAM 读取连续8个数据分别需要19和15加上定期刷新时间。而如果在Burst模式关闭的情况下,处理器一次从SRAM 和SDRAM 读取连续8个数据分别需要40和64加上定期刷新时间。可见Burst模式对嵌入式处理器性能的影响很大,所以用户在环境条件许可的情况下,尽量要打开Burst模式。而嵌入式处理器设计时也应该尽量将Burst Length设置为较大值。

4.4 Cache对嵌入式系统性能的影响

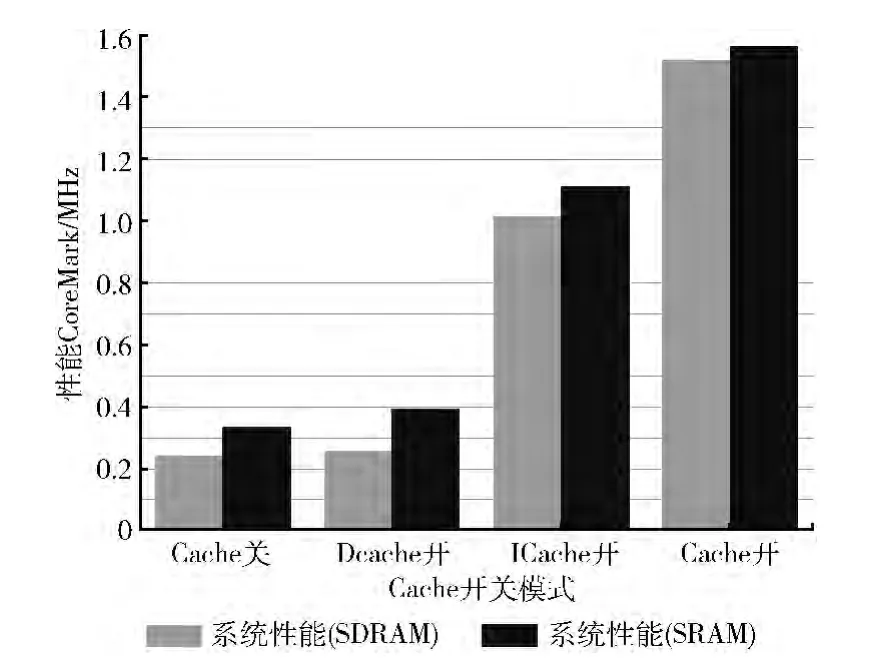

Cache是提高处理器及嵌入式系统性能的关键部件,能够大幅度提高处理器的读取速度,提升处理器性能,进而提升嵌入式系统的性能。但是在工业控制和航空一些特殊环境下,Cache并没有打开。为能定量的分析Cache对嵌入式系统性能的影响,本文在Burst模式关闭的情况下,研究程序分别在SRAM 和SDRAM 时,DCache、ICache分别打开关闭对嵌入式系统性能 (CoreMark/MHz)影响,结果如图2所示。

图2 Cache对嵌入式系统性能的影响

由图2可以看出,当仅打开DCache时,在SDRAM 和SRAM 中的嵌入式系统的性能加速比分别为1.38和1.18;当仅打开ICache时,嵌入式系统的性能加速比分别为5.46和3.34;当把Cache全部打开时,加速比分别为8.19 和4.55。根据各种模式下性能加速比,可以看到嵌入式系统性能都有提升。ICache对嵌入式系统性能的影响要高于DCache的影响,了解ICache和DCache在嵌入式系统性能优化中所占比重,帮助嵌入式处理器设计者根据处理器应用环境,合理安排ICache 和DCache 的大小。同时看到Cache全部打开后,嵌入式系统性能有了大幅度的提升,尤其是嵌入式系统采用SDRAM 作为外存时,这一数据可以告诉用户在环境允许的情况下,要尽量打开Cache,充分发挥嵌入式处理器性能,提高嵌入式系统性能。

4.5 嵌入式系统性能优化的方案

根据以上关于SDRAM、SRAM、Burst模式、ICache和DCache这些关键部件对嵌入式系统性能 (CoreMark/MHz)影响的分析,可以量化的得到这些关键部件在嵌入式系统性能优化中的影响程度。其影响嵌入式系统性能的程度大小依次是Cache,Burst模式,SDRAM 的刷新间隔时间,SRAM 的读写等待时间,SDRAM 的CAS 延迟和tRP。根据这些影响程度,可以做出两套性能优化方案:一是将程序和数据存入SDRAM 中时,SDRAM 的CAS延迟和tRP设置为0,SDRAM 刷新价格时间设置为最大,打开Cache,打开Burst模式,嵌入式系统性能可以达到最大优化。二是将程序和数据存放在SRAM 中时,SRAM 的读写等待周期设置为0,打开Cache,打开Burst模式,嵌入式系统性能可以达到最大优化。根据特定的应用环境灵活的改变以上两种方案的某些参数,可以使嵌入式系统在该特定环境下达到最佳性能。

根据以上两个方案,在主频25 MHz的情况下,分别对CoreMark基准集下载在SDRAM 和SRAM 中嵌入式系统的性能做出测试,结果两种方案的测试结果几乎相同,且都达到了最大的CoreMark 值。因为Burst模式、Cache打开后,Cache的命中率较高,从主存中访问的比重很小,再加上Burst模式的作用,SDRAM 和SRAM 访问速度的差异进一步缩小。对嵌入式系统性能影响的比率很低,因此两种优化方案下嵌入式系统的性能可以达到相同的值。最终该嵌入式系统的性能测试结果为CoreMark 1.0:39.075/GCC 3.2.3-O3,CoreMark/MHz 1.0A1C31.563/GCC 3.2.3-O3。

5 结束语

本文将目前最新的用于嵌入式处理器性能评测的CoreMark基准集用于面向工业控制的嵌入式系统的性能分析,弥补了长期使用Dhrystone基准集作为嵌入式处理器性能评估的不足。准确评估出嵌入式系统的性能,丰富了同国外先进处理器性能比较的指标。同时对嵌入式系统中的关键部件SDRAM、SRAM、ICache、DCache、Burst模式以及它们各自内部的一些因素做了仔细分析。量化的得出它们分别对嵌入式系统的性能的影响程度。为嵌入式系统设计者充分发挥嵌入式处理器性能,优化嵌入式系统性能提供有力支持。但是CoreMark基准集主要是针对整数运算性能,对于浮点运算性能的评估仍需要进一步研究。

[1]Anthony Gutierrez,Ronald G Dreslinski,Thomas F Wenisch,et al.Full-system analysis and characterization of interactive smartphone applications [C]//IEEE Int Symp on Workload Characterization,2011:81-89.

[2]Alexander Heinecke, Karthikeyan Vaidyanathan, Mikhail Smelyanskiy.Design and implementation of the Linpack benchmark for single and multi-node systems based on IntelRXeon PhiTMcoprocessor[C]//IEEE 27th International Symposium on Parallel &Distributed Processing,2013:126-136.

[3]Nabil Litayem,Bochra Jaafar,Slim Ben Saoud.Embedded microprocessor performance evaluation case study of the Leon3 processor[J].Journal of Engineering Science and Technology,2012,7 (5):576-586.

[4]Zhang Tiefei,Yu Licheng,Chen Tianzhou,et al.Process scheduling-based energy management for bank-aware memory system [J].Journal of Information &Computational Science,2012 (9):4013-4015.

[5]Shay Gal-On,Markus Levy.Creating portable,repeatable,realistic benchmarks for embedded systems and the challenges thereof[C]//ACM,2012:149-152.

[6]Marisha Rawlins,Ann Gordon-Ross.On the interplay of loop caching,code compression,and cache configuration [C]//IEEE,2011:244-248.

[7]Jeyaraj Andrews,Thangappan Sasikala.Evaluation of various compiler optimization techniques related to mibench benchmark applications[J].Journal of Computer Science,2013,9 (6):749-756.

[8]Maheswari R,Pattabiraman V.Performance evaluation of OR1200 processor with evolutionary parallel HPRC using GEP [J].ICTACT Journal on Soft Computing,2012,2 (3):331-336.

[9]EmilyBlem,Jaikrishna Menon,Karthikeyan Sankaralingam.A detailed analysis of contemporary ARM and x86architectures[C]//The 19th IEEE Intl Symposium on High Performance Computer Architecture,2013:4-11.

[10]Igor Bohm,Bjorn Franke,Nigel Topham.Cycle-accurate performance modeling in an ultrafast just-in-time dynamic bi-nary translation instruction set simulator [C]//IEEE,2010:1-8.

[11]Shay Gal-On,Markus Levy.CoreMark instruction [EB/OL].[2013-12-20].http://www.CoreMark.org.

[12]Shay Gal-On,Markus Levy.The embedded microprocessor benchmark consortium:EEMBC bench-mark suite [EB/OL].[2013-12-20].http://www.eembc.org.

[13]John L Hennessy,David A Patterson.Computer architecture:A quantitative approach [M].4th ed.Beijing:Publishing House of Electronics Industry,2007:23-30 (in Chinese).[John L Hennessy,David A Patterson.计算机系统结构:量化研究方法 [M].4版.北京:电子工业出版社,2007:23-30.]

[14]John L Hennessy,David A Patterson.Computer organization and design:The hardware/software interface [M].3rd ed.Beijing:China Machine Press,2007:168-178 (in Chinese).[John L Hennessy,David A Patterson.计算机组成与设计:硬件/软件接口 [M].3版.北京:机械工业出版社,2007:168-178.]