集成电路FT制程高压测试方法研究

姚 锐,周 淳,张亚军,倪晓丽

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

随着经济发展和技术的进步,集成电路产业取得了飞速的发展。现在城市的每个角落随处可见光彩夺目的大型户外显示屏,几乎每个家庭都拥有液晶电视、液晶显示器、电源充电器等,它们正常稳定的工作都依赖于电源管理系统,实现AC/DC和DC/DC等的转换。

随着绿色电源的兴起,追求更高的能量转换效率,越来越多的MOS器件应用于电源管理模块。MOS器件的耐高压测试即耐电压强度测试是检测电源管理电路的一项重要指标。在集成电路FT制程中主要通过自动分选机金手指单元实现测试资源对于被测器件的激励,主要有自动分选机夹测和自动分选机压测两种实现方式。

2 集成电路测试的目的及其相应流程

2.1 测试的意义

测试是一个实验的过程,在这个过程中运行系统并分析它的响应结果,以判断该系统是否正常运行。测试的准确性和可靠性对于产品质量非常重要。集成电路测试主要指对其各种应用的数字集成电路、模拟集成电路和数模混合信号集成电路的测试,检测集成电路芯片中由生产制程等可能引入的缺陷。测试的意义不仅仅在于判断被测试器件是否合格,还可以提供关于制造过程的有用信息,从而有助于提高成品率;同时还能反馈设计方案可能存在的薄弱环节,有助于检测出设计方面的问题。集成电路测试主要有两个节点:晶圆级测试,简称CP测试;成品测试,简称FT测试(本论文研究的测试节点)。

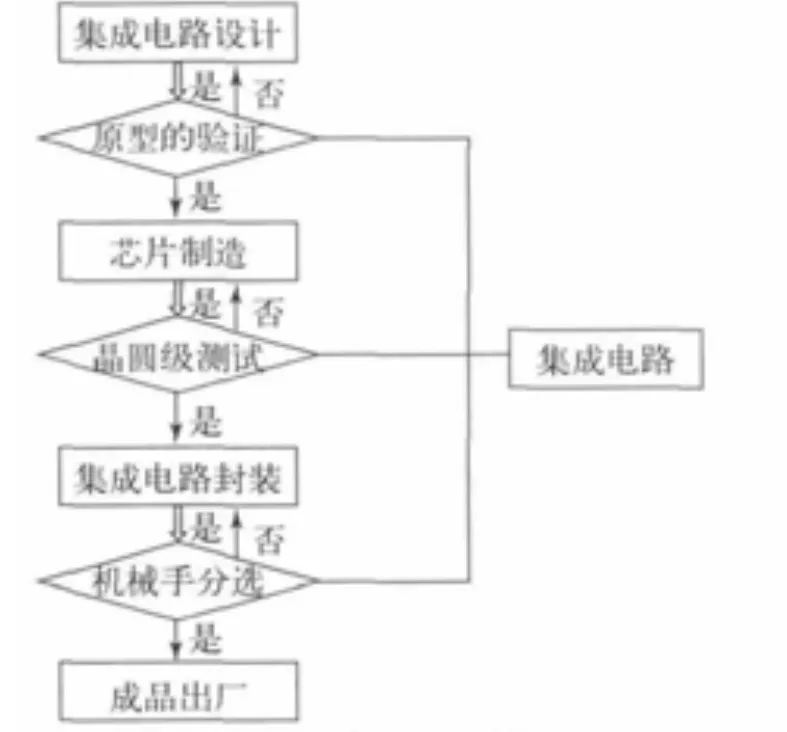

2.2 集成电路测试流程

集成电路测试的流程如图1所示。

图1 集成电路测试流程

2.3 FT封装形式

集成电路的封装类型有很多,有DIP/SOP/SSOP/TSOP/QFN/BGA/TO系列等,本论文主要就DIP/SOP两种常见的封装形式的集成电路高压测试方法进行研究。

3 测试技术

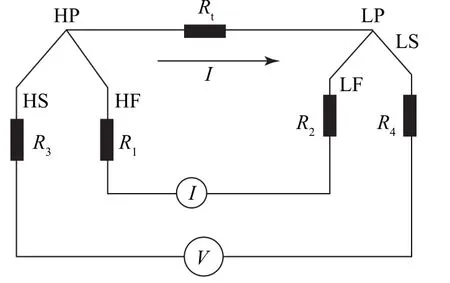

当被测电阻阻值小于几欧,测试引线的电阻和金手指与测试点的接触电阻与被测电阻相比已不能忽略不计时,若仍采用两线测试方法必将导致测试误差增大。此时可采用开尔文连接方式(或称四线测试方式)来进行测试,如图2。

开尔文连接有两个要求:对于每个测试点都有一条激励线F和一条检测线S,二者严格分开,各自构成独立回路。同时要求S线必须接到一个有极高输入阻抗的测试回路上,使流过检测线S的电流极小,近似为0。

图2中R表示引线电阻和金手指与测试点的接触电阻之和。由于流过测试回路的电流为0,在R3、R4上的压降也为0,而激励电流I在R1、R2上的压降不影响I在被测电阻上的压降,所以电压表可以准确测出Rt两端的电压值,从而准确测量出Rt的阻值。测试结果和R无关,有效减小了测量误差。按照作用和电位的高低,这4条线分别被称为高电位施加线(HF)、低电位施加线(LF)、高电位检测线(HS)和低电位检测线(LS)。

图2 开尔文连接测试

4 高压测试问题的研究解决

4.1 高压测试需要条件

行业主流的集成电路耐压测试要求提供的高压为 700~1 200 V。

下面是一段高压测试施加及测试条件:

HKV_SetMode(0,0,900,10);//0通道测量漏电流,最高输出电压900 V,最大测量电流10 mA。

DelaymS(5);

HKV_SetMode(0,1,5,900);//0通道测量耐压,最高输出电流5 mA,最大测量电压900 V。

DelaymS(5);

HKV_SetOutVal(0,-0.25);

DelaymS(10);

HKV_MeasureV(0);

VBDS=pSite->RealData[0];

4.2 高压测试核心解决点

根据大批量产品的生产跟踪和过程出现异常的分析结果,高压测试主要解决两个核心问题,全自动分选机的金手指碳化处理和绝缘处理等,而这两个问题又彼此包含。

4.3 高压测试碳化及处理方法

本文讨论的测试结构为图1的夹测测试。在高压测试过程中由于金手指与被测试电路长时间频繁的接触,尤其是被施加高压的管脚与其接触的金手指之间会产生“碳化”现象。碳化即金手指与被测试电路管脚之间由于长时间频繁在高压环境下接触形成的氧化现象。当碳化达到一定程度就会在金手指表面形成厚厚的氧化层,从而严重影响到金手指与被测试电路之间的接触阻抗。起初的碳化消除方法是进行粗糙化处理,即用规格1200CW的砂纸擦拭金手指的氧化层,尽可能露出原先合金的本色,但由于多次的擦拭会导致金手指平整度变差,从而出现接触不良或打管脚现象,大大缩短了金手指的使用寿命。

4.4 高压测试预防碳化优化方案

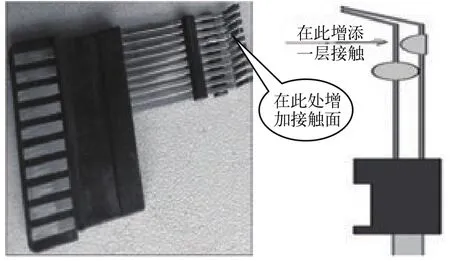

为了减少金手指的损耗,节约生产成本,同时提升测试质量,需要寻求新方法解决金手指碳化问题。经过长期跟踪观察,比对了夹测和压测的生产过程发现,夹测金手指与被测试电路接触是点与面的接触,而压测是面与面的接触。接触面积的增加确保了各种激励施加的可靠性和准确性。为了缓解在高压夹测试情况下对金手指的碳化损伤,增大金手指与被测试电路管脚之间的接触面积可以大幅缓解这种现象的发生。

图3为优化后的方案。

图3 金手指用于高压测试的优化处理

4.5 高压测试“打火”和通讯紊乱

生产过程中,操作人员反馈高压测试过程中会频繁出现“打火”现象,且个别批次特别明显。经过一段时间的跟踪观察发现,由于集成电路在封装工序中因不同厂家封装工艺的差异,导致封装好的集成电路上下两侧存在露铜线现象,此铜线与电路内部是相通的,有的甚至是与源端相连。由于集成电路在被测试之前是停放在测试区的测试挡板上,此测试挡板的结构是导电性能很好的铁,与整个测试机是一个整体。当对集成电路进行耐压性能测试的时候,就会产生短路从而出现“打火”现象,产生一系列意想不到的后果,如直接烧毁集成电路、导致操作人员被电击等。

其中最常见也是最令人烦恼的是导致自动分选机和测试系统之间的通讯信号混乱。因为自动分选机通讯板上的“地”与整个分选机是同一个“地”,高压信号通过导电性能良好的测试挡板传递到了通讯板上,使得通讯板受到很强的外来信号干扰发生紊乱,无法正常接收测试系统发来的信号,不能完成正常的生产流程,同时伴随很大的质量风险。

4.6 高压测试的绝缘处理

为了避免以上现象的发生,起初是在测试挡板上粘贴绝缘胶带,粘贴绝缘胶带后异常现象得到较大缓解,但并没有真正完全解决绝缘的问题,持续时间也只有短短的两三天周期。分析原因在于测试挡板很窄,绝缘胶带很难牢固地粘连在上面,且绝缘胶带的抗耐磨性很差,很容易损坏。

经过一段时间的思考,选择在测试挡板上涂环氧树脂胶,固化后的环氧树脂分子结构致密同时具有很强的内聚力、突出的尺寸稳定性、耐久性及其优异的电绝缘性能,对绝大多数金属和非金属都有很好的粘结性。

经过一段时间的使用发现效果比较理想,比起初粘贴绝缘胶带的效果有了很大的改善:

第一,避免了如绝缘胶带粘连性不好导致的脱落现象;

第二,比起绝缘胶带的抗耐磨性和电绝缘性也有了很大的提升,由原来两三天的使用寿命提升到20天左右。

但由于测试产能的提升加上需要测试高压产品的增多,20天的使用寿命仍远远达不到生产需求,急需寻找一种更加可靠和持久的解决方案。

图4 测试挡板的绝缘处理

现有设计在测试挡板上嵌贴陶瓷片做电绝缘处理,如图4在测试挡板上嵌贴陶瓷片。选择陶瓷片是因为陶瓷片具有极佳的电绝缘性与抗耐磨性,经过一段时间的使用效果卓越,比起环氧树脂胶,陶瓷片的耐磨系数是固化后环氧树脂的40~50倍。这就基本从根源上解决了高压测试伴生的各种异常问题。

5 结束语

任何一块集成电路都是为完成一定的电特性功能而设计的单片模块,IC测试就是集成电路的测试,就是运用各种方法,检测那些在制造过程中由于物理缺陷引起的不符合要求的样品。如果存在无缺陷产品的话,集成电路的测试也就不需要了。由于实际制造过程所带来的以及材料本身或多或少都有的缺陷,无论怎样完美的产品都会产生不良的个体,因此测试也就成为集成电路制造中必不可少的工程之一。而集成电路FT制程高压测试则是一系列集成电路测试的重要指标测试,有别于常规的常压测试,是一个新的测试领域,需要拓展思路,寻求更准确和完美的解决方案。

[1] 半导体集成电路测试的基本原理[M]. 北京:电子工业出版社.

[2] 集成电子线路设计[M]. 福州:福建科学技术出版社.

[3] 集成电路测试技术[M]. 北京:人民邮电出版社.