CSNS多丝正比室读出电子学

任海龙 赵豫斌 文双春 鲁睿其

1(湖南大学 物理与微电子科学学院 长沙 410082)

2(东莞中子科学中心 东莞 523808)

CSNS多丝正比室读出电子学

任海龙1,2赵豫斌2文双春1鲁睿其1,2

1(湖南大学 物理与微电子科学学院 长沙 410082)

2(东莞中子科学中心 东莞 523808)

中国散裂中子源(China Spallation Neutron Source, CSNS)中的多功能反射谱仪采用二维多丝正比室探测器(Multi-Wire Proportional Chamber, MWPC)来获取入射中子的位置信息。本文介绍了一种结构简单的MWPC位置读出方法。该方法采用挪威IDEAS公司的64通道电荷灵敏专用集成电路(Application Specific Integrated Circuit, ASIC) VA64tap2.1,克服了传统方法硬件复杂、功耗大、成本高的缺点。另外,系统可通过测量阳极电荷量区分中子和γ射线,提高测量精度。在现有条件下对读出系统进行测试,测试结果表明:系统能完成读出任务,且所选ASIC芯片功耗低(每通道0.3 mW)、噪声小(<0.35 fC)、动态范围大(−200–+160 fC)、集成度高(单片64通道),可用于MWPC探测器的位置读出。

多丝正比室探测器,中国散裂中子源,专用集成电路,电荷测量,可编程门阵列

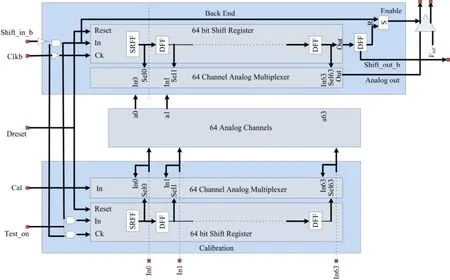

中子是人们了解物质微观结构的重要探针之一。常见的中子源有放射性核素中子源、反应堆中子源及散裂中子源三种。散裂中子源是由高能质子轰击重金属靶产生中子的大科学装置,它为生命科学、材料科学、化学、物理学等领域的基础研究和相关高新技术开发提供了强有力的研究手段[1]。作为中国第一台散裂中子源,中国散裂中子源(China Spallation Neutron Source, CSNS)将和正在运行的IPNS (Intense Pulsed Neutron Source)、KENS、ISIS一起,构成世界四大脉冲散裂中子源。CSNS一期将建设通用粉末衍射仪、小角散射仪和多功能反射仪三台谱仪[2],其中多功能反射仪的探测器部分采用二维多丝正比室结构[3]。它由阳极平面(介于二维位置读出平面之间)、X读出平面(取向与阳极丝平行,丝间间距1.5mm)、Y读出平面(取向与阳极丝垂直,丝间间距4mm)以及顶部的阴极平面构成。实验时,阳极平面和阴极平面分别加正负高压,中子通过入射窗进入充3He气体的丝室,发生反应:

反应产生的质子和氚核在运动过程中电离工作气体并产生大量初始电子-离子对,电离电子在电场作用下漂向阳极并在阳极丝上发生雪崩倍增,雪崩产生的正离子向阴极漂移时在二维位置读出丝上感应出的信号。读出电子学有两个任务:(1) 测量二维位置读出丝上信号以确定入射中子位置;(2) 测量阳极平面电荷量以区分中子和γ射线。

传统的多丝正比室探测器(Multi-Wire Proportional Chamber, MWPC)位置和电荷量读出通常采用分立元器件和运放,搭建电荷灵敏积分前放、滤波成形、峰值保持、模数转换以及控制电路。随着探测器通道数的增多,传统读出方法集成难度高、系统可靠性低、功耗大等缺点越来越突出。为降低系统功耗、减小系统占用空间,使用低噪声、低功耗、高集成度的专用集成电路(Application Specific Integrated Circuit, ASIC)更具实用意义。

1 VA64tap2.1介绍

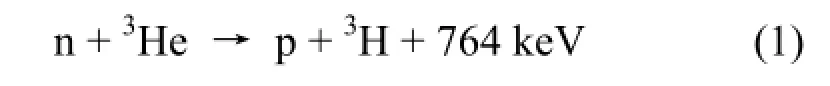

VA64tap2.1[4]是挪威IDEAS公司设计的一款64通道电荷测量ASIC芯片,其动态范围为−200– +160fC。单通道由电荷灵敏积分前放、滤波成形、过阈比较及峰值保持电路组成,结构如图1所示。

图1 VA64tap2.1单通道结构Fig.1 VA64tap2.1 channel architecture.

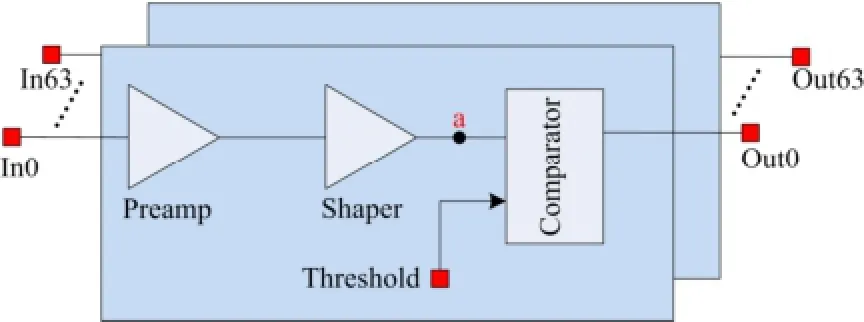

VA64tap2.1内部结构如图2,通过配置内置寄存器Ctrl_reg,芯片可工作于正常和测试两种模式:正常工作模式下,VA64tap2.1对64路信号进行电荷积分、成形并以过阈触发方式并行输出,输出的信号经LS64_2[5](VA系列芯片专用输出信号电平转换ASIC,IDEAS公司生产)转换电平后送现场可编程门阵列(Field-Programmable Gate Array, FPGA)进行位置测量;测试模式下,外部电荷注入测试管脚Cal,配置Ctrl_reg选定被测通道后,信号经电荷积分、成形后由图1中a点输出。通过峰值保持信号holdb保持各通道峰值,并以读出时钟VA_Clkb,将各通道峰值模拟信号通过差分管脚Outp/Outn输出。此模式可精确测得各通道电荷量,从而得到通道基线及噪声。

图2 VA64tap2.1内部结构Fig.2 VA64tap2.1 internal architecture.

2 读出电子学系统设计

2.1 硬件设计

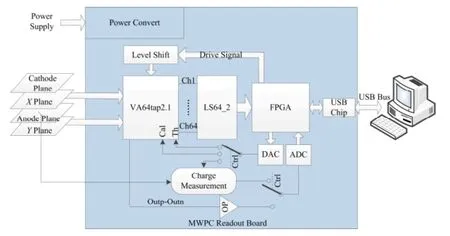

如图3所示,读出板由电荷测量、ASIC、FPGA、电平转换、阈值及刻度信号产生、USB接口等多个模块组成。板上采用Xilinx公司Spartan6系列FPGA (XC6SLX75T)作为各芯片的控制和数据处理器,并以主串方式配置一片EEPROM (XCF32P)实现FPGA固件的上电自动加载。探测器位置读出信号通过Samtec接口插件QSH-060-01-L-D-A连接至读出板。由于读出板为数字模拟混合电路,为防止高频数字信号干扰模拟测量,板上使用小磁珠对模拟地平面和数字地平面进行隔离。读出板采用USB2.0通信协议通过USB接口芯片CY7C68013实现与PC的数据通信,获取PC控制信息并发送数据包至PC。采用Linear公司的电压比较器LT1715,实现FPGA控制信号(+3.3V/0V)与ASIC 控制信号(+1.5V/−2V)之间的电平转换。

读出板由±6V (DC)外部电源模块供电,经板上电源变换后供给各芯片。正常工作时,整个读出板正压电流180mA,负压电流80mA,总功耗小于1.6W。VA64tap2.1的−2 V/+1.5 V电源电流分别为7.5mA和2.5mA,单通道功耗小于0.3mW。

阈值及刻度信号产生模块利用FPGA控制模数转换(Digital to Analog Converter, DAC)芯片AD5323,产生刻度或阈值信号(−2.048–+2.048V),完成正常模式下VA64tap2.1的阈值设定及测试模式下的通道刻度。

探测器阳极信号由阳极高压线经交流耦合后获得,为防止过大信号对测量通道造成损坏,在信号与地之间加双向二极管BAV99限压,并加10Ω电阻限流。电荷测量模块采用电荷灵敏积分前放、CR-(RC)3成形电路对探测器阳极电荷信号积分成形,成形后的信号为宽度1μs的准高斯波形,其顶部平坦、后沿较窄的特点有助于提高寻峰精度[6]。处理后的信号通过10bit模数转换(Analog to Digital Converter, ADC)芯片AD9215以60MHz 频率采样数字化,并送FPGA测量阳极电荷。

图3 读出电子学系统示意图Fig.3 Schematic diagram of readout electronics system.

2.2 软件设计

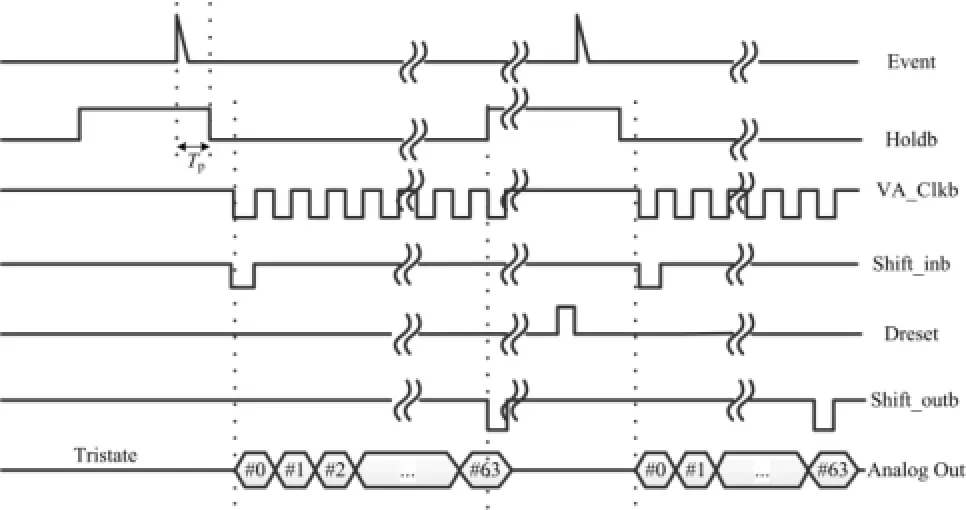

读出系统的软件包含FPGA固件程序及PC端应用程序。FPGA固件程序使用Verilog HDL硬件描述语言在Xilinx ISE环境下综合实现。系统工作时,FPGA首先通过USB总线接收PC命令,对读出板工作模式进行配置。系统工作于正常模式时,PC发送设定的阈值到FPGA,FPGA控制DAC产生阈值并送VA64tap2.1。同时,电荷测量电路接通探测器阳极信号。有效事例到达时,VA64tap2.1的过阈触发信号和处理后的探测器阳极信号送FPGA获取电荷量及位置信息,并生成事例数据包。数据包之间通过添加时间标签对不同事例加以区分。通过USB2.0总线发送数据包至PC端即时处理并显示。测试模式时,系统接收PC命令选择被测通道,FPGA控制DAC产生可调的测试信号送该通道进行测试。图4为VA64tap2.1的测试时序,模拟事例出现后,FPGA产生holdb(宽度大于电荷积分时间Tp),对各通道信号进行峰值保持。随后产生读出使能信号shift_inb和读出时钟信号VA_Clkb,将各通道峰值串行读出。读出的峰值经ADC数字化后送FPGA处理并打包输出。VA64tap2.1串行读出的频率设置为1MHz,64通道总读出时间为64μs。

图4 VA64tap2.1芯片读出时序图Fig.4 Timing diagram for readout of the VA64tap2.1 chip.

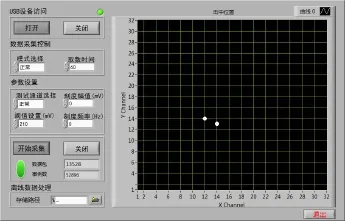

图5 为PC端应用程序,该程序由LabVIEW与C语言混合编程实现。它具有界面友好、操作简单、响应速度快等特点。利用该应用程序我们可以配置读出板工作方式,读出板上数据并在线显示。

图5 PC端应用程序界面Fig.5 Interface of PC application software.

3 读出电子学系统测试

3.1 线性测试

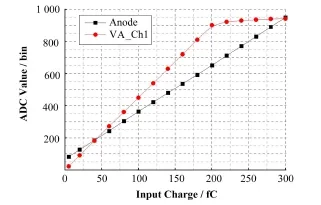

为测得VA64tap2.1及电荷测量模块的电荷积分线性程度,被测通道的注入电荷由DAC产生一个前后沿较窄的脉冲信号串联一个小的交流耦合电容获得,注入电荷量为脉冲幅值与交流耦合电容的乘积。我们选用1pF交流耦合电容,通过改变DAC产生的脉冲信号幅度来改变注入电荷量,在0–300mV之间均匀设置测试点,测得VA64tap2.1通道1(以下简称Ch1)和电荷测量模块的线性度如图6所示。VA64tap2.1在0–200 fC之间积分线性误差(Integral Linearity Error, INL)好于1.5%,电荷测量模块在0–300 fC之间INL好于1.0%。

图6 电荷测量通道线性曲线Fig.6 Linearity curve of charge measurement channel.

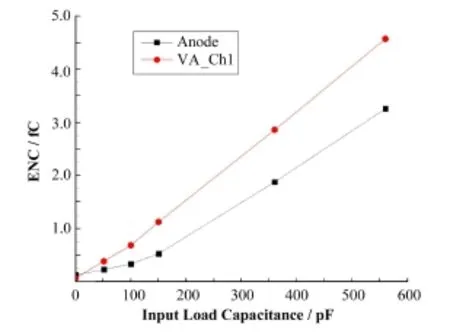

3.2 等效噪声电荷测试

分别在Ch1和电荷测量模块的输入端与地之间接不同电容(0–560pF),测得输入端等效噪声电荷(Equivalent Noise Charge, ENC)如图7所示。输入电容小于100pF时,VA64tap2.1约为38 e·(pF)−1,电荷测量模块约为13 e·(pF)−1;输入电容在100–560pF时,VA64tap2.1约为53 e·(pF)−1,电荷测量模块约为40 e·(pF)−1。

图7 等效噪声电荷线性曲线Fig.7 Linearity curve of ENC.

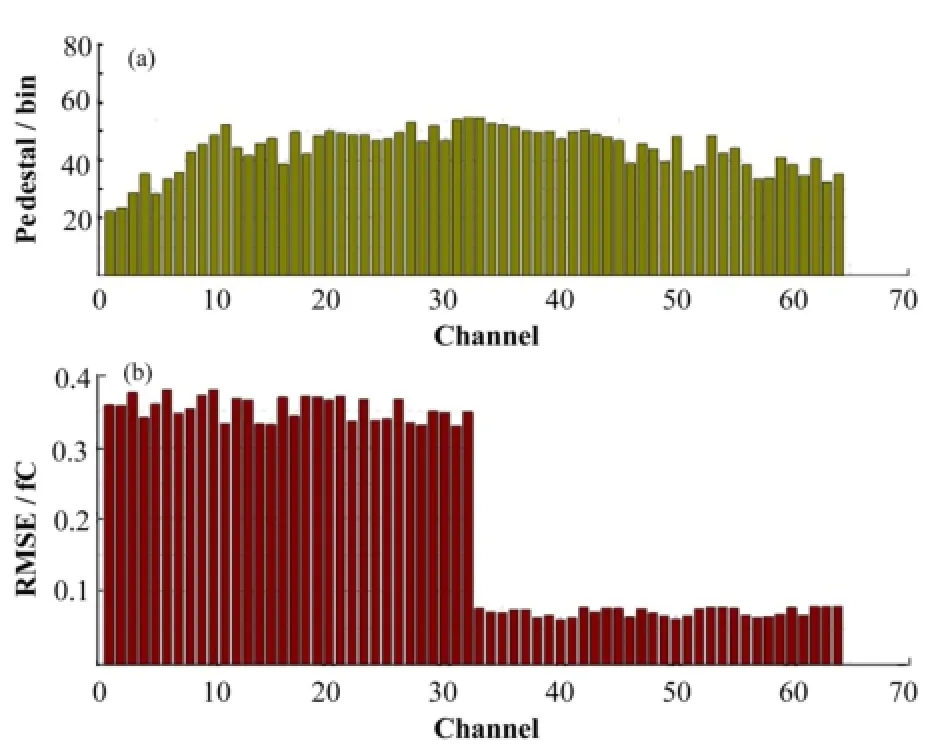

3.3 基线及噪声测试

在探测器未加高压条件下,将其64路位置读出信号通过Cal分别送各通道进行基线测试,结果如图8。64通道的基线介于4–12 fC之间;探测器加高压未加放射源,将其32路位置读出信号通过Cal管脚分别接VA64tap2.1的1–32号通道,剩余32通道悬空,对探测器噪声进行测试。

结果表明,接探测器通道与悬空通道噪声典型值——均方根误差(Root Mean Squared Error, RMSE)分别为0.35 fC和0.07 fC,接探测器通道有较高噪声是由探测器漏电流和分布电容引起。

图8 基线(a)和噪声(b)测试Fig.8 Baseline (a) and noise (b) test.

3.4 X射线过阈信号分布测试

由于没有合适的中子源,实验室采用55Fe放射源产生X射线来测试探测器样机和读出电子学系统。分别取X和Y方向读出丝各32根。放射源经直径200μm的小孔准直后,调整位置至被测读出丝正上方。配置读出电子学工作于正常模式,设置不同阈值各读出60s,对X方向32通道过阈信号的计数结果如图9所示。在不低于噪声基线条件下,过阈信号在各通道上成高斯分布,且阈值较小时计数率较高。

图9 不同阈值下信号过阈分布(a) 210 mV,(b) 280 mVFig.9 Distribution of signal over different thresholds.(a) 210 mV, (b) 280 mV

4 结语

本电子学读出系统采用ASIC芯片,实现了MWPC探测器的二维位置读出。系统通过测量阳极电荷量剔除γ射线的影响,通过调节阈值来获得理想的计数率。硬件设计采用8层板结构,具有占用空间小(可方便挂载至探测器上)、升级更新方便和成本低廉等优点。现有条件下的测试结果表明该系统可正常工作,功能和性能上满足设计预期。为达到工程需求,拟采用光纤方式与上位机连接,以提高数据收发速度。另外,将对电荷及位置的测量模块做进一步优化以提高其性能。

1 张杰. 中国散裂中子源(CSNS)—多学科应用的大科学平台[J]. 中国科学院院刊, 2006, 21(5): 415–417

ZHANG Jie. China Spallation Neutron Source (CSNS)-big science platform for multidisciplinary applications[J]. Bulletin of Chinese Academy of Sciences, 2006, 21(5): 415–417

2 孙志嘉, 杨桂安, 许虹, 等. CSNS谱仪-中子探测器初步设计[C]. 全国核电子学与核探测技术学术年会, 2010

SUN Zhijia, YANG Guian, XU Hong, et al. Preliminary design of the neutron detectors for the instruments of CSNS[C]. The National Nuclear Electronics & Detection Technology Annual Meeting, 2010

3 王小胡, 朱启明, 陈元柏, 等. 一个二维读出多丝正比室的实验研究[J]. 核电子学与探测技术, 2009, 29(4): 756–759

WANG Xiaohu, ZHU Qiming, CHEN Yuanbo, et al. Experimental study of a two-dimensional MWPC[J]. Nuclear Electronics & Detection Technology, 2009, 29(4): 756–759

4 Gamma Medica-Ideas. VA64TAP2.1 documentation (V0R7)[P]. Norway, 2006

5 Gamma Medica-Ideas. LS64_2 documentation (V0R3)[P]. Norway, 2005

6 邹敏. CSNS3He管读出电子学系统的研制[M]. 北京:中国科学院高能物理研究所, 2012

ZOU Min. The research of the3He tube readout electronic system in CSNS[M]. Beijing: Institute of High Energy Physics, Chinese Academy of Sciences, 2012

CLC TL82, TN41

Electronic readout system for MWPC detector used in CSNS

REN Hailong1,2ZHAO Yubin2WEN Shuangchun1LU Ruiqi1,2

1(The Physics and Micro Electronic College of Hunan University, Changsha 410082, China)

2(Dongguan Institute of Neutron Science, Dongguan 523808, China)

Background: China Spallation Neutron Source (CSNS) is a scientific facility used for studying neutron characteristics and detecting the micro structure of materials. Purpose: This study aims to obtain the position and charge information of incident neutrons for the multipurpose reflectometer of CSNS. Methods: An electronic readout system is designed to detect and handle the signals from a two-dimensional Multi-Wire Proportional Chamber (MWPC). An Application Specific Integrated Circuit (ASIC) chip VA64tap2.1, made by IDEAS company, is applied to get the position and charge information in MWPC. The readout system is comprised of a VA64tap2.1-based readout board, a firmware for Field-Programmable Gate Array (FPGA) and an application program in PC. Results: The tests results show that the system can fulfill the readout requirements, and the ASIC chip is of low noise (less than 0.35fC when connected the MWPC detector), low power dissipation (less than 0.3 mW per channel), large dynamic range (−200‒+160fC) and high integration (64 channels/board). Conclusion: This electronic readout system can be used in particle position detection.

MWPC, CSNS, ASIC, Charge measurement, FPGA

TL82,TN41

10.11889/j.0253-3219.2015.hjs.38.050402

中国散裂中子源工程(发改高技(2008)2578号)资助

任海龙,男,1988年出生,2011年毕业于太原科技大学,现为硕士研究生,主要从事FPGA逻辑开发及单板硬件设计

赵豫斌,E-mail: zhaoyb@ihep.ac.cn

2014-12-17,

2015-03-22