OMAP-L138 DSP与FPGA通信方案设计

张伟文,高伟强,林 淦,刘建群,阎秋生

(广东工业大学机电工程学院,广东广州 510006)

OMAP-L138 DSP与FPGA通信方案设计

张伟文,高伟强,林 淦,刘建群,阎秋生

(广东工业大学机电工程学院,广东广州 510006)

针对双刀头高性能柔性材料切割数控系统,结合OMAP-L138+FPGA控制系统的数据传送需求以及平台资源,提出一种OMAP-L138的DSP通过EMIFA接口与FPGA的FIFO进行数据通信的设计方案,DSP将处理后的数据通过EMIFA接口传送到FPGA的异步缓存FIFO模块。FIFO在接收DSP发送的高速数据的同时,将缓存的数据输出。通过逻辑分析仪实验测试验证,该方案能够实现数据的正确通信。

OMAP-L138;FPGA;EMIFA;FIFO;异步缓存

0 引言

OMAP-L138是美国TI公司生产的基于达芬奇(DaVinci)技术的ARM+DSP双核处理器,具有ARM926EJ-S和C674X高速浮点DPS两个异构内核,采用OMAP-L138+FPGA双芯片构建数控系统的硬件平台,能够满足高性能数控系统对界面层、控制层和设备层开发的要求。异构多核结构系统中,各处理器之间的实时通信将直接影响整个控制系统的性能及可靠性,其中ARM与DSP的通信通过共享内存方式进行数据交互,而DSP与FPGA常用的通信接口主要有总线型接口、存储型接口、串口型接口、主机型接口和特殊接口。其中总线接口开发难度较大,需要协议支持;串口接口开发简单,但是速率较慢;特殊接口不具备通用性,需要修改DSP驱动,开发周期长。

根据OMAP-L138+FPGA控制系统对数据传输量的需求及控制以及平台的资源,选择EMIF接口作为DSP与FPGA之间的通信接口方案。由于FP⁃GA开发端并没有EMIF总线接口,需要进行编程完成接口功能。通常情况下采用FPGA的双端口RAM或者FIFO来协调实现[1-3]。因此,本文针对双刀头高性能柔性材料切割系统的需求,采用OMAP-L138+FPGA双芯片设计了数控系统硬件平台,提出一种OMAP-L138 DSP通过EMIFA接口与FPGA的FIFO进行数据通信的设计方案,实现了DSP与FPGA的高速实时通信。

1 OMAP-L138+FPGA数控系统硬件平台设计

本文研究的柔性材料切割系统要求有两个数控切割刀头,分别控制两组X-Y-C轴和Z轴4轴刀头运动切割皮革、布料等柔性材料。其中C轴是导向控制轴,用于刀刃方向对X-Y轮廓的跟随控制。该系统是8轴进给,双3轴联动运动控制系统。因此,硬件系统不但要有强大的插补运算能力,还有设备驱动的扩展要求。

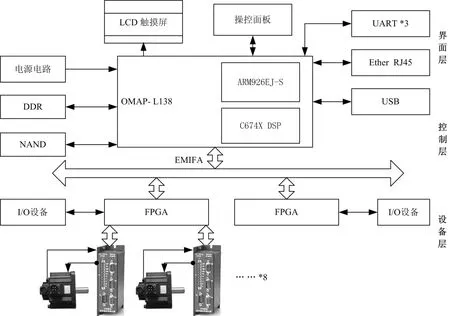

根据要求,硬件系统由OMAP-L138和Cy⁃clone II FPGA组成(如图1所示)。系统划分为界面层、控制层和设备层三部分。界面层由ARM内核基于Linux操作系统开发,主要提供人机操控界面、数控程序管理、文件服务、上位机通讯和系统维护等功能。控制层在DPS内核基于DPS/BIOS实时操作系统开发,主要完成数控轨迹前瞻、运动加减速规划、双三联动插补、刀向跟随运动、双刀头干涉避让、刀尖Z向补偿等控制与计算。设备层由FPGA实现,主要实现对伺服驱动的数字/脉冲转换控制,并提供各种I/O信号的处理功能。

图1 8轴OMAP-L138+FPGA柔性材料切割数控系统结构

2 DSP的EMIF(外部存储器接口)介绍和硬件接口设计

2.1 OMAP-L138 DSP硬件接口EMIFA介绍

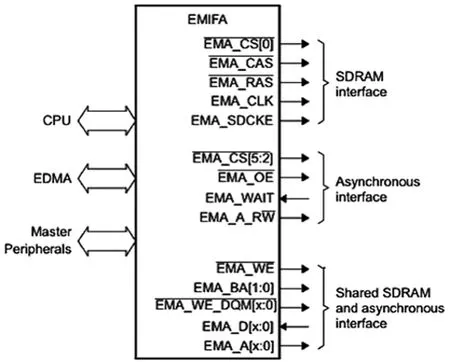

EMIFA是外部存储器件和OMAP-L138 DSP的接口,提供64 bit宽度的外部总数据接口,也可以作为32 bit宽度使用;共支持4个大小32 M异步外部存储器,可以通过配置外接不同类型的存储设备,包括同步突发静态 RAM(SB⁃SRAM)、同步动态RAM(SDRAM)、各种异步设备(SRAM、ROM和FIFO)以及同步FIFO[4]。图2为OMAP-L138 DSP EMIFA接口的功能模块图。

图2 OMAP-L138 DSP的EMIFA接口功能模块

2.2 FPGA与EMIFA的硬件接口及读写时序

如图3所示为FPGA与EMIFA的硬件接口连接图。OMAP-L138 DSP的EMIFA与FIFO通信数据为16位,选取片选空间/EMA_CS[4]。其中,FP⁃GA工作时钟为EMIFA工作时钟(EMA_CLK, 100 MHz),/EMA_WE为DSP往FPGA写入数据的判别信号,/EMA_OE为DSP读取FPGA数据的判别信号。

图3 FPGA和DSP之间的接口连接图

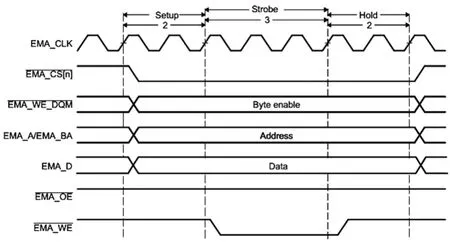

如图4所示为FPGA与EMIFA的接口写时序图,从中可以看出,DSP往FPGA写入数据需要三个步骤:建立(Setup)、写入(Strobe)和保持(Hold)。同时,把单个数据所占时长设计为7个主时钟周期,前2个时钟周期设为建立时间,/EMA_WE从第3个时钟周期开始置低并保持3个周期长度,这样就保证了有充足的时间用于数据写入准备。在/EMA_WE的两次写入低电平之间需保证2个时钟周期以上的时间用于数据保持。FPGA就在这个时刻进行数据采样,完成数据的传输。

图4 EMIFA与FPGA的FIFO的接口写时序图

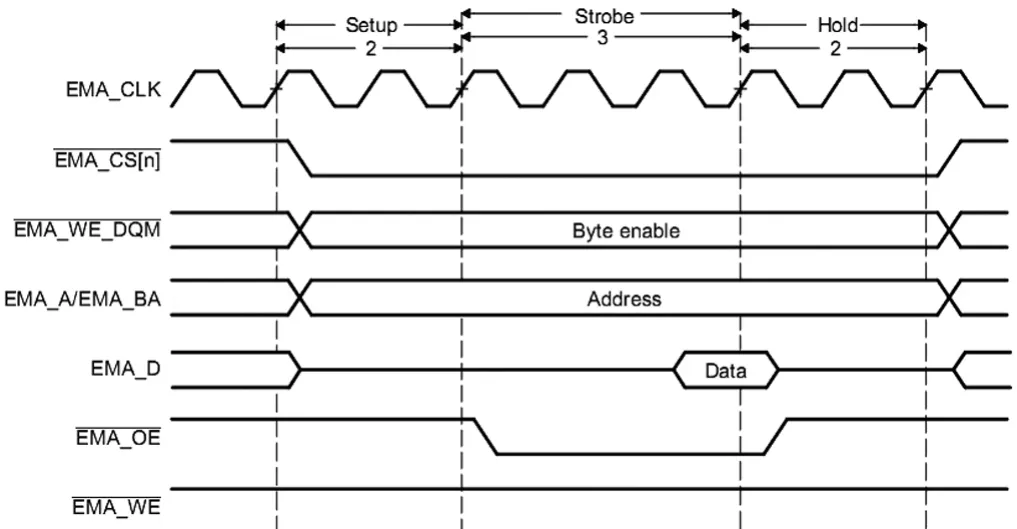

如图5所示为FPGA与EMIFA的接口读时序图。与写时序一样,DSP读取FPGA数据同样需要三个步骤:建立(Setup)、写入(Strobe)和保持(Hold),各个阶段所占时长与写时序一致。本次设计DSP读取的FPGA数据为FIFO的数据存储个数,在/EMA_OE为低电平时完成数据的读取。

图5 EMIFA与FPGA的接口读时序图

3 FPGA异步缓存FIFO模块设计

FIFO(First In First Out)是一种先进先出的数据缓存器,而异步FIFO是用一种时钟写入数据,用另一种时钟读出数据[5]。本次设计中,FPGA选用Cyclone II系列的EP2C8,FIFO深度为4 M。如图6所示,为异步缓存模块设计框图。其中,clk为FPGA工作时钟 (CLK,100 MHz),rdclk为clk通过分频模块得到的时钟,大小为4 kHz。

图6 异步缓存模块设计框图

3.1 读写请求的产生

(1)基于字面匹配的语义相似度计算方法。比较典型的有基于LCS[8]、TF-IDF[9]的语义相似度计算方法。基于LCS的语义相似度计算方法是利用2个文本中词语的最大公共子串的长度来计算文本之间的相似度;基于TF-IDF的语义相似度计算方法是将文本建模成词频向量,运用余弦相似度来衡量文本之间的相似度。这类方法的优点是计算速度快、工作量小,缺点是忽略了词语的语义信息,需要人工设定停用词表。

根据FPGA与DSP EMIFA接口的写时序图(如图4所示),DSP往FPGA写入单个脉冲数据时,/EMA_CS[4]拉低并持续7个写时钟周期,/ EMA_WE拉低并持续3个写时钟周期。而FIFO在写时钟的上升沿检测到写请求(wrreq)为高电平时,写入一次数据。因此,为了避免FIFO重复写入同一脉冲数据,写请求应该在每一个/EMA_WE信号的下降沿产生(有效,即置高),并持续一个写时钟周期。写请求产生模块如图7所示,其中clk配置外接DSP的EMA_CLK引脚,awe_n外接/ EMA_WE,wrreq为写请求。

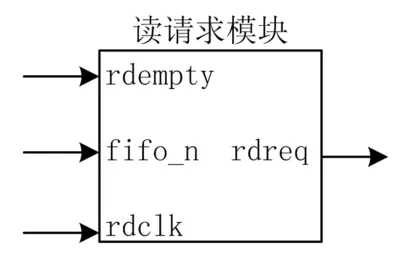

FIFO读出数据和写入数据原理一致,在读时钟的上升沿检测到读请求(rdreq)为高电平时,读出一个数据。本次设计中,读时钟频率设置为4 kHZ。FIFO在读时钟下读出的每个数据持续时间为250μs,因此,FIFO在读出第一个数据开始,读请求信号(rdreq)应该一直有效、置高。为了保证数据的连续性,读请求信号(rddreq)在FIFO的存储个数大于等于4个,直到rdempty为高电平时置低。图8为读请求产生模块,其中,rdclk接由clk通过分频模块产生的时钟信号,rdempty和fifo_n分别接FIFO的rdempty信号和wrusedsw信号。

图7 写请求产生模块

图8 读请求产生模块

3.2 DSP读取FPGA的FIFO存储个数

本次设计中FIFO存储容量(深度)设置为4 M,由于DSP往FPGA的FIFO写入数据的速度远远高于FIFO读出数据的速度,势必会造成FIFO存储数据的溢出。为了避免数据溢出造成的数据丢失和紊乱,DSP在每次通信中应该先查询FPGA的FIFO的存储数据个数。若存储个数低于上限值,DSP继续往FPGA传送数据;否则,DSP停止往FPGA传送数据。本次设计中,设置允许DSP往FPGA传送数据的上限为200个,即50组脉冲数据包。

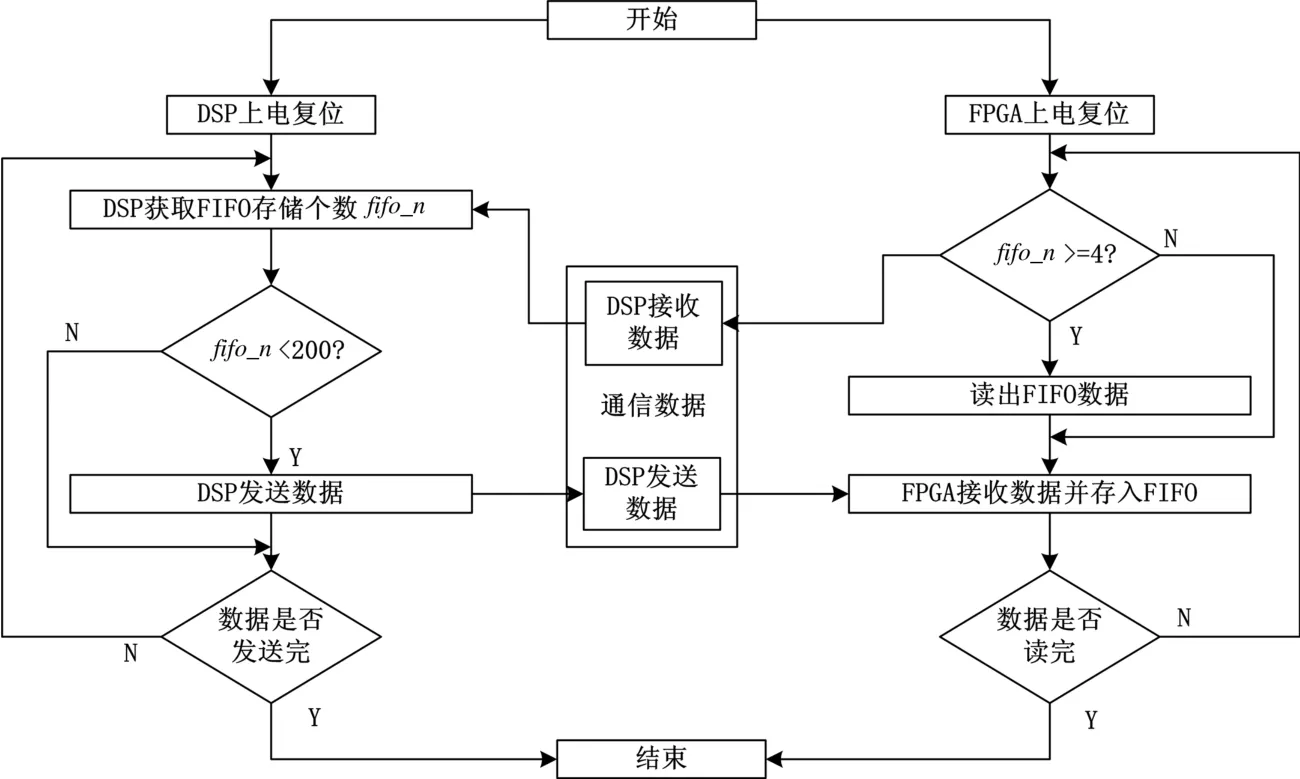

4 接口实现流程

DSP和FPGA开始工作时,上电复位。在DSP与FPGA的通信过程中,DSP在每次通信前,先获取FPGA的FIFO存储个数fifo_n。当fifo_n小于规定的上限值(本次设计设置为200)时,DSP发送一次数据包。如此循环,直到数据发送完毕,最后停止通信。

FPGA在两者通信过程中处于从属状态,当DSP需要读取FIFO存储个数fifo_n时,FPGA只需把fifo_n赋值给通信数据DATA;当DSP发送数据包时,FPGA将接收的数据依次写入FIFO中。与此同时,当FIFO存储数据的个数超过4个时,开始读出数据,直到FIFO为空。图9为接口实现程序流程图。

图9 程序流程图

5 EMIFA配置程序及实验验证

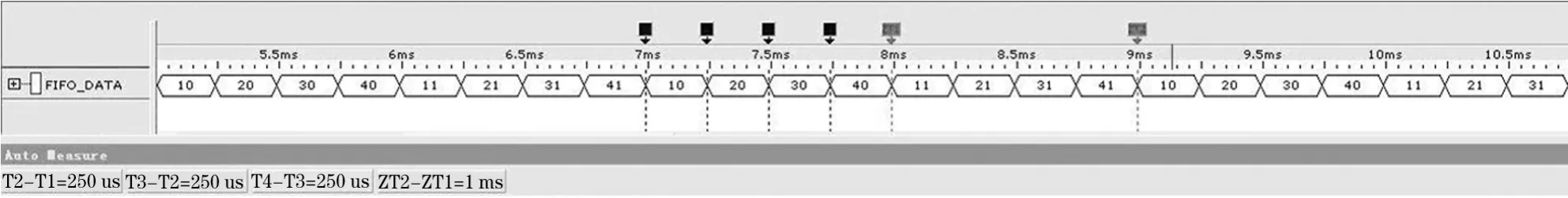

如图10所示,为基于OMAP-L138和FPGA的异构双核嵌入式系统测试板。DSP接口软件设计主要是通过TI公司的集成开发环境CCS3.3软件,利用支持库文件对EMIFA相关寄存器进行配置。本次设计为了便于实验分析验证,EMIFA配置程序主要实现了DSP往FPGA的FIFO中重复写入10、20、30、40、11、21、31、41数据。

图10 控制平台测试板

6 结论

经过逻辑分析仪实验验证分析,能够实现正确符合设计要求的数据通信。将本次设计完成的OMAP-L138与FPGA之间的通信方案应用到柔性材料数控系统中,OMAP-L138将进行了插补运算后的数据通过该方案传输给FPGA,再由FPGA进行数据脉冲转换输出同步脉冲驱动8轴实现双刀头3轴联动插补控制。运用了该方案的双刀头高性能柔性材料切割系统已开发完毕,并投入到生产线上,已于深圳某鞋业公司稳定运行生产,获得了预期效果。因此,本次基于异步缓存FIFO的DSP EMIFA与 FPGA的通信方案能够实现OMAMP-L138与FPGA的正确通信。

图11 逻辑分析仪测试结果

[1]李乐.DSP+FPGA折反射全景视频处理系统中双核高速数据通信[J].电子与信息学报,2010,32(3):649-654.

[2]胡彬,陈涛.TMS320C6713DSPEMIF接口与FPGA双口RAM接口设计[J].测试测量技术,2008(10):32-35.

[3]任勇屹,张祺,韦忠正.一种FPGA和TMS320DM642的通信方案[J].计算机应用与软件,2013,30(7):298-300.

[4]Texas Instruments.External Memory Interface A(EMI⁃FA)[R].December 2011.

[5]胡波,李鹏.异步FIFO在FPGA与DSP通信中的运用[J].电子科技,2011,24(3):53-61.

(编辑:向 飞)

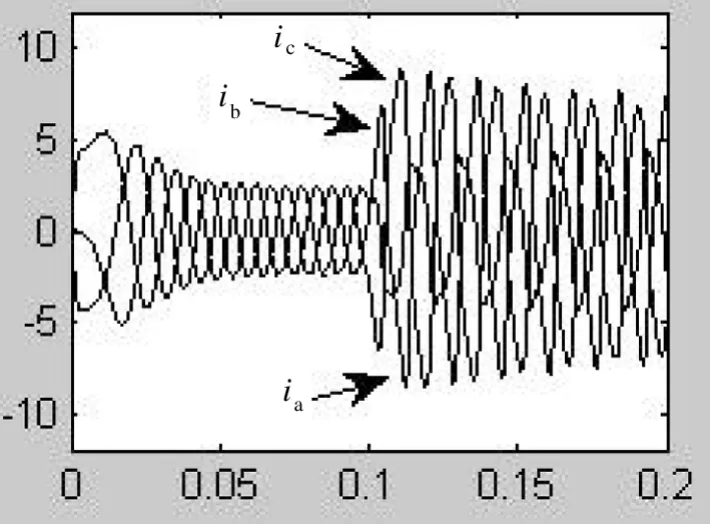

图9 T1和T2同时在t=0.1 s故障时MLD模型中三相电流

图10 T1和T2同时在t=0.1 s故障时三相电流残差

参考文献:

[1]崔博文,任章,陈剑,等.逆变器供电的电动机变频调速系统实时故障检测[J].电机与控制学报,2006(01):54-56.

[2]崔博文,任章,陈剑,等.逆变器供电的感应电机驱动系统故障仿真研究[J].电机与控制学报,2007,11(1):578-583.

[3]仇志凌.基于LCL滤波器的三相三线并网变流器若干关键技术研究[D].杭州:浙江大学,2009.

[4]安群涛.三相电机驱动系统中逆变器障诊断与容错控制策略研究[D].哈尔滨:哈尔滨工业大学,2011.

第一作者简介:罗 凯,男,1986年生,江西南昌人,硕士研究生。研究领域:船舶电力推进及其控制。

Design on Communication between OMAP-L138 DSP and FPGA

ZHANG Wei-wen,GAO Wei-qiang,LIN Gan,LIU Jian-qun,YAN Qiu-sheng

(School of Electromechanical Engineering,Guangdong University of Technology,Guangzhou510006,China)

A data communication design between OMAP-L138 DSP and FPGA FIFO is proposed with the data transfer requirement of OMAPL138+FPGA control system and the platform resources for High performance flexible materials pole head CNC cutting system.DSP transmits the processed data to FPGA via the asynchronous FIFO with EMIFA interface.And the FIFO receivers the high-speed data from DSP,while outputting data from the asynchronous FIFO.The design is verified to achieve the correct communication with the laboratory tests by logic analyzer.

OMAP-L138;FPGA;EMIFA;FIFO;asynchronous cache

TP273

B

1009-9492(2015)10-0115-05

10.3969/j.issn.1009-9492.2015.10.029

张伟文,男,1989年生,广东汕尾人,硕士研究生。研究领域:数控技术。

崔博文,男,1966年生,博士,教授。研究领域:电力电子技术、电力电子系统故障诊断技术。

(编辑:向 飞)

2015-04-15