基于NiosⅡ的多路高速数据采集存储系统的实现

祝 宇,王连明,艾淑平

(1.东北师范大学物理学院,长春130024;2.吉林建筑大学基础科学部,长春130118)

基于NiosⅡ的多路高速数据采集存储系统的实现

祝 宇1,王连明1,艾淑平2

(1.东北师范大学物理学院,长春130024;2.吉林建筑大学基础科学部,长春130118)

为了解决多路高速数据的采集与存储问题,提出基于FPGA(Field Programmable Gate Array)和NiosⅡ软核技术的设计实现方法。将采集的数据和FPGA的配置数据共享配置存储器空间,可以节省额外的存储器件,降低系统成本。实验中以EP2C35F672C8为控制核心、AD7980为模数转换器、EPCS64为存储介质,实现了15路模拟信号的完全并行采集。该系统可实现对多路ADC(Analog-to-Digital Converter)的并行控制,从而实现多路信号的并行高速采集。由于采用了软核技术,使系统具有很高的灵活性和可扩展性。实验结果表明,此设计为要求成本低、系统升级频繁的工程提供了新的思路。

NiosⅡ控制器;现场可编程门阵列;多路数据采集;高速;并行;串行存贮器

0 引 言

数据采集存储是数字信号处理系统中的重要环节,而多路高速数据采集存储是高性能数字信号处理系统的关键技术,在雷达信号处理、多传感器数据融合、声学检测与成像等军事和工业领域具有广泛的应用。

目前,实现多路信号高速采集的方法主要有基于微处理器的多路分时切换采集[1-3]、FPGA(Field Programmable Gate Array)和外部微处理器联合的并行采集[4,5]。前者由于软件代码是顺序执行的,不能进行多路数据的并行采集,大大降低了系统的工作效率。后者一般利用FPGA实现数据采集控制,外部MCU(Micro Control Unit)作为数据传输与存储控制核心,系统复杂且成本高[6]。文献[7]中高速数据采集的控制核心也是FPGA,但未使用其可定制软核功能,降低了系统的灵活性。虽然数据同步采集,但数据传入FPGA是顺次选通完成的,所以系统中8路模拟信号的采集并不是完全并行[7]。

NiosⅡ是Altera公司开发的一款32位精简指令集软核处理器,采用软核技术的优势在于,用户可以根据系统需求在SOPC Builder环境下,将NiosⅡ与系统预定义或用户自定义的外围设备软核相连接,生成一个完全匹配用户需求的微处理器应用系统,并在FPGA中实现[8]。同时软核技术的应用,可以解决某一接口部件需求量大时,商用化处理器无法提供的问题,如需要多路PIO、多路定时器等。采用FPGA实现系统,可将有高速需求的部件用硬件实现[9],并生成自定义软核且与NiosⅡ处理器相连[10],从而解决高速问题。

笔者采用基于FPGA的NiosⅡ软核技术进行高速并行系统的设计,既可满足系统多路高速、并行采集的需求,又具有开发周期短、设计灵活、升级容易、节约成本的优点。

1 系统整体架构

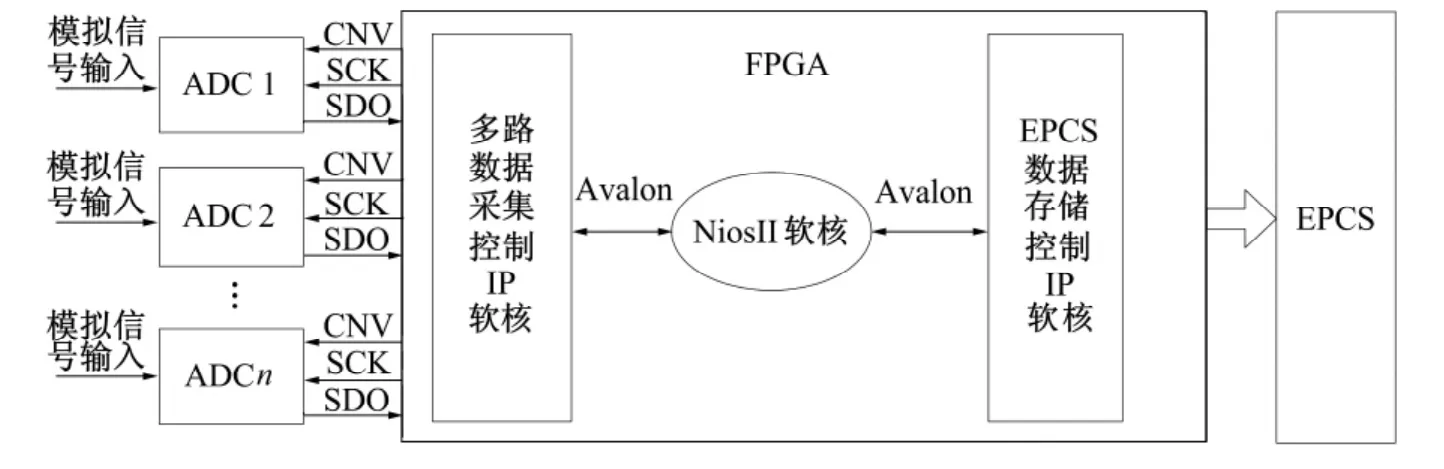

多路数据采集存储系统主要由3部分构成:多路数据采集控制模块、NiosⅡ控制器和EPCS数据存储控制模块。系统结构如图1所示。

图1 系统结构图Fig.1 System structure diagram

系统的工作过程:在NiosⅡ软核控制器的协调控制下,多路数据采集控制IP软核同步产生n组ADC(Analog-to-Digital Converter)的控制信号,与此同时同步接收n路ADC的串行数据,EPCS数据存储控制IP软核将数据存储在外部EPCS中。FPGA内部逻辑配置数据、NiosⅡ程序映象和采集的数据一起共享EPCS存储空间。

2 FPGA数据采集控制原理

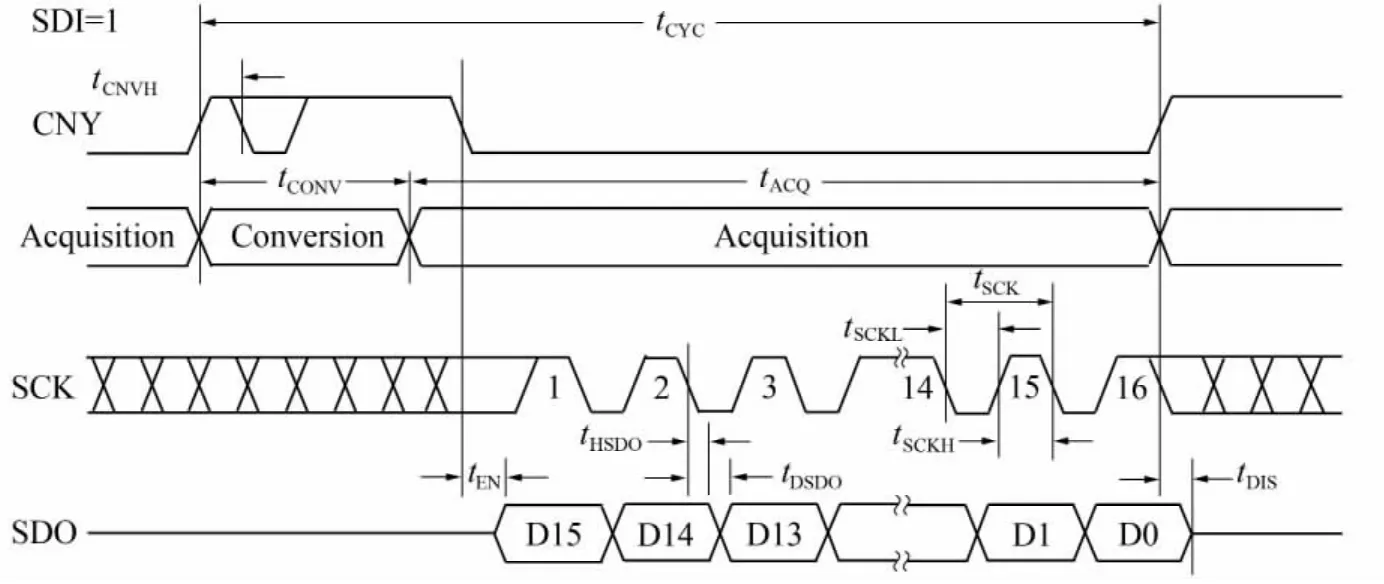

系统中的ADC选择AD公司的AD7980,它是16位逐次逼近型、低功耗、高速AD转换芯片,其最大数据吞吐量为1MSPS(Million Samples Per Second)[11]。AD7980有多种工作模式,设计中采用的模式为片选模式之三线无繁忙指示(mode 3-wire no busy indicator)。其时序如图2所示。

图2 CSmode 3-wire no busy indicator模式时序图Fig.2 mode 3-wire no busy indicatormode timing

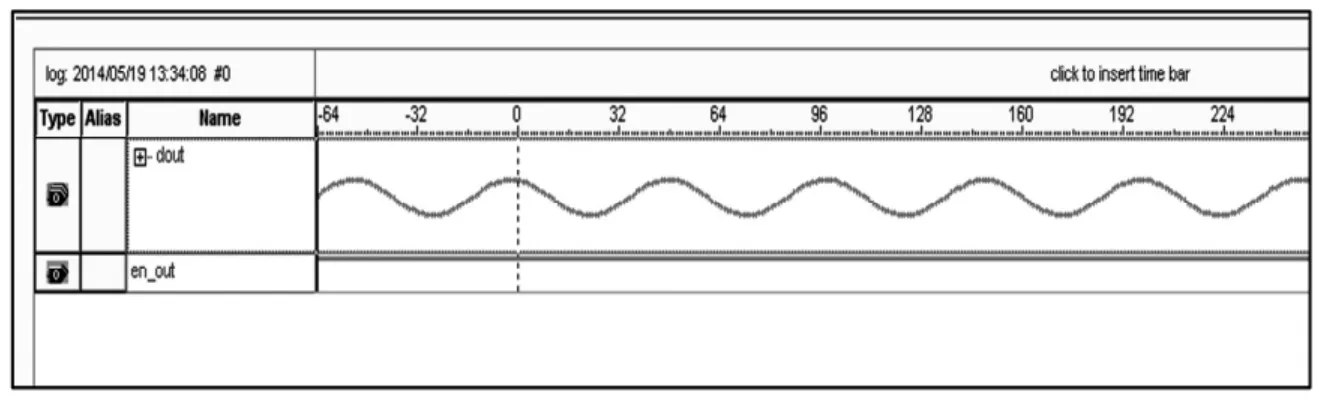

这款ADC芯片的主要控制及数据引脚分别是:SDI(Serial Data Input)串行数据输入、CNV(Convert Input)转换输入、SCK(Serial Data Clock Input)串行数据时钟输入、SDO(Serial Data Output)串行数据输出。一个工作周期包含转换期Conversion和获取期Acquisition。首先SDI引脚置高电平,使芯片工作在CS模式;然后CNV上升沿启动转换期,保持高电平直到最大转换时间,使SDO引脚无繁忙指示(no busy indicator)后,再拉低CNV;最后进入获取期,从CNV信号下降沿开始,伴随串行时钟SCK每个下降沿,即可从SDO端口顺利读出转换完成的串行数据,数据的高位最先输出。这样ADC芯片就对模拟信号完成了一次采集转换。为了验证AD采集数据的正确性,采样外部输入正弦信号,并用SignalTap抓取内部结果dout(见图3)。

图3 SignalTap抓取AD采集到的正弦信号图Fig.3 Sine wave acquired by ADC captured by signalTap

同时采集多路数据时采集到的数据和真实信号有误差,似乎受到了干扰。原因是FPGA的输出控制信号驱动能力有限,所以在AD和FPGA之间再增加一级驱动即可。

为了同时采集n路模拟电压信号,需要n路AD转换芯片同时工作,所以系统需要同时提供n路转换信号CNV,n路串行数据时钟信号SCK和n路串行数据接收SDO。利用一般微控制器实现多路信号的并行控制与接收几乎是不可能的,因为计算机编程语言都是顺序执行,而且引脚数量有限。SOPC (System On a Programmable Chip)技术是所有嵌入式系统设计的有机结合[12]。而采用基于FPGA的SOPC技术,可通过自定义数据采集控制IP(Intellectual Property)软核,实现对每个ADC的单独并行控制; FPGA的丰富IO资源,也能满足系统大量的引脚需求。

系统中设计了多路数据采集控制IP软核,同时实现对n路ADC的并行采集控制与数据传输。理论上,只要FPGA资源充足,即可实现任意多路的并行采集。将数据采集控制部分打包成自定义组件IP,通过Avalon总线挂在NiosⅡ软核上。Avalon交换结构可使NiosⅡ主控制器轻松调用自定义数据采集控制IP软核,极大地提高了系统的灵活性和扩展性。使用NiosⅡ软核作为主控制器,既节省了外部MCU,又降低了系统成本。

3 利用EPCS进行数据存储

3.1 外部配置存储器EPCS

通常情况下,EPCS作为外部配置存储器,负责配置FPGA内部逻辑和NiosⅡ程序。FPGA内部逻辑的配置数据可通过AS方式下载到EPCS中,然后由EPCS将配置数据配置到FPGA中以形成硬件电路。EPCS是非易失性存储介质,即使FPGA掉电,之前的配置数据也依然存在。而NiosⅡ处理器通过boot loader从EPCS中将要在其内部运行的程序映象拷贝到DDR2里,即DDR2作为Nios程序运行的空间。所以在定制CPU时,复位地址选择EPCS,异常地址选择DDR2[13]。

一般情况下,EPCS中除了存储配置数据和程序映象外,还剩余很多存储空间。利用这部分空间存储采集数据,可节省额外的非易失性存储器件,减小系统尺寸,降低系统成本。EPCS芯片存储空间分配如图4所示。

图4 EPCS存储空间分配Fig.4 Distribution of stored space in EPCS

3.2 EPCS存储数据

EPCS是Flash存储器的一种,对Flash存储器的一切操作同样适用于EPCS。

Flash存储器的基本单元有页、区或块。对于不同类型的Flash,其操作的最小单元也不同。对于EPCS的操作,Altera公司的HAL提供了两大类操作:简单Flash访问(Simple Flash Access);细粒度Flash访问(Fine-Grained Flash Access)。不管是哪种访问方式,EPCS的基本读写数据长度都是一个字节[14]。所以,一个16 bit的数据需要拆分成两个字节进行存储。

1)简单Flash访问。该访问方式如果两次写的数据在一个区里,则后一次的写入会先擦除前一次的写入,使该区只保留最近一次写入的数据,而该区的其他空间都是0xFF。

具体涉及的API函数如下

alt_flash_close_dev()

alt_flash_open_dev()

alt_read_flash()

alt_write_flash()

2)细粒度Flash访问。该访问方式可保护前一次的数据。其具体实现方法是:先读取该区的数据;然后连同这次要写入的数据一起写进相应的存储区域。

具体涉及的API函数为

alt_get_flash_info()

alt_erase_flash_block()

alt_write_flash_block()

大多数数据采集存储系统需要连续多次测量并存储数据,根据HAL对Flash两种访问方式的特点,数据存储采用细粒度Flash访问,而数据的读出选择Flash访问。写Flash的具体操作步骤如下

其中fd=alt_flash_open_dev(“/dev/epcs”),是要打开Flash设备EPCS。如果返回值为空,则表示设备没有打开ret_code=alt_write_flash_block(fd,block_addr,addr,data,BUF_SIZE),表示向addr开始的地址空间写BUF_SIZE个数据,data即为要写入的数组数据,而block_addr是Flash块的地址头;如果返回值ret_code为0,则说明写入成功。这条语句在写入数据的同时,不会影响之前写入该块的其他空间数据。alt_flash_close_dev(fd),这条语句执行Flash设备的关闭。

系统设计中,底层使用硬件描述语言VHDL和C语言,上层使用原理图输入方式[15,16]。

4 系统测试

设计中使用的FPGA为Altera公司的CycloneⅡ系列EP2C35F672C8,EPCS为EPCS64,令AD7980工作在最大采样速率,即1 MSPS。经测试,系统可同时控制15路ADC,且每路ADC都可实现1 MSPS;采样存储深度为32 MByte。即该系统可以实现AD芯片的最大采样速率。

系统中使用的FPGA外部晶振频率为50 MHz,通过PLL倍频达到其最大时钟频率1 GHz,就可以对采样速率更高的ADC进行控制。

所以针对不同应用的采样,选择合适的AD转换芯片、FPGA、EPCS,可以轻松扩展采样精度与速率、采集通道数及存储深度。

5 结 语

笔者设计实现了基于NiosⅡ的多路高速数据并行采集存储系统,该方案充分体现了FPGA并行分布式结构、用户定制电路、配置灵活及便于系统升级的优势,为多路数据同时高速采集提供了借鉴。配置数据和采集数据共享EPCS配置芯片,节省了额外的非易失性存储器件。通过将SOPC技术、NiosⅡ软核技术应用于多路高速数据采集存储系统,为成本低、系统升级频繁的工程提供了新思路。

[1]林祝亮,武林,杨金华,等.基于双单片机的多路数据采集系统设计[J].仪器仪表学报,2006,27(6):132-134. LIN Zhuliang,WU Lin,YANG Jinhua,et al.Design of Multi-Channel Data Acquisition System Based on Double MCU[J]. Chinese Journal of Scientific Instrument,2006,27(6):132-134.

[2]陈婷婷,姜余祥,李哲英.基于嵌入式技术的高速数据采集系统[C]∥中国兵工学会第十四届测试技术年会暨中国高等教育学会第二届仪器科学及测控技术年会论文集.北京:中国兵工学会,2009:152-155. CHEN Tingting,JIANG Yuxiang,LIZheying.High Speed Data Acquisition System Based on Embedded Technology[C]∥the 14th Annual Testing Technology Meeting of China Ordnance Society,the 2th Instrument Science and Measurement Technology Conference Proceedings of China Institute of Higher Education.Beijing:China Ordnance Society,2009:152-155.

[3]王静,林君.高速数据采集系统在ATEM中的实现[J].吉林大学学报:信息科学版,2004,22(6):537-540. WANG Jing,LIN Jun.Realization of High Speed Data Collecting System in ATEM[J].Journal of Jilin University: Information Science Edition,2004,22(6):537-540.

[4]梁友良.ARM+FPGA的多路高速AD接口电路设计[D].长春:长春理工大学理学院,2012. LIANG Youliang.Design of High-Speed Multi-Channel and Interface Circuit on ARM and FPGA[D].Changchun:School of Science,Changchun University of Science and Technology,2012.

[5]蔡弘.基于ARM+FPGA的高速信号采集与存储系统设计[D].北京:北京交通大学电子信息工程学院,2007. CAIHong.Design of High-Speed Signal Acquisition and Storage System Based on ARM and FPGA[D].Beijing:School of Electronic and Information Engineering,Beijing Jiaotong University,2007.

[6]沈碧云.小型高速可编程多路数据采集存储系统的研究[D].南京:南京理工大学电子工程与光电技术学院,2013. SHEN Biyun.Research of Small High-Speed Programmable Multi-Channel Data Acquisition and Storage System[D]. Nanjing:School of Elctronic and Optical Engineering,Najing University of Science and Technology,2013.

[7]林长青,孙胜利.基于FPGA的多路高速数据采集系统[J].电测与仪表,2005,42(473):52-54. LIN Changqing,SUN Shengli.Multi-Channel High-Speed Data Acquisition System Based on FPGA[J].Electrical Measurement&Instrumentation,2005,42(473):52-54.

[8]周立功.SOPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2006:3-8. ZHOU Ligong.SOPC Embedded System Basic Tutorial[M].Beijing:Beijing University of Aeronautics and Astronautics Press,2006:3-8.

[9]WANG Xuying,LU Yinghua,ZHANG Likun.Design and Implementation of High-Speed Real-Time Data Acquisition System Based on FPGA[J].The Journal of China Universities of Posts and Telecommunications,2006,13(4):61-66.

[10]李兰英.NIOSⅡ嵌入式软核SOPC设计原理与应用[M].北京:北京航空航天大学出版社,2006:35-49. LI Lanying.NIOSⅡ Embedded Soft Core SOPC Design Principle and Application[M].Beijing:Beijing University of Aeronautics and Astronautics Press,2006:35-49.

[11]ANALOG DEVICE CORPORATION.AD7980 Data Sheet[EB/OL].[2014-12-08].http://www.analog.com/en/products.

[12]冯莹靓,代寿刚.基于SOPC与乒乓存储的车载信息终端设计[J].吉林大学学报:信息科学版,2013,31(2):124-130. FENG Yingliang,DAIShougang.Design of Intelligent Vehicle Information Terminal Based on SOPC&Butterfly Storage[J]. Journal of Jilin University:Information Science Edition,2013,31(2):124-130.

[13]ALTERA CORPORATION.CycloneⅡDevice Handbook[EB/OL].[2014-12-08].http://wl.altera.com/literature/lit-index.html.

[14]ALTERA CORPORATION.NiosⅡSoftware Developer's Handbook[EB/OL].[2014-12].http://wl.altera.com/literature/ lit-index.htm l,2014:151-156.

[15]潘松,黄继业.EDA技术实用教程-VHDL版[M].4版.北京:科学出版社,2010. PAN Song,HUANG Jiye.EDA Technology Practical Tutorial-VHDL Version[M].4th ed.Beijing:Science Press,2010.

[16]PETER JASHENDEN.VHDL嵌入式数字系统设计教程[M].夏宇闻,夏嘉宁等译.北京:北京航空航天大学出版社,2011. PETER JASHENDEN.Digital Design:An Embedded Systems Approach Using VHDL[M].Beijing:Beijing University of Aeronautics and Astronautics Press,2011.

(责任编辑:刘东亮)

Implementation of Multi-Channel High-Speed Data Acquisition and Storage System Based on NiosⅡ

ZHU Yu1,WANG Lianming1,AIShuping2

(1.School of Physics,Northeast Normal University,Changchun 130024,China; 2.Department of Foundational Science,Jilin Jianzhu University,Changchun 130118,China)

In order to realize parallelmulti-channel high-speed data acquisition and storage,amethod which is based on FPGA(Field Programmable Gate Array)and NiosⅡis proposed.This system can realize the parallel control ofmulti-channel ADCs(Analog-to-Digital Converter),to achieve parallel high-speed acquisition ofmultichannel signal.The data acquired and the FPGA configuration data can share the configuration memory,which can save the extra storage devices,and reduce the system cost.In the experiment,use EP2C35F672C8 as core,AD7980 as ADC,EPCS64 as the storagemedium,to achieve entirely parallel acquisition for 15-channel analog signal.The adoption of soft core technologymakes the system more flexible and extensible.The results show that it provides new ideas to projectswhich requires low cost,frequent system upgrade.

NiosⅡ controller;field programmable gate array(FPGA);multi-channel data acquisition;high speed;parallel;erasable programmable configurable serial(EPCS)

TN79;TP274

A

1671-5896(2015)06-0632-05

2015-02-07

国家自然科学基金资助项目(21227008);吉林省科技厅基金资助项目(20130102028JC)

祝宇(1990— ),女,长春人,东北师范大学硕士研究生,主要从事嵌入式系统研究,(Tel)86-15143000427(E-mail) zhuy609@nenu.edu.cn;通讯作者:王连明(1972— ),男,吉林白山人,东北师范大学教授,硕士生导师,博士,主要从事智能信息处理及嵌入式系统研究,(Tel)86-13086848199(E-mail)wanglm703@nenu.edu.cn。