集成电路测试平台中交流源输出方波的特性改进

姚海燕

(江苏省南通中等专业学校,江苏省联合职业技术学院南通分院,江苏 南通 226011)

随着世界大多数半导体公司在中国建立封装测试工厂,测试设备成本竞争压力越来越大。越来越多的国产集成电路测试机凭借其优良的性价比逐步占领了集成电路测试行业的中低端市场。很多公司抓住市场改革机遇大量购进国产测试机并取得了明显的生产效益。但是正像其它任何新兴事物一样,国产测试机在发展的过程中总有一些不够完善的地方需要改进,比如有些机型在实现低成本的同时也出现测试源的噪声大、输出波形不稳定等问题,给集成电路测试带来麻烦,影响了测试的准确性。

1 交流源(ACSM)的基本工作原理

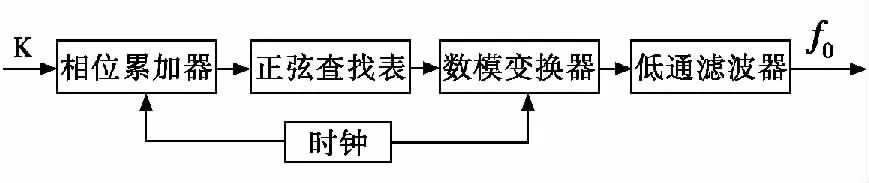

目前,国内集成电路测试机交流源有很多种类型,笔者接触到的一种交流源主要由AD9952 产生时钟信号,高速DAC 产生输出波形。整个交流源的工作原理与AD9952 内部电路工作原理类似。其中,AD9952 的组成框图如图1 所示,它主要由参考时钟、相位累加器、正弦查询表、数模转换器(DAC)及低通平滑滤波器等构成[1]。理论上,这种交流源能够产生任意周期波形,并提供给后级的测试电路。因此,交流源输出波形的稳定性直接决定了集成电路某些参数测试的准确性。

图1 AD9952 组成框图

2 交流源输出方波的特性及稳定性的改进

2.1 交流源输出方波的特性

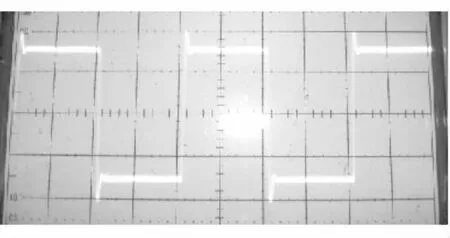

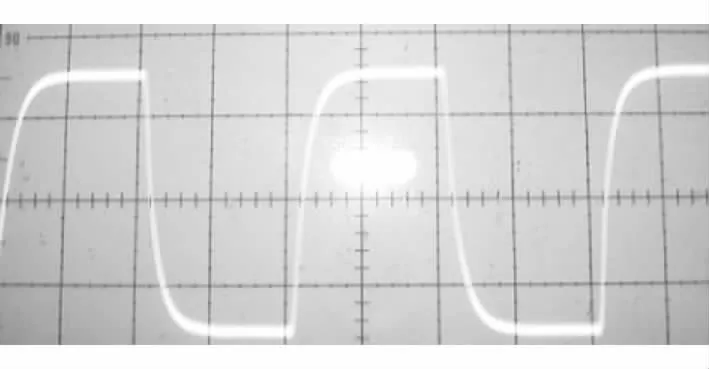

以Fairchild 公司的集成电路FAN7529 的测试为例,该电路在测试参数IDCC 时需要在器件上施加一个频率为50 kHz 的方波信号,然后串联一个20 kΩ 的电阻到被测器件。该参数的典型值在2 mA 左右。在完全按照测试SPEC的测试条件后发现实际测试值比典型值大了0.9~1 mA,而且测试结果很不稳定。通过示波器观察发现,该交流源输出方波信号在高电平和低电平的起始端均有一个0.3~0.5 V的Spike,如图2 所示,此时的方波输出的确存在不稳定的情况。

图2 交流源输出方波信号

2.2 交流源输出方波的特性分析

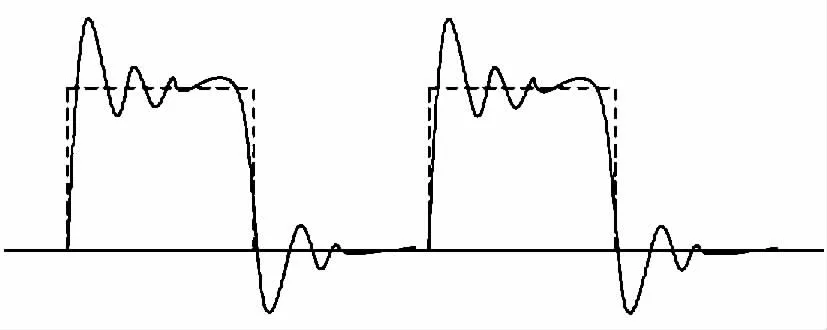

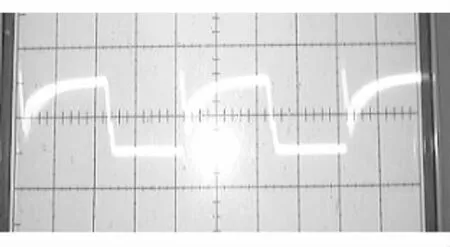

该方波是由交流源上的AD9952 产生时钟,再由高速DAC 输出的。经分析发现,方波上的Spike 是由内部晶体振荡器输出波形“过冲”现象引起的,过冲现象的一般波形示意图如图3 所示。在方波的高电平和低电平处均有电压的不稳定变化,这种不稳定变化有可能影响了最终的测试结果。

图3 过冲示意图

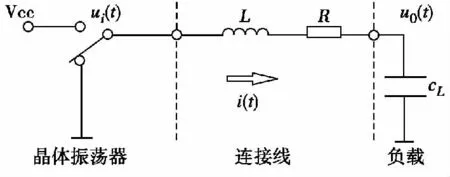

为分析Spike 的产生原因,将交流源与测试电路等效成产生输出方波的晶体振荡器、测试电路连线以及负载组成,如图4 所示。

图4 测试电路分析等效图

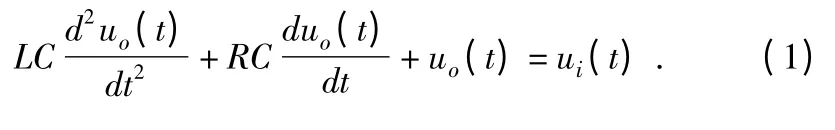

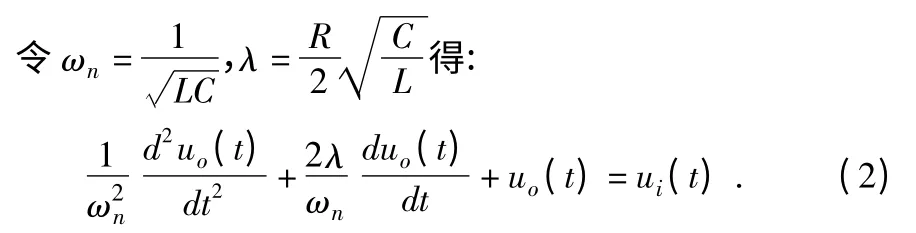

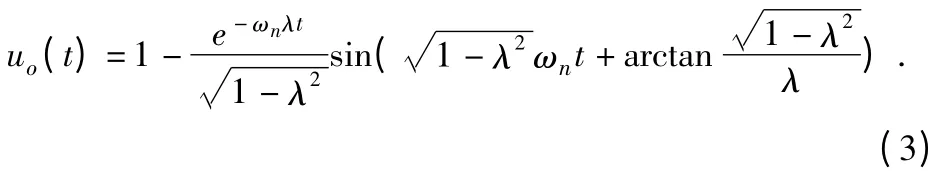

按照晶体振荡器输出波形的一般方程:

在输入为单位阶跃电压,λ <1 时,该方程的解为:

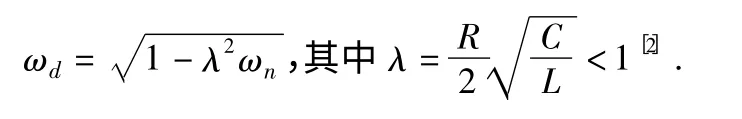

因此在λ <1 时系统响应是振荡的,振荡频率为:

根据上述方程,在λ=0 时,振荡频率ωd=ωn,系统无阻尼,输出方波应无过冲。在λ >1 时,输出波形单调上升。在0 <λ <时,输出为衰减振荡,也就是在上述测试中遇到的问题。在这种情况下系统响应的暂态过程为在输出高电平(或低电平)值上反复上下振荡,振荡频率ωd比ωn小。由于存在振荡,暂态过程中出现“过冲”,“过冲”幅度有可能达到高电平的2 倍[3]。这种振荡是随时间逐渐衰减的,这正是我们在测试中看到的,晶体振荡器的输出波形在其上升沿或下降沿出现的“过冲”现象。也正是由于交流源输出波形的不稳定性直接导致了集成电路测试时相关参数的不稳定。因此,在进行集成电路测试时必须在交流源信号进入被测器件前滤除该Spike,也就是消除该过冲现象。

2.3 交流源输出方波的特性改进

1)增大C,即增加负载电容。在DUT 板的信号输入端增加一个电容,经实践确认最佳值为100 pF,但是效果不是很理想,有些地方仍然存在Spike。

2)减小L,减少测试回路连接线的长度。由于FAN7529 的测试回路是PCB 板,因此该方法也是不可能实现的。

3)增大R,增大测试回路的电阻。在交流源输出端和FAN7529 测试DUT 板的信号输入端之间串一个电阻,经实践确认最佳值为10 kΩ。

因此,本次测试改进交流源输出方波选择了第三种方法。实践证明,在串入10 kΩ 电阻后,在不接入被测器件时,Spike 被成功滤除,虽然波形有些圆角但是不影响测试,如图5 所示。但是,这种方法在接入被测器件后测试值依然不理想,如图6 所示,因为按照被测器件FAN7529 的测试要求,交流源信号在进入被测器件前要先经过一个20 kΩ 的电阻,按照此接法就相当于外接了一个30 kΩ 的电阻,显然不符合测试要求。因此,实际测试时在交流源信号经过10 kΩ 电阻后增加了一个Buffer,增强交流源带负载能力,如图7 所示。

图5 不接被测器件时的输出波形

图6 接被测器件后的输出波形

图7 交流源输出波形的改进电路

以图7 的线路对FAN7529 的测试DUT 板进行更改后,大大消除了测试机交流源输出方波的Spike,测试值也接近于典型值。该项参数测试经机械手多次测量,误差在百分之一以内,符合一般集成电路的测试要求。

3 结论

集成电路测试平台交流输出波形的稳定性对某些参数的测试起到至关重要的作用,是集成电路产品性能稳定性的重要保障。为提高交流源输出方波的稳定性,可以通过增大C、减小L 或者增大R 来实现。当然,具体问题具体分析,在实际进行集成电路测试时,除上述方法外,可能还需要另辟蹊径。国产测试机的发展毕竟才经历了一些变革,相信测试机厂家会进一步改进机器的性能。同时,对于广大一线的测试工程师而言,在已有的测试条件下,利用技术手段,提高交流输出波形的稳定性、改进测试方法是非常有必要的。

[1]曾凡辉,刘春梅.晶体振荡器输出波形“过冲”现象的分析[J].压电晶体技术,2001(1) :34-39.

[2]赵声衡,赵英.晶体振荡器[M].北京:科学出版社,2008.

[3]余中杰,费元春.超低功耗DDS 芯片AD9952 及应用[J].信息技术,2004,28(9) :14-17.