基于ARM+FPGA的引信信息测试系统设计与实现

吴茂林,吴向臣,周在龙

(1.海军工程大学 兵器工程系,湖北 武汉 430033;2.华北计算机系统工程研究所,北京 100083)

基于ARM+FPGA的引信信息测试系统设计与实现

吴茂林1,吴向臣1,周在龙2

(1.海军工程大学 兵器工程系,湖北 武汉 430033;2.华北计算机系统工程研究所,北京 100083)

引信信息交联信号具有快速性、瞬时性和高频率等特性。通过嵌入式系统和FPGA设计实现了一种引信信息交联信号的测试系统,能同时对多路引信交联信息进行实时检测、信息发送装定和反馈,通过对高频瞬时信号的信息处理,设计专用调制解调与编码解码电路和人机交互应用程序。设计的测试系统经过多次试验,验证了其有效性和准确性。

ARM;FPGA;系统设计;硬件电路;软件结构

0 引言

随着微型化智能化设备的不断发展,单纯的单片机设备已经不能满足目前对高性能的测试与试验设备的要求。引信交联信息具有高频性、瞬时性等特点,对多路引信交联信息的测试对设备的实时性、信息处理能力要求高,本文设计实现了一种基于FPGA+ARM结构的引信交联信息测试设备,实现了准确、快速的多路引信交联信息的处理,具有交联信息发送、信息接收反馈功能,以及精度高、操作简单、功能可选等众多优点,同时具有广阔的功能拓展空间。

1 测试设备总体结构

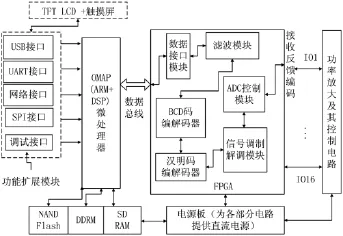

系统总体设计围绕测试设备的功能实现和各部分的技术要求展开,结合某型电子引信通信协议和与系统交联信息的特征,同时考虑测试设备后续的功能扩展性,本文对实现测试设备的关键电路进行总体设计。测试系统总体上可以划分成硬件和软件两部分,硬件系统由高性能ARM处理器[1]和外围的接口电路组成,以ARM为架构的嵌入式核心电路模块实现对数据信号的处理和对操作界面的支持,FPGA[2]可编程逻辑电路完成数据的编码、调制和发送,驱动反馈模块完成12路特定时序的交联信号的驱动放大,满足信息测试要求。总体结构如图1所示。

图1 系统设计图

软件系统以Linux内核环境下开发的应用程序为主,其软硬件功能均大大高于单片机系统,满足设计需求。

2 硬件电路设计

系统硬件电路采用 AltiumDesigner10软件进行设计实现,ARM核心板按 8层印制板布线,FPGA及外围接口电路按6层印制布线。主要核心电路[2,3]是FPGA+ARM外围架构电路和电源管理电路。

2.1 FPGA+ARM架构设计

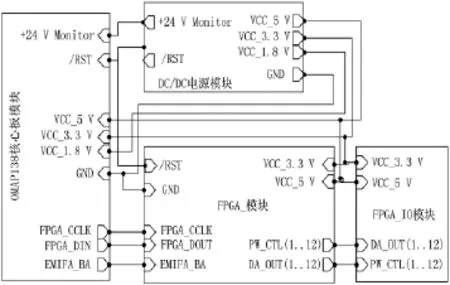

设计的FPGA+ARM的硬件架构封装结构图如图2所示,封装电路图展示了ARM核心处理器和FPGA外设之间的信号和布线关系。通过以ARM处理器为核心,FPGA可编程逻辑为外设的模式构建该硬件系统。为了实现设备的相关功能,该FPGA+ARM结构包含了:FPGA电路结构、FPGA IO电平转换电路结构、FPGA调试电路结构。

图2 FPGA+ARM电路结构图

2.1.1 FPGA电路结构

FPGA电路结构中,FPGA的FPGA_INT端和ARM处理器相连,实现对FPGA外设的识别和初始化。同时将FPGA与ARM的EMIFA端口相连,该端口为EMIF端口的一类,即外部存储接口,实现核心板与不同类型的存储器连接。将该接口与FPGA相连,使FPGA充当一个协同处理器、高速数据处理器和高速数据传输口,这里主要用于实现FPGA与ARM平台的数据交联。

2.1.2 IO电平转换模块

将FPGA与IO电平转换模块连接。直接从FPGA输入输出的信号电压只有 3.3 V,需要经过该电路进行转换为5 V后方可与外部电路进行对接,该电路也是输出缓冲电路。设计该缓冲电路作为可编程逻辑电路与信号驱动和反馈电路的桥梁。FPGA数据经过缓冲后发送给信号驱动电路,同时也可以接收来自反馈电路的反馈数据再发送给FPGA设备。

2.1.3 FPGA调试模块

该电路主要设计有两种功能,第一,FPGA模式选择;第二,FPGA的JTAG调试。模式选择主要通过M0和M1两个端口,在实际电路中通过跳线帽短接的方式进行模式的选择。JTAG作为 FPGA设备的在线编程和调试接口,设计用来对设备进行现场编程和设备调试。

2.2 电源管理电路设计

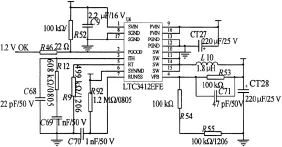

系统结构中涉及到ARM芯片、FPGA芯片、液晶屏、触摸屏、信号驱动等多种直流电压的供电,而设备由ARM核心板输出的供电电压为直流 24 V,远远大于相应模块的供电上限。设计本电路的核心目的就是将直流24 V经DC-DC转换后为相关芯片和器件供电。同时,由于工作对象是引信及其系统,电路还应具有系统复位功能和驱动保护功能。设计的电压转换电路如图3所示。

图3 电压转换电路

电压转换电路设计中使用DC/DC转换器(LTC3736-EUF元件),用于控制电压的输出,通过这个元件可以将5 V的电压转化成1.2 V的电压,以使其电压值满足设计需求。同时设计了复位重置电路,当设计系统出现宕机等意外情况时可以通过该电路对整个系统重新上电,使所有元件初始化后重新启动。

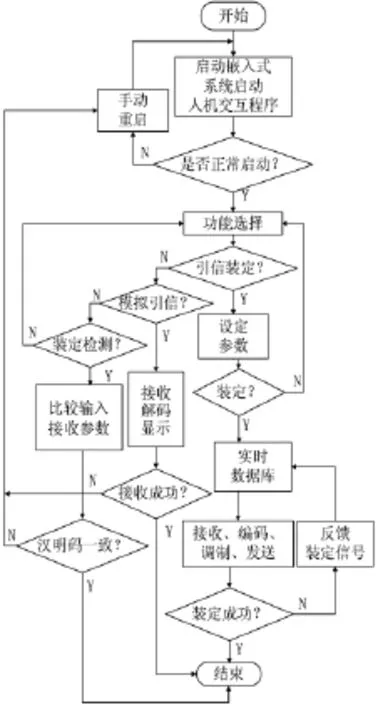

图4 系统主程序流程图

3 软件结构设计

3.1 软件总体结构

软件系统总体结构[4]设计一方面体现在系统主程序的设计上,系统的主程序流程图如图4所示,设计的主程序主要包括实现信号的输入/输出、数字调制解调、编码发送和反馈接收等功能,实现了基于Linux操作系统下的 ARM与FPGA接口驱动、LCD液晶驱动、网口驱动、串口驱动、触摸屏驱动和 Ubifs文件系统管理;另一方面体现在嵌入式系统人机界面设计和FPGA数据处理程序设计。

3.2 人机交互程序设计

人机交互程序使用 QTouch组态软件实现。在软件的设计中重点考虑应用程序的简洁、美观和实用性。根据主程序流程图,设备功能主要分为模拟引信、引信装定和装定检测三大功能,因此设计应用程序时针对三大功能设置相应的操作界面和选择界面设计以及数据交换机制设计。

3.3 FPGA数据处理程序设计

FPGA主要实现信号的调制与编码[5],然后将处理完毕的数据发送给接收端。

调制信号为二进制序列时的数字频带调制称为二进制数字调制。在对引信装定编码信号进行调制和解调时,通过FPGA采用的是二进制振幅键控方式(ASK)来实现,数据处理程序流程框图如图5所示。图5(a)为信号装定程序设计流程图,它显示了FPGA设备如何将获得的装定参数经过调制编码发送到引信体中,并通过反馈检测,检测其装定的正确性。图 5(b)为模拟引信接收程序流程图,它反映了模拟引信如何接收来自装定控制柜的装定信息,并将该信息实时显示。

图5 数据处理程序流程框图

4 实验验证

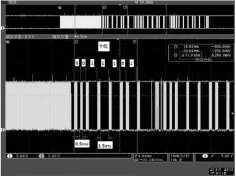

电路设计完成后。经过实验室多次实验,对该系统的实际功能进行了严格测试。电路的测试与波形图如图6所示。

图6 电路测试波形图

由图6可见,信号表示一位数据的波形时间为11 ms左右,时间短脉冲多频率高,这给信号的处理和接收都带来了很大麻烦。因此基于FPGA的高速处理能力设计实现了ARM+FPGA结构的引信交联信息的检测系统。实验结果表明该电路设计完全符合设计要求。通过高性能示波器捕捉到的波形显示,该电路发送和接收的信号波形与理论信号波形完全一致,成功实现了对瞬时高频信号的收发和处理,验证了该电路具有对引信信息交联信号的检测与处理能力。

5 结语

本次装定检测设备的设计采用 ARM+FPGA架构,通过对电源管理电路、FPGA+ARM架构相关电路以及重点的信号接收与反馈电路的设计,完成了设备的硬件平台搭建,并设计编写了底板数据处理程序和人机交互应用程序。根据后续的实验发现该设计完全满足设备的需求。该类设计可以在其他类似类型的检测设备中得到广泛应用,同时该设备具有良好的可拓展,可以根据实际需求设计其他检测功能。

[1]韦东山.嵌入式Linux应用开发完全手册[M].北京:人民邮电出版社,2008.

[2]王晓勇.FPGA的基本原理及运用[J].舰船电子工程,2005,25(2):82-85.

[3]郭瑞,林岩.OMAP-138和FPGA的合并单元设计方案[J].单片机与嵌入式系统应用,2012(11):49-52.

[4]王学慧,周晓东,张河.基于 CPLD的引信感应装定器设计[J].弹箭与制导学报,2003,23(4):87-89.

[5]雷斌,王宁.FPGA的汉明码数据传输系统的设计[J].西安工业大学学报,2009,29(6):559-564.

Designing and realizing of the system to check the fuze's information based on ARM+FPGA

Wu Maoling1,Wu Xiangchen1,Zhou Zailong2

(1.Naval Univ.of Engineering,Dept.of Weaponry Engineering,Wuhan 430033,China; 2.National Computer System Engineering Research Institute of China,Beijing 100083,China)

The signal of the fuse is fast,momentary and altofrequent.This article comes up with a testing system of the signal from the fuse,and it is based on the embedded system and the FPGA.This system can not only deal with the signals from several channels at the same time,but also realize the real-time detection,information transfer and information feedback.The appropriative demodulation circuit,encoding circuit and decoding circuit are designed through the high-frequency and momentary signal processing.It has been proved that this system is effective and reliable,after several times of the system testing.

ARM;FPGA;system design;hardware circuit;software architecture

TP206.1

A

10.16157/j.issn.0258-7998.2015.08.006

吴茂林,吴向臣,周在龙.基于 ARM+FPGA的引信信息测试系统设计与实现[J].电子技术应用,2015,41 (8):24-26.

英文引用格式:Wu Maoling,Wu Xiangchen,Zhou Zailong.Designing and realizing of the system to check the fuze's information based on ARM+FPGA[J].Application of Electronic Technique,2015,41(8):24-26.

2015-03-31)

吴茂林(1978-),男,硕士,副教授,主要研究方向:兵器对抗技术。

吴向臣(1990-),通信作者,男,硕士研究生,主要研究方向:兵器对抗技术,E-mail:1090200318@qq.com。