PCB布线中的过孔和电容效应分析和结构优化

尚文亚+刘丰满+王海东+何慧敏+万菲+于大全+上官东恺

摘 要: 在多层PCB布线中,过孔和电容是常见的不连续结构。信号线在不同平面间转换传输路径时,过孔与回流层之间的寄生电容与寄生电感将引起信号完整性的相关问题;而常用的传输线上的AC耦合电容等,引入了阻抗突变的结构,由此带来了反射等相关问题。通过对多层PCB上的过孔进行建模仿真,研究不同变量对过孔性能的影响趋势,以协助信号完整性问题的分析;通过对电容阻抗突变处进行不同形式的补偿,仿真和测试结果相验证,得到提高信号传输质量的解决方案。

关键词: PCB传输线; 过孔效应; 阻抗突变; 信号完整性

中图分类号: TN41?34 文献标识码: A 文章编号: 1004?373X(2015)16?0110?05

Effect analysis and structure optimization of via hole and capacitance in PCB wiring

SHANG Wenya1,2, LIU Fengman1,3, WANG Haidong1,3, HE Huimin1, 2, 3, WAN Fei1, 3, YU Daquan3, 4, SHANGGUAN Dongkai1, 3

(1. National Center for Advanced Packaging (NCAP China), Wuxi 214135, China; 2.University of Chinese Academy of Sciences, Beijing 100049, China;

3. Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China; 4. Huatian Technology, Xian 710018, China)

Abstract: Via hole and capacitance are common disconnecting structures in multi?layer PCB wiring. As signal line travels among different layers, signal integrity problems from parasitic capacitance and inductance between via hole and backflow layer occurs. The AC coupling capacitances on common transmission lines will also bring in a structure of the resistance mutation, which will result in reflection and other related problems. By modeling and simulation for via holes on multi?layer PCB, the effects of different variables on performance of the via holes were studied to assist the analysis of signal integrity. Compensation in different modes is conducted for the resistance mutation of capacitance. The simulation results were verified by the related tests. The solution to improve the signal transmission properties was obtained.

Keywords: transmission line on PCB; via hole effect; resistance mutation; signal integrity

现代电子产品益趋向高密度、小型化的方向发展,封装内的布线密度不断增加。而随着数字信号传输速率的不断提高,信号的上升沿越来越短,过孔和电容等不连续结构带来的对传输线特征阻抗的影响越来越明显[1?2]。而不同的介质和层叠结构上的不连续结构对电学性能的影响不尽相同,对阻抗不连续结构的阻抗补偿形式不可一概而论。基于项目实际应用中的线性和层叠结构,本文设计了多种测试结构以提取和验证适合于实际线路的过孔模型和阻抗补偿形式。

1 传输线与反射

1.1 反射原理

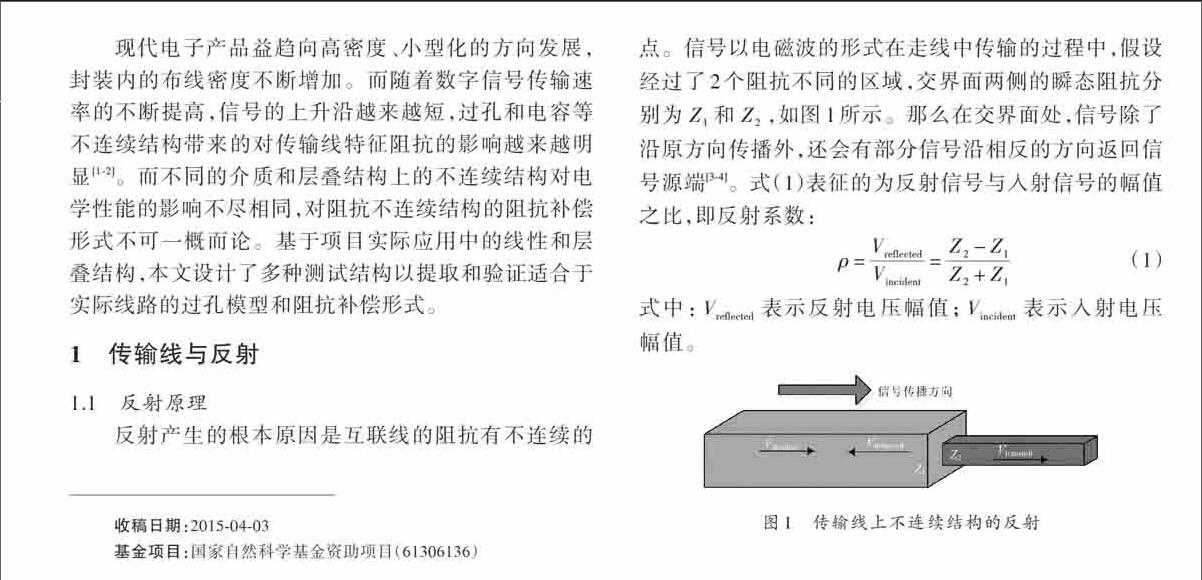

反射产生的根本原因是互联线的阻抗有不连续的点。信号以电磁波的形式在走线中传输的过程中,假设经过了2个阻抗不同的区域,交界面两侧的瞬态阻抗分别为[Z1]和[Z2],如图1所示。那么在交界面处,信号除了沿原方向传播外,还会有部分信号沿相反的方向返回信号源端[3?4]。式(1)表征的为反射信号与入射信号的幅值之比,即反射系数:

[ρ=VreflectedVincident=Z2-Z1Z2+Z1] (1)

式中:[Vreflected]表示反射电压幅值;[Vincident]表示入射电压幅值。

图1 传输线上不连续结构的反射

1.2 容性突变与感性突变

对于式(1),当阻抗为电阻性阻抗不连续时,在阻抗不连续点两侧的阻抗值都是固定的,因而反射系数也是恒定的。而当阻抗为容性或感性不连续时,信号得到的阻抗却是随时间变化的,因而反射系数也是变化的。

在如图2(a)所示的RC电路中,电容随着电压的变化充放电,电容两端的电压随时间变化。假设高电平电压幅度A,则电容两端的电压可表示为:

[VC=A(1-e-tτ)] (2)

式中:[τ=RC]为电路的时间常数。流过电容的电流为:

[IC=CdVCdt=ARe-tτ] (3)

因此,电容的阻抗可表示为:

[ZC=VCIC=R(etτ-1)] (4)

反射系数可表示为:

[ ρ=ZC-RZC-R=Retτ-1-RRetτ-1+R=1-2?e-tτ] (5)

由公式可看出,在上电的瞬间,电容的阻抗为0,电容两端的电压迅速上升,充电电流很大;随着电容充电,阻抗变为无穷大,最终相当于开路。图2(b)中比较了电路中无负载电容和有负载电容时的输出电压的瞬态变化,由于电容的作用,输出电压的上升时间明显变缓。在高速电路中,输入电压的上升沿变换迅速,电容引起的时延如果超过了信号的上升时间,将引起信号沿变化变缓、延时等问题[3?5]。

图2 RC震荡电路及其对输出电压的影响

在图3(a)所示的RL电路中,在激励源产生瞬变的电平变化时,通过电感的电流可表示为:

[IL=AR(1-e-tτ)] (6)

式中:[τ=LR]为电路的时间常数;A为高电平的幅值。则电感两端的电压可表示为:

[VL=LdILdt=Ae-tτ] (7)

电感的阻值可表示为:

[ZL=VLIL=Re-tτ1-e-tτ] (8)

反射系数可表示为:

[ρ=ZL-RZL-R=Re-tτ1-e-tτ-RRe-tτ1-e-tτ+R=2?e-tτ-1] (9)

由公式可以看出,在上电的瞬间,反射系数为+1,相当于开路,使得反射信号与入射信号叠加,出现一个波峰。随后信号电压按指数规律迅速下降,最终反射系数为-1时反射结束,电感处相当于短路。如图3(b)为电路中有电感与无电感负载时的输出电压瞬态变化值,电感的存在使得输出端电压产生类似于噪声一样的波峰,如果上冲的幅度过大、电压变化频繁,将影响实际电路的正常工作,甚至引起信号误判[3?5]。

图3 RL震荡电路及其对输出电压的影响

2 不连续结构的电学仿真

本文基于一款光电转换系统的设计中所遇到的电学问题,对布线过程中遇到的不连续结构进行信号完整性研究,得出相关的仿真和优化结论。系统中测试板使用的普通FR4材料,介电常数为4.4,损耗角为0.02。叠层结构为图4(a)中所示的8层板,表层为信号层,主要的信号走线均为差分线,阻抗匹配后的线型为图4(b)中所示。本节后续的仿真均以图4中的叠层和线型在HFSS软件中进行建模。

图4 叠层和阻抗匹配后的线型

2.1 过孔影响因素仿真分析

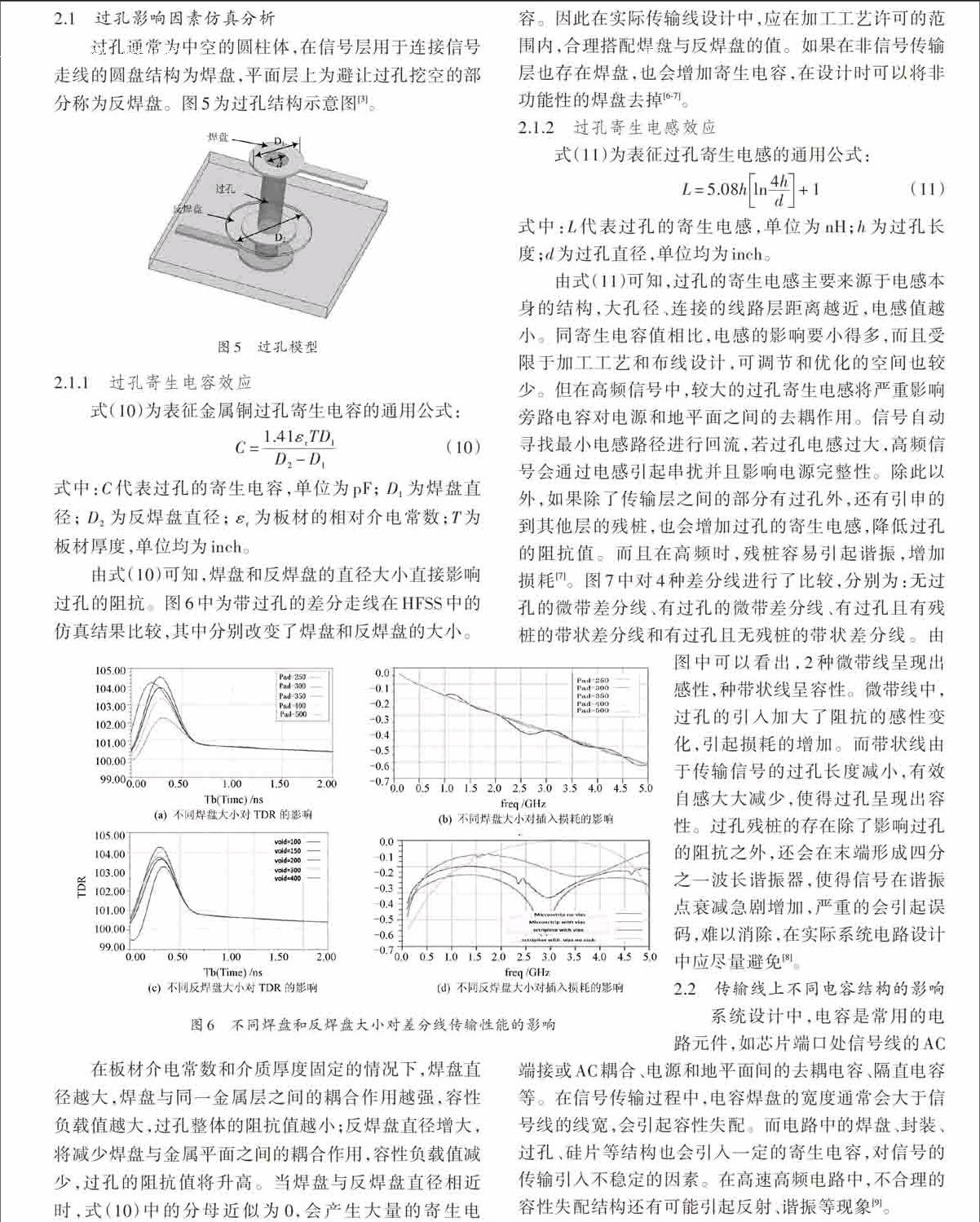

过孔通常为中空的圆柱体,在信号层用于连接信号走线的圆盘结构为焊盘,平面层上为避让过孔挖空的部分称为反焊盘。图5为过孔结构示意图[3]。

图5 过孔模型

2.1.1 过孔寄生电容效应

式(10)为表征金属铜过孔寄生电容的通用公式:

[C=1.41εrTD1D2-D1] (10)

式中:C代表过孔的寄生电容,单位为pF;[D1]为焊盘直径;[D2]为反焊盘直径;[εr]为板材的相对介电常数;T为板材厚度,单位均为inch。

由式(10)可知,焊盘和反焊盘的直径大小直接影响过孔的阻抗。图6中为带过孔的差分走线在HFSS中的仿真结果比较,其中分别改变了焊盘和反焊盘的大小。

在板材介电常数和介质厚度固定的情况下,焊盘直径越大,焊盘与同一金属层之间的耦合作用越强,容性负载值越大,过孔整体的阻抗值越小;反焊盘直径增大,将减少焊盘与金属平面之间的耦合作用,容性负载值减少,过孔的阻抗值将升高。当焊盘与反焊盘直径相近时,式(10)中的分母近似为0,会产生大量的寄生电容。因此在实际传输线设计中,应在加工工艺许可的范围内,合理搭配焊盘与反焊盘的值。如果在非信号传输层也存在焊盘,也会增加寄生电容,在设计时可以将非功能性的焊盘去掉[6?7]。

2.1.2 过孔寄生电感效应

式(11)为表征过孔寄生电感的通用公式:

[L=5.08hln4hd+1] (11)

式中:L代表过孔的寄生电感,单位为nH;h为过孔长度;d为过孔直径,单位均为inch。

由式(11)可知,过孔的寄生电感主要来源于电感本身的结构,大孔径、连接的线路层距离越近,电感值越小。同寄生电容值相比,电感的影响要小得多,而且受限于加工工艺和布线设计,可调节和优化的空间也较少。但在高频信号中,较大的过孔寄生电感将严重影响旁路电容对电源和地平面之间的去耦作用。信号自动寻找最小电感路径进行回流,若过孔电感过大,高频信号会通过电感引起串扰并且影响电源完整性。除此以外,如果除了传输层之间的部分有过孔外,还有引申的到其他层的残桩,也会增加过孔的寄生电感,降低过孔的阻抗值。而且在高频时,残桩容易引起谐振,增加损耗[7]。图7中对4种差分线进行了比较,分别为:无过孔的微带差分线、有过孔的微带差分线、有过孔且有残桩的带状差分线和有过孔且无残桩的带状差分线。由图中可以看出,2种微带线呈现出感性,种带状线呈容性。微带线中,过孔的引入加大了阻抗的感性变化,引起损耗的增加。而带状线由于传输信号的过孔长度减小,有效自感大大减少,使得过孔呈现出容性。过孔残桩的存在除了影响过孔的阻抗之外,还会在末端形成四分之一波长谐振器,使得信号在谐振点衰减急剧增加,严重的会引起误码,难以消除,在实际系统电路设计中应尽量避免[8]。

2.2 传输线上不同电容结构的影响

系统设计中,电容是常用的电路元件,如芯片端口处信号线的AC端接或AC耦合、电源和地平面间的去耦电容、隔直电容等。在信号传输过程中,电容焊盘的宽度通常会大于信号线的线宽,会引起容性失配。而电路中的焊盘、封装、过孔、硅片等结构也会引入一定的寄生电容,对信号的传输引入不稳定的因素。在高速高频电路中,不合理的容性失配结构还有可能引起反射、谐振等现象[9]。

图8为差分信号线转表贴SMA头的传输线,为了进行信号的输入和输出需添加0402型号100 nF的电容,(a)中电容并排排列且在电容pad处直接进行了到单端的转接,出现了直角结构;(b)中在(a)的基础上,信号在电容后有一段过度后转为单端信号;(c)中将两个电容分开摆放。对图8中3种电容摆放方式分别进行了仿真比较,结果如图9所示。

由图9看出,图8(c)结构的传输性能最好,阻抗失真较小。在图8(a)和(b)中,由于电容的并排排列,导致电容焊盘之间也存在大量的寄生电感和寄生电容,而且与过孔距离较近,导致阻抗失配效应叠加[10]。

图8 电容的3种不同布线结构

3 测试结果

为了验证传输线不连续结构处的可靠性,在投板时附加了科邦线的制作,如图9所示,针对上节中的几种结构设计了测试结构并做了对比分析。

图10为科帮线的成品图,图11为几种差分线的测试结果对比,线性结构分别为微带线、带过孔的微带线和带过孔的带状线,长度均为7 cm。由测试结果可以看出,由于设计中的过孔结构不合理,引入了比较严重的阻抗不连续点,导致插入损耗的曲线中出现了下冲现象。如果出现下冲的频段在数字信号的有效带宽范围内,有可能会影响信号的二次或三次谐波[6]。对带有SMA结构的传输线,科邦线上也做了测试结构设计,有效长度10 cm左右,在靠近SMA附近有添加0402的电容。

图9 三种电容排列方式对差分线传输性能的影响

图12为两块科邦板上各2条SMA结构的测试数据的比较,由图中可以看出,插损的曲线纹波较平缓,由于设计的传输线长度较大且不连续结构较多,回路损耗值较高。与图11中的曲线相比较,合理的电容阻抗匹配结构比过孔的影响要小的多,在实际系统设计中,应减少关键信号如时钟等进行过孔走线,并且尽可能地优化过孔自身的特性[10]。

图10 科邦线的成品

图11 三种传输线的插入损耗测试值比较

图12 带SMA结构的差分线测试数据

4 结 语

本文针对设计中遇到的传输线上的过孔和电容结构进行建模仿真,对不同变量对传输线性能的影响进行具体分析,并给出了优化意见。通过对测试结构的对比分析,验证了相关的仿真和分析的结论。

参考文献

[1] FAN Jun, YE Xiaoning, KIM Jingook. Signal integrity design for high?speed digital circuits: progress and directions [J]. IEEE Transactions on Electromagnetic Compatibility, 2010, 52(2): 20?30.

[2] JIANG Jing, KONG Lingwen. Study of signal integrity for PCB level [C]// 11th International Conference on Electronic Packaging Technology & High Density Packaging. [S.l.]: IEEE, 2010: 828?833.

[3] 于争.信号完整性SI揭秘[M].北京:机械工业出版社,2013.

[4] Eric Bogatin.信号完整性分析[M].李玉山,李丽平,译.北京:电子工业出版社,2008.

[5] 王海东.10 GbpsQSFP设计中信号完整性的分析[D].北京:中国科学院研究生院,2012.

[6] KIM Jin?Ho, HAN Sung?Woo, KWON Oh?Kyong. Analysis of via in multilayer printed circuit boards for high?speed digital systems [C]// Proceedings of International Symposium on Electronic Materials and Packaging. Jeju Island: IEEE, 2001: 382?387.

[7] PAJOVIC Miroslav, YU Jinghan, MILOJKOVIC Dragan. Analysis of via capacitance in arbitrary multilayer PCBs [J]. IEEE Transactions on Electromagnetic Compatibility, 2007, 49(3): 722?726.

[8] MIRALR?O Enrique López, RUIZ César Méndez. Signal integrity design of via with extra routing stub for device routing flexibility [C]// IEEE Electrical Design of Advanced Packaging & Systems Symposium. [S.l.]: IEEE, 2013: 189?192.

[9] KOO Tae?Wan, KANG Hee?do, YOOK Jong?Gwan. Signal integrity enhancement of high?speed digital interconnect with discontinuous and asymmetric structures for mobile applications [C]// 2013 IEEE International Symposium on Electromagnetic Compatibility (EMC). Denver, CO: IEEE, 2013: 713?717.

[10] HSU Sheng?Yun, CHOU Chiu?Chih, WU Tzong?Lin. Signal integrity: influence of non?linear driver, different bit rates, and estimation by different algorithms[C]// 2014 International Symposium on Electromagnetic Compatibility. Tokyo: ISEC, 2014: 121?124.