基于PCI总线的PowerPC8245处理器嵌入式系统硬件的设计与实现

樊江锋+徐连波+叶波+王旭东

摘 要: MPC8245处理器芯片是一款高性能、低功耗处理器,该处理器集成了MPC603e内核及PCI桥,存储器控制器,DMA控制器,可编程中断控制器和I2C控制器。支持浮点运算,存储器管理,16 KB命令Cache,16 KB数据Cache,电源管理等功能。作为PCI接口的处理器模块接口,其可以广泛应用于PCI接口的嵌入式计算机,PCI接口逻辑、驱动设计简单,结构清晰,易于扩展。

关键词: PowerPC8245; 处理器; PCII; I2C控制器

中图分类号: TN911?34 文献标识码: A 文章编号: 1004?373X(2015)16?0062?04

Design and implementation of embedded system hardware of MPC8245 processor

based on PCI bus

FAN Jiangfeng, XU Lianbo, YE Bo, WANG Xudong

(AVIC Computing Technique Research Institute, Xian 710119, China)

Abstract: MPC8245 is a processor chip with high capability and low power consumption. It is integrated with MPC603E kernel, PCI bridge, memory controller, DMA controller, programmable interrupt controller, I2C controller, and supports the functions of floating?point operation, memory management, 16 k byte command & data cache, power supply management, etc. As the interface of processor with PCI, MPC8245 can be widely used in embedded computers with PCI. Besides, the logic and driver design of MPC8245 PCI interface is simple, and it's configuration is very legible. Therefore, MPC8245 can be expanded easily.

Keywords: PowerPC8245; processor; PCI; I2C controller

PowerPC系列处理器最早是由Motorola公司、IBM以及Apple公司联合开发的,现主要由Freescale公司研制生产。由于其可升级性好,功耗低而应用最为广泛,同时在国内该处理器也应用较多,从PowerPC6XX,PowerPC7XX,PowerPC7XXX等系列都有产品应用,尤其最近几年飞速发展,被广泛应用于各类嵌入式计算机系统。

1 MPC8245处理器硬件设计及实现

1.1 系统概述

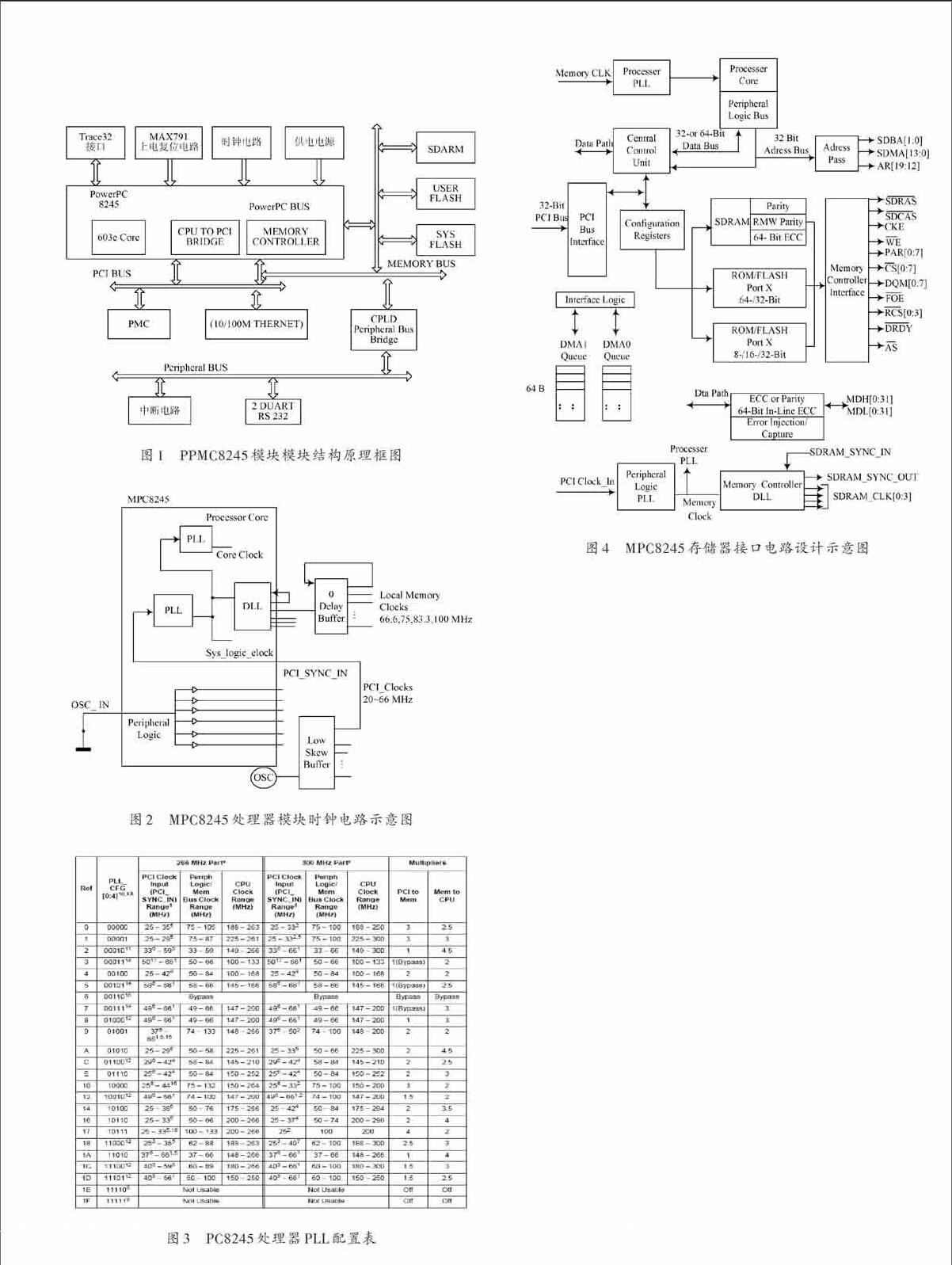

PPMC 8245模块以Motorola MPC8245处理器为核心,它内部集成了一个603e的处理器核和外设逻辑块(功能和操作方法类似MPC107);用CPLD逻辑为处理器外围电路接口控制,实现存储器资源、I/O资源、以太网和PCI设备的读/写访问以及定时器和中断的管理。

PPMC 8245模块通过MPC8245内部集成的外设逻辑块直接控制SDRAM存储器的读/写访问和刷新,定时器、以太网和PCI设备也由外设逻辑直接控制,FLASHTM存储器、NVSRAM存储器、调试串口、输入/输出离散量和中断由外设逻辑和CPLD逻辑共同控制。PMC8245处理器模块的硬件设计结构示意图见图1。

1.2 时钟电路设计

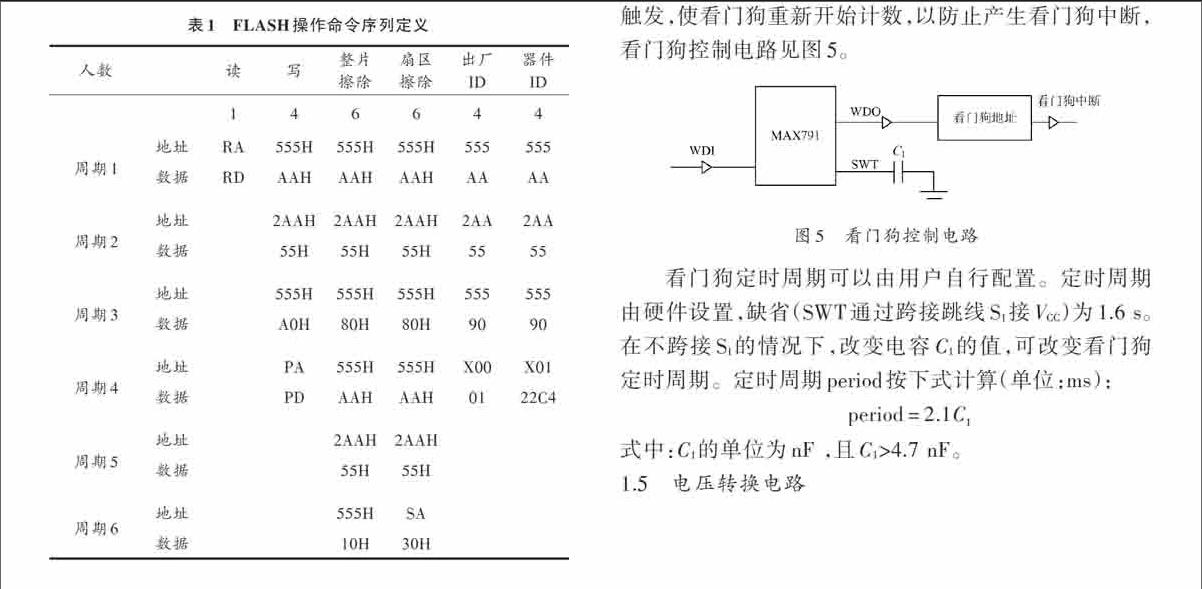

CPU模块上时钟有25 MHz,33 MHz,其时钟工作电压为3.3 V,时钟电路见图2。33 MHz时钟经时钟驱动器产生5路33 MHz同步时钟,其中1路为PCI_SYNC_IN输入到MPC8245,在经内部PLL和DLL产生SDRAM时钟,另4路输出到PMC插座上供PCI设备使用。MPC8245的PLL配置引脚为 PLL_CFG[0..4],对于给定的输入时钟SYSCLK,PLL配置对应的CPU和VCO的操作频率,PLL的配置时钟对应关系见图3。

1.3 存储器电路设计实现

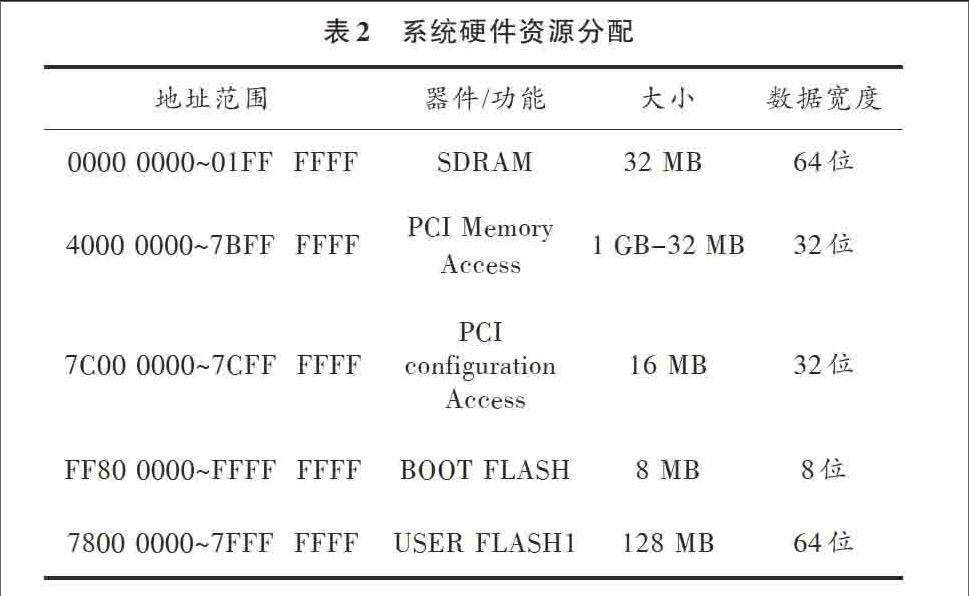

MPC8245处理器内部集成高性能存储器控制器,示意图见图4,实现处理器和PCI接口对局部存储器的访问,存储器接口支持SDRAM,FLASH,NVSRAM等。

图1 PPMC8245模块模块结构原理框图

图2 MPC8245处理器模块时钟电路示意图

图3 PC8245处理器PLL配置表

图4 MPC8245存储器接口电路设计示意图

SDRAM支持数据宽度32位或64位,速度最高133 MHz,最大支持2 GB空间,每个片选最大支持512 MB,支持RWM周期,SDRAM ECC功能。Port X接口设计挂接FLASH,NVSRAM和FPGA内部寄存器,支持8位,16位,32位,64位空间。

PPMC 8245模块通过MPC8245集成的存储器控制器,提供地址译码、数据处理周期访问时序、SDRAM时钟等来访问存储器。通过控制MPC8245内部的一些寄存器来完成这些功能。

1.3.1 SDRAM存储器

PPMC 8245模块提供64位宽度的128 MB的SDRAM,支持SDRAM校验,ECC。SDRAM采用SAMSUNG公司的K4S511632E?TCI75实现,工作电压为3.3 V,封装为54引脚的TSOP。MPC8245内置SDRAM存储器控制器,提供SDRAM的时序控制逻辑,并且提供SDRAM的访问时钟,设计频率66 MHz。地址空间位于存储器的低端0x0000000~0x7FFFFFF。访问方式及时序控制由MPC8245内部的寄存器来实现。

1.3.2 USER FLASH存储器

USER FLASH存储器用于储存用户数据。USER FLASH采用SPANSION公司的4片16位的存储器S29GL256P实现64位USER FLASH,工作电压为3.3 V,封装为56引脚的TSOP,容量设计为256 MB。每片FLASH有512个128 KWord扇区,支持整片擦写,扇区写保护等。FLASH存储器操作命令见表1。

表1 FLASH操作命令序列定义

注:RA为读FLASH地址;RD为取FLASH上RA地址的数据;

PA为FLASH地址;PD为写FLASH对应PA地址单元的数据;

SA为被擦写扇区内任意地址。

1.3.3 SYSTEM FLASH存储器

SYSTEM FLASH采用SPANSION公司的1片16位的存储器S29GL256P实现,容量为8 MB,工作电压为3.3 V,封装为56引脚的TSOP,按8位工作方式工作,容量设计为 8 Mb。

SYSTEM FLASH 地址分配在存储空间的高端,地址空间为0xFF800000H~0xFFFFFFFFH。用于通用接口模块的启动,SYSTEM FLASH上驻留监控程序,BIT测试程序,FLASH在板编程程序等。

1.4 复位电路和看门狗电路设计

模块采用单5 V电源输入,模块上选用MAX791芯片完成上电复位电路和看门狗电路,当5 V低于4.65 V时,产生复位。电源5 V电源电压低于4.65 V 时,系统处于复位状态,电源大于4.65 V后,产生大于200 ms 复位,复位本模块,同时将复位信号送至PCI总线,供其他设备使用。

看门狗电路采用MAX791和CPLD实现。当看门狗功能失效后,产生看门狗中断。看门狗中断由GSE和软件看门狗使能位WDOEN来控制。GSE为高电平时,系统处于空中状态,看门狗中断自动使能;当GSE为低电平时,系统处于地面调试维护状态,看门狗中断通过软件使能位WDOEN来控制,WDOEN为‘0时,使能看门狗,WDOEN为‘1时,禁止看门狗。看门狗电路产生中断后,送入中断电路,同时也送给通道故障逻辑电路。正常使用时要求用户必须在小于1 s间隔内产生看门狗触发,使看门狗重新开始计数,以防止产生看门狗中断,看门狗控制电路见图5。

图5 看门狗控制电路

看门狗定时周期可以由用户自行配置。定时周期由硬件设置,缺省(SWT通过跨接跳线S1接VCC)为1.6 s。在不跨接S1的情况下,改变电容C1的值,可改变看门狗定时周期。定时周期period按下式计算(单位:ms):

[period=2.1C1]

式中:C1的单位为nF ,且C1>4.7 nF。

1.5 电压转换电路

PPMC8245处理器模块上MPC8245内核电压为2.0 V,接口电压可以设置成为3.3 V,其他芯片均为5 V或3.3 V电压。5 V可由电源模块提供,接口电压3.3 V由5 V经线性可调电压转换器LTM4600HVMPV#PBF转换提供,最大电流10 A。处理器内核电压2.0 V由5 V经线性可调电压转换器LTM4600HVMPV#PBF转换提供,最大电流10 A。

1.6 中断控制器电路设计

PPMC8245处理器模块上有2个中断控制器,其中内部中断控制器(PIC)采用OpenPIC体系结构实现,在MPC8245内部实现,支持16级的串行中断。内部中断处理器可以根据中断源的特点设置中断的优先级、电平有效方式及中断向量。这2个中断控制器管理的中断送给处理器的INT中断。其中0~15个中断为模块内部中断输入到MPC8245上,标识“内部”中断为MPC 8245内部的中断,其处理过程及优先级等同16级外部一样。所有外部中断源均为电平触发、低电平有效。

1.7 以太网接口

PPMC8245处理器模块1路提供10M/100M快速以太网接口,采用Intel82551(GD82551IT)芯片实现。采用RJ45头双绞线接口,Intel82551直接连接到PCI总线上。以太网协议芯片配置地址为0x80006000,通过软件可以进行以太网地址的设定。

1.8 TRACE32接口

TRACE32接口用于处理器硬件调试,利用PowerPC处理器的COP接口实现的。通过COP接口利用相应的TRACE32硬件调试设备可控制PowerPC处理器的工作并对板上功能逻辑进行测试。

TRACE32接口可完成以下功能:读/写内部存储器等资源;读/写CPU内部寄存器;单步,实时执行;硬件断点,数据断点;高级和汇编级调试;FLASH编程;提供功能强大的描述语言。

1.9 串行调试接口电路

串行调试接口电路采用1片16C552实现,44脚PQFP封装,8位数据宽度,按8位方式访问。提供2路串行通信接口,串行接口的工作时钟采用16 MHz,2路串行接口可设成RS 232/RS 422,用于与开发平台的通讯,最大速率115 Kb/s(典型为38.4 Kb/s)。16C552的寄存器基地址为0xFF000000。

1.10 地址空间分配

存储器控制器在MPC8245内部实现,系统地址空间分为4个区:局部存储器,PCI存储器空间,PCI I/O空间,FLASH存储器空间。MPC8245内部的存储控制器实现对所有空间的控制访问。系统硬件资源分配见表2。

表2 系统硬件资源分配

1.11 PMC接口

PPMC8245模块作为可以广泛应用于嵌入式计算机的处理器模块,提供PCI总线结构,以PMC背板这种通用的连接方式快速构建起系统的应用,本模块设计成可以做PMC处理机背板,也可以做PMC处理机基板,PMC接口实现标准的PCI背板总线接口。

2 结 语

PPMC8245处理器模块作为具有PCI总线接口的Power PC处理器的典型代表,为以Power PC处理器为核心处理的嵌入式计算机系统的设计提供技术支持,该系统可配置VxWorks操作系统,并在该系统的平台上完成驱动软件和系统软件的设计。MPC8245处理器广泛应用于各类嵌入式计算机系统中,希望本文能够为嵌入式系统设计提供一定的帮助。

参考文献

[1] Freescale Semiconductor. MPC8245 integrated processor reference manual [EB/OL]. [2008?03?10].http: / /www. Freescale.com.

[2] Anon. PCI lcoal bus specification revision 2. 3 [EB/OL]. [2012?12?20]. http: / / www.docin.com/p?532005.

[3] 李贵山,陈金鹏.PCI 局部总线及其应用[M].西安:西安电子科技大学出版社,2003.

[4] 张斌峰,曹兴冈,谢涛.机载通信管理器的处理器模块设计[J].航空计算技术,2014(3):128?131.

[5] 陈海荣.基于双核Power PC处理器的高性能计算模块设计[J].计算机测量与控制,2011(11):2824?2827.

[6] 刘丽君,贺占庄,李灏.基于PowerPC的嵌入式系统硬件设计[J].计算机技术与发展,2008(2):251?252.

[7] 王旭东.基于ARM的嵌入式系统硬件设计研究[J].电子世界,2014(18):19?20.endprint