晶振电路的原理及匹配方法

孔进亮

(珠海格力电器股份有限公司 广东珠海 519070)

振荡电路是单片机系统的“脉搏”,为单片机系统提供准确的时基。如果振荡电路工作频率出现偏差,会导致计时不准,甚至通讯不能同步(特别是高速通讯)。振荡电路在单片机系统中起着至关重要的作用,本文将以晶振电路为例,介绍晶振电路的原理及其匹配方法。

1 晶振电路原理

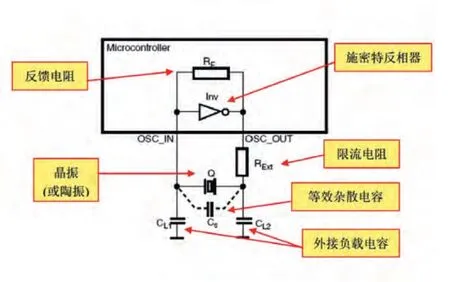

我们在单片机上使用的晶振电路(图1)称为作皮尔斯(Pierce)振荡器[1]。

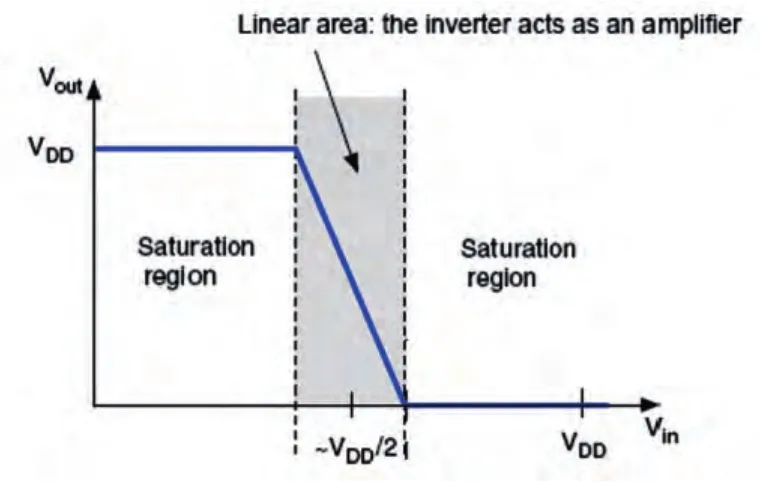

我们知道振荡电路主要由决定振荡频率的选频网络和维持振荡的正反馈放大器组成,该电路将直流电源能量转换为一定波形的交变振荡信号。在单片机内部,反相器作为为主动元件,对输入信号进行反相和放大,晶振及其负载电容(包括CL1、CL2、CS等)组成了反馈网络。由于反向器的线性区域很窄,容易出现抖动,故此加入RF引入直流负反馈,迫使反向器工作在线性区域(图2)。这时,工作在线性区的反向器就等同于反向放大器了。RF并为反向器提供直流偏置,使电路更灵敏。

反馈振荡电路正常工作必须满足三个条件:起振条件(保证接通电源后能逐步建立起振荡),平衡条件(保证进入维持等幅持续振荡的平衡状态)和稳定条件(保证平衡状态不因外界不稳定因素影响而受到破坏)。

要达到振荡状态,振荡电路幅值和相位均需要满足一定的条件,称巴克豪林(Barkhausen)判据[1]:

A(f)=|A(f)|×ejfα(f)

B(f)=|B(f)|×ejfβ(f)

︱A(f)•B(f)︱≥1

α(f)+β(f)=2nπ(n=0,1,2…)

其中:A(f)是放大器部分,给这个闭环系统提供能量以保持其振荡;B(f)是反馈通道,决定了振荡电路的频率。

振荡电路的闭环增益应大于1,并且相移为2nπ。即振荡电路要保证处于正反馈状态。

(1)起振

刚接通电源时,电路中存在各种电扰动,但只有频率为谐振角频率的分量才能通过选频网络产生较大的反馈电压。通过主动元件的放大和反馈,振荡电压振幅不断增大(正反馈)。在起振过程中,直流电源补充的能量要大于整个环路消耗的能量。

(2)平衡过程与平衡条件

因为放大器线性放大的范围是有限的,随着输出振幅增大,放大器将由放大区进入饱和区或截止区,其放大能力逐渐下降。当放大器增益下降而导致闭环增益下降到1时,振幅的增长过程将停止,振荡电路达到平衡,进入等幅振荡状态。此时,直流电源补充的能量刚好抵消整个环路消耗的能量。既电路达到振荡平衡时,振荡电路处于放大倍数为1的正反馈状态,即:

图1 单片机晶振电路

图2 反向器工作示意图[1]

︱A(f)•B(f)︱=1

α(f)+β(f)=2nπ(n=0,1,2…)

(3)平衡状态的稳定性和稳定条件

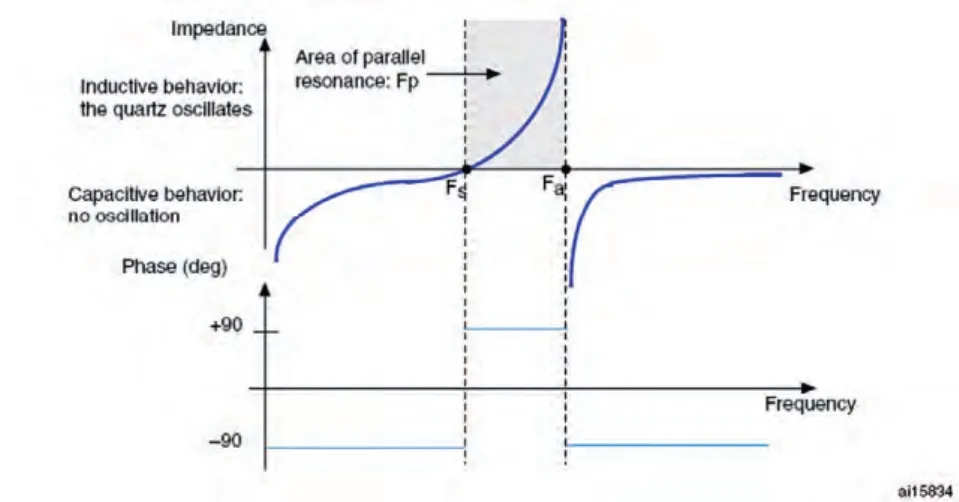

振荡电路在工作过程中,不可避免地要受到各种外界因素变化的影响,如电源电压波动、温度变化、噪声干扰等。要使振幅稳定,振荡器在其平衡点必须具有阻止振幅变化的能力。保证相位稳定,要求振荡器的相频特性在振荡频率点应具有阻止相位变化的能力。石英晶体频域特性可以满足以上要求(图4),其参数具有高度的稳定性,所以其组成的振荡电路具有稳定的振荡频率。

2 晶振电路的参数计算

2.1 晶振频率计算

石英晶体是常用的振荡电路元件。它可用图3所示模型表示。

C0:等效并接的电容(注:也叫并电容、静电电容,其值一般仅与晶振的尺寸有关)。

Lm:(动态等效电感)代表晶振机械振动的惯性。

Cm:(动态等效电容)代表晶振的弹性。

Rm:(动态等效电阻)代表对电路的损耗。

晶振的阻抗可表示为以下方程(Rm忽略不计):

Fs的是当电抗Z=0时的串联谐频率(注:Lm、Cm和Rm支路的谐振频率);Fa是当电抗Z趋于无穷大时的并联谐振频率(注:整个等效电路的谐振频率);Fs到Fa之间的区域即“并联谐振区”(图4中的阴影部分),该区域是晶振电路的正常工作区域。在此区域晶振呈电感特性,在电路中产生180°的相移(与反向器的180°相移叠加,产生360°的相移,而符合正反馈的相位)。其频率FP(又称FL,负载频率)表达式如下:

从公式(4)可知,可以通过调节负载电容CL来微调振荡器的频率,故此晶振制造商在规格书中会给出外部负载电容CL的值。调整CL值,可以使晶振晶体振荡时达到其标称频率。以8MHz晶振参数为例(如表1),通过表达式(2)、(3)和(4),我们可以计算出该晶振的Fs、Fa、FP:

Fs=7988768Hz,Fa=8008102Hz;如果该晶振的CL为10pF,则其振荡频率为:FP=7995695Hz。

要使其达到准确的标称振荡频率8MHz,则CL应该为4.02pF。

图3 石英晶体模型[1]

图4 石英晶振的频域电抗特性[1]

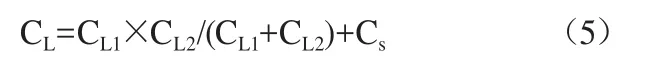

2.2 负载电容CL计算

CL值取决于外部电容器CL1和CL2,和电路板上的杂散电容Cs。外部电容器CL1和CL2可用来调整CL,使之达到晶振制造商的标称值。但杂散电容Cs与芯片的引脚、焊盘、封装引脚、印刷电路板等均有关系,无法计算,一般按5pF估算。

CL的公式如下:

例如,如果CL=15pF,假设Cs= 5pF,根据公式(6)计算得CL1=CL2= 20pF ;

图5 使用感应探头测量频率

图6 负性阻抗测量和计算

2.3 增益裕量计算

振荡电路的增益裕量决定了振荡电路是否能够正常起振:

(注:margin,即裕量)

gm:主动元件(单片机内部的反向器)的跨导,此参数取决于单片机内部电路。

gmcrit(注:gmcrit,即gm critical):取决于晶振的参数。

若CL1=CL2、晶振的CL将与制造商给定的值相同,则gmcrit的计算公式:

ESR:晶振的等效串联电阻

基于振荡电路设计的理论[1],单片机内部反向器的跨导(gm)必须满足:gm>gmcrit。而为保证可靠的起振,gm应达到gmcrit的5倍以上,即gainmargin最小值一般设为5。

例如,有如下参数的石英晶体,并且已知微控制器的振荡器部分gm等于25mA/V。

石英晶体参数:频率=8MHz,C0=7pF,CL=10pF,ESR=80Ω。

由于107>>5,因此晶振将正常起振。

如果不能满足增益裕量起振条件(即增益裕量Gainmargin小于5,晶振将无法正常起振),应尝试使用ESR较低或CL较低的晶振。

2.4 驱动功率DL及外部限流电阻RExt计算

晶振的功耗必须限制在某一范围内,超过这个值时,晶振会受到损害,出现电极劣化、频偏、寿命衰减。

驱动级别计算公式:

其中,ESR是指晶振的等效串联电阻:

IQ是流过晶振电流的均方根有效值,使用示波器可观测到其波形为正弦波。电流值可使用峰-峰值(IPP)。

可以调节外部限流电阻,使流过晶振的电流不超过IQMAX均方根有效值。

IQMAX均方根有效值表达式如下:

流过晶振的电流IPP不应超过IQMAXPP(使用峰-峰值表示),IQMAXPP表达式如下:

当IQ超过IQmaxPP时,必需要增加RExt,并且将RExt加入到ESR中重新计算IQmax。

2.5 外部电阻RExt计算

图7 在晶振引脚(XOUT端)上串入可调电阻VR

图8 使用小电流探头测试晶振电流

RExt的作用是限制晶振的驱动功率,并且它与CL2组成一个低通滤波器,以确保振荡器的起振点在基频上,从而避免3次、5次、7次谐波频率。如果晶振的功耗超过额定值,则外部电阻RExt是必需的;如果晶振的功耗小于额定值,RExt可取0Ω。

RExt值计算如下:

表1 8MHz晶振参数

表2 晶振在电路板中的频率偏差

输入条件:振荡器频率F=8MHz;CL2= 15pF

得到:RExt= 1326Ω

如果RExt值太小,晶振上可能会承担太多的功耗。如果RExt值太大,振荡器起振条件不满足从而无法正常工作。计算完RExt值后要重新计算Gain margin的值,以确保RExt值对起振条件没有影响。例如,RExt值的值需要加入到ESR中参与gmcrit的计算,同时要保证:

2.6 启动时间

启动时间是指振荡器启动并达到稳定所需的时间。这个时间受外部CL1和CL2电容影响,同时它随着晶振频率的增加而减少。不同种类的晶振对启动时间影响也很大。频率为MHz级的晶振的启动时间是毫秒级的。32kHz的晶振的启动时间一般要1~5秒。

2.7 牵引度(Pullability)

晶振的牵引度(也叫可调度)是指工作在正常并联谐振区的晶振频率的变化率。这也用于衡量随负载电容变化而导致的频率变化,负载电容的减少会导致频率的增加,反之负载电容的增加会导致频率的减小。晶振的牵引度表达式如下:

3 晶振电路的评估及实际测试

从公式(5)和公式(7)发现,CS参数一般只能估算,gm是单片机内部电路的参数,厂家没有公开,通常难以计算。我们需要用其他方法对电路进行评估。

在正反馈的振荡电路中,我们将消耗能量的电路部分等效为负载,而提供能量的主动元件(放大器)部分,等效为源负阻器件,产生“负电阻”。

振荡电路的起振条件为负阻绝对值大于正阻。振荡稳定后负阻绝对值等于内阻。因此负性阻抗是一个衡量振荡电路稳定性很重要的参数。而对晶振电路的增益裕量的评估转换为对负性阻抗的测量。

对晶振电路的参数评估测试如下:

3.1 频率测量

(1)晶振的单体参数测试,可以使用晶振参数测试仪;

(2)晶振电路频率实测:通过频谱仪和数字频率计实测晶振在电路中的频率(图5);

(3)算出晶振在电路板中的频率偏差△f/f0(表2)。

根据不同的应用场合,一般要求频率偏差为±30ppm~±50ppm不等;如果是实时钟(RTC)的应用,则要求达到0ppm~10ppm。以实时钟为例,起使用的是32.768kHz晶振,在实际电路存在10ppm的偏差,每天产生误差达到0.864秒。可见振荡电路中的频率偏差对时间精度有影响。

3.2 负性阻抗测量

负性阻抗(-R),前面已有介绍,其测量方法如下:

(1)晶振电路中串入可调电阻VR,不断增大VR直到晶振停止振荡。重新调节VR,直到电路刚好能起振。取出VR,用万用表测量此时VR的阻值。如图6、7。

(2)计算负性阻抗:N.R.= VR+RL。要求│N.R.│> (5~10)×RL(注:RL即晶振的ESR,见公式(11))

3.3 驱动功率测量

按图7在晶振引脚上串入电流探头,测量流过晶振的电流值,按2.4、2.5(公式(10)~(14))计算驱动功率和限流电阻。

3.4 晶振波形测试及启动时间测试

一般的示波器探头附加电容达到8~15pF,对于晶振电路来说,引入的附加电容太大,已经影响电路的工作。故此对晶振波形测试需要使用主动式FET探头,探头附加电容小于1pF,测试时可以减少对晶振电路的影响。根据测试的波形评估实际测试波形是否出现削顶、削底、振幅不足、振荡不稳定等异常情况。

3.5 晶振电路参数调整

当前述1~4项测试出的参数出现异常时,则需要对电路参数进行调整。

4 结束语

单片机系统中,晶振电路的可靠性、稳定性和准确性,对系统运行有着重要的影响。在对时间精度要求很高的应用中,晶体电路的匹配性能测试和调整是必不可少的环节。希望通过本文使大家的对晶振电路有更深刻的理解,电路设计水平进一步提升。

[1] ST,AN2867应用文档《ST微控制器振荡器电路设计指南》,2009

[2] 沈伟慈,《通信电路》(第二版),西安:西安电子科技大学出版社,2007

[3] [日]稻叶保,《振荡电路的设计与应用》,北京:科学出版社,2004

[4] HOLTEK,HA0075s《Holtek单片机复位电路和振荡电路应用》

[5] HOLTEK,HA0301T《HT32系列微控制器晶振& ADC设计的注意事项及PCB 布局指南》

[6] Microchip,01155a_cn《Microchip时钟晶振的实时校准》

[7] Seraphim,《石英晶体振荡电路之回路分析介绍》

[8] 赵毅强,杨栋,《低功耗低频快速起振电路的设计》,北京工业大学学报,2012

[9] 刘惩,李冰,《用于时钟芯片的Pierce晶体振荡器设计》,半导体技术第33卷第1期,2008

[10] 罗一平,《三点式振荡器中负阻特性和反馈特性的等价性》,浙江师大学报(自然科学版)第19卷第2期,1996