高速数字电路的串扰问题分析与仿真

摘要:在当今的高速数字电路设计过程中,信号完整性问题的研究已经成为不容忽视的重要环节。而串扰问题则是影响信号完整性的重要因素,因此在电路的设计初期就要充分利用EDA软件进行仿真,充分考虑可能出现的问题,及时发现及时解决。文中给出了串扰在Altium Designer中的仿真波形,从仿真结果可以清楚的看到采取不同的解决方法,串扰噪声改善的效果不一样,因此在实际工程中要根据电路设计的具体需求采用合理的最佳解决方案。

关键词:串扰;Altium Designer;信号完整性

中图分类号:TN41 文献标识码:A 文章编号:1009-3044(2015)22-0132-02

1 概述

高速数字电路系统中,电路功能越来越复杂,而导致的信号频率的升高,布局布线密度的加大,PCB板层数的增多等诸多因素,都会引起各种信号完整性问题。在这种情况下,电路设计的关键因素不仅仅是信号的互连了,如何解决好信号完整性问题就显得更加重要了。信号完整性是指信号通过信号线传输后仍能保持完好,保持其正确的逻辑功能功能和时序而未受到损伤的一种特性[1]。在各种信号完整性问题中串扰现象是普遍存在,且对电路影响比较大的。

2 串扰产生的原因

在信号频率越来越高的数字电路设计中,经常会有串扰现象的产生。信号串扰(Cross-talk)是在电气上没有连接的信号线之间,产生的电磁耦合现象,一条信号线上的电压或电流可以通过互感和互容耦合到相邻的信号线上[2],即对相邻的传输线产生了不期望的干扰噪声。这个串扰噪声从攻击对象上以耦合电压或耦合电流的形式,交叉耦合到牺牲对象上,表现在只要有一信号线上有信号流通,PCB板上与这条信号线相邻的其他网络上就会感应出耦合电压或电流信号。

如图1,设A点的信号为干扰源,则D点的接收器就为被干扰对象,A、B之间的传输线L就是攻击线,则C、D之间的传输线P就是牺牲线。随着PCB板上信号线间的几何距离越来越小,加之时钟速度的不断升高,这种耦合越剧加大,信号间的干扰噪声就会更加明显。

当攻击线上有变化的信号从源端传向负载端时,攻击线上会产生一个时变电磁场,牺牲线将包括在这个电磁场里面,变化的电磁场在牺牲线上就会产生感应的电信号。这个感应电信号会分别向牺牲网络线的近端和远端两个方向传播,如图2,朝近端传播的串扰称为近端串扰;另一个向远端传播的串扰称为远端串扰,。

串扰都产生于信号变化的一瞬间,远端串扰是攻击源对牺牲源的接收端产生的影响,表现为一个尖端脉冲,持续时间等于攻击信号的跳变时间tr[3,4],但对于远端串扰,产生的容性串扰和感性串扰两者的方向相反长度相同,基本上是可以相互抵消的。

而近端串扰是攻击源对牺牲源的发送端产生的干扰,与干扰信号的方向相反,近端串扰的容性和感性部分具有相同的极性,并与干扰信号的极性相同,脉冲宽度等于两倍的串扰线的延时2tr,因此它们相互叠加而不是抵消,表现为一个长脉冲。

3 串扰噪声的抑制方法

串扰在高速数字系统中存在是非常普遍的,而且对电路性能的影响也很大,降低串扰最有效的是减少干扰源与被干扰线之间的耦合度,增加信号走线间的距离,减小耦合长度[5]。但是对于当今高速系统的设计,PCB板的密度已经越来越大,仅靠增加信号线间的距离改善串扰已经基本达不到要求了。因此主要可以从下面几个方面考虑改善:

1)尽可能地减少相邻网络线间的平行长度,如果条件允许最好能把相互间可能产生影响的传输线放在不同层间走线,而且相邻两信号层的走线方向尽可能垂直。

2)通过端接,如RC交流端接、上下拉电阻、串联端接等各种端接方法,使传输线两端阻抗与传输线阻抗匹配,可以大大减小串扰的幅度。

3)对于目前密度越来越大的多层PCB板来说,信号层与电源层之间都是用电介质填充的,这个电介质层的厚度直接影响着传输线特征阻抗,在满足特征阻抗的条件下,应使电介质层尽可能薄,这样加大了传输线与参考平面间的耦合度,也就相当于减少了与相邻传输线的耦合。因此减小层间介质厚度,同样可以改善串扰现象。

4)多层PCB板都包含若干个信号层和电源层,一般是通过信号层和电源层叠放顺序来构成标准的微带传输线和带状传输线。对于同样厚度的电介质层,带状传输线的串扰要小于微带传输线的串扰[5]。因此在高速系统中,尽可能使用带状传输线进行PCB布线。

4 基于Atium Designer10的串扰仿真分析

下面就以一个某FPGA电路为例来分析一下串扰抑制的仿真效果。在Atium Designer10中,做好一切准备工作之后,在PCB编辑器中,执行【tools】/【signal integrity】命令,信号完整性分析窗口,如图3所示。

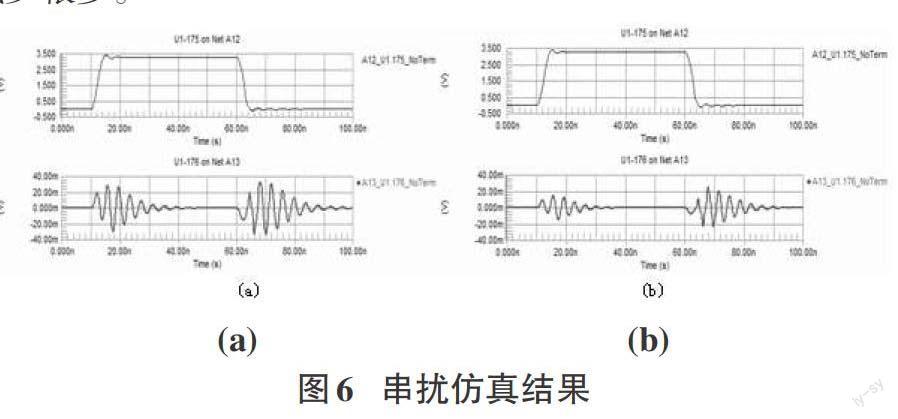

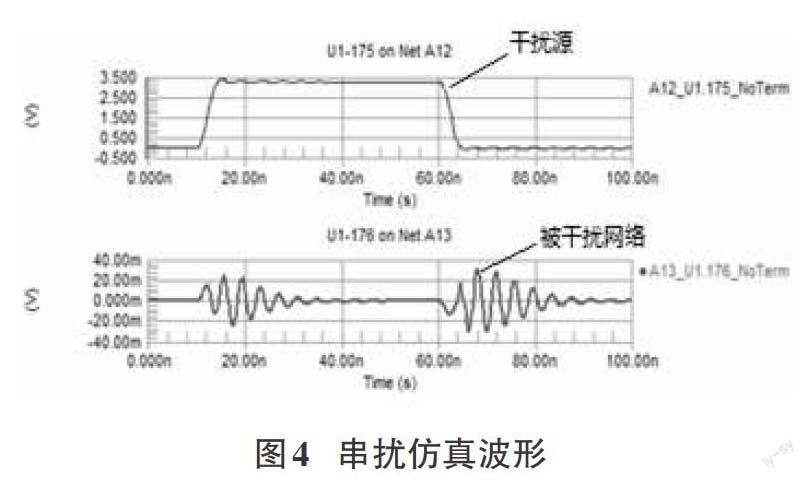

对电路中的产生干扰噪声可能性比较的网络进行重点分析,选中待分析的网络标签,如“A12、A13”等等,点击向右箭头或者双击导入到窗口右侧待分析列表中,在圖3分析窗口右侧Net下,选中A12,点击右键设置A12为攻击源,单击窗口右下角的Crosstalk Waveforms命令,进行串扰情况分析,没有采取任何抑制措施的串扰波形如图4,可以看出在牺牲信号线A13上存在着很大串扰噪声,最大串扰噪声幅度可达30mv左右。

在图3信号完整性分析窗口右侧可以选择各种端接策略,如串联端接、RC交流端接、上拉或下拉电阻端接、二极管端接等等,每种端接方式可以设置不同的端接阻抗,来减小串扰所带来的影响,图5为采用各种端接后串扰仿真结果,每种端接方式分别选了两种不同的阻抗。从波形上可以看出,(a)、(b)两种端接方式对串扰几乎起不到任何抑制作用,甚至有的更糟了,(c)、(d)两种端接方式对串扰噪声都有不同程度的抑制,即使同一种端接方式,阻抗不同,抑制噪声的效果也是不一样的。如:RC交流端接,电阻选择170欧,电容4nF,串扰噪声最大值从30mv可以降低到低于20mv。在实际工程中,设计者可以参考波形分析,根据实际噪声容限的要求[3,6]信号摆幅小于的5%原则,综合多方面因素考虑选择合适的阻抗值和合理的端接方式。

5 结束语

串扰噪声对高速电路系统性能的影响不容忽视,电路能否长期稳定的工作,在很大程度上取决于PCB设计的合理性。对目前要求都越来越高的电路系统,设计初期都必须要综合考虑各方面因素,合理布局布线,经过严密的仿真验证,及时发现问题及时解决,降低开发成本,缩短产品上市时间。

参考文献:

[1] 王渊峰, 戴旭辉. Altium Designer10电路设计标准教程[M]. 科学出版社, 2013:253-280.

[2] 陈伟, 黄秋元. 高速电路信号完整性分析与设计[M]. 北京: 电子工业出版社, 2009:64-97.

[3] 崔玉美. 基于Protel2004的信号完整性分析与研究[J]. 实验室研究与探索, 2010(11):38-40.

[4] 曾铮, 郑建宏. 高速PCB板设计中的串扰问题和抑制方法[J]. 电子设计应用, 2006(4):81-84.

[5] 陈思思. 信号完整性中的串扰分析[J]. 武汉理工大学学报, 2005(10):17-20.

[6] 高海宾, 辛文, 胡仁喜等. Altium Designer10从入门到精通[M]. 北京: 机械工业出版社, 2014:234-246.