弹载小型化高速信号处理机设计方案*

庄跃迁

(中国西南电子技术研究所,成都610036)

1 引言

随着弹载装备的不断快速发展,尤其是对弹载装备赋予的战技指标要求越来越高的情况下,针对基于弹载平台研发的信号处理机的要求也在不断提高。与地面、舰载、机载等产品的不同之处在于,弹载产品由于其特殊的功能指标及环境条件,作为其核心单机的信号处理机必须满足高处理性能、小型化等要求,同时兼顾功耗、散热、可靠性、成本和模块化等因素。

传统的弹载信号处理机的核心处理器多采用几百MHz的单核或双核定/浮点处理器,而目前,弹载信号处理机对数字信号处理器的处理性能要求已经达到数十Gflop到数百Gflop,多核心浮点处理器的应用已经势在必行。弹载信号处理机对数据传输要求也达到了数Gbit/s到数十Gbit/s,并且通常弹载信号处理机都具有非常严苛的体积要求。因此,如何设计高速高密度大容量处理能力的弹载处理机,实现高效的多核心并行处理、高速的大规模数据传输,是弹载信号处理机亟需面对和解决的问题。

目前,弹载装备已经涵盖了雷达导引头、电子干扰机、电子侦察、通信等多个专业领域,而信号处理机作为不同领域的通用核心设备,其研发将更加具有重要意义。设计满足工程化需求的弹载小型化高速信号处理机已经迫在眉睫。本文对弹载小型化高速信号处理机的设计方案、模块组成进行了介绍,并重点分析了处理机设计中解决的关键技术。

2 处理机方案设计

典型的弹载信号处理机需要完成包括信号采样、信号预处理、信号处理、数据处理、接口控制、模块管理在内的多项功能。其中,信号采样完成对多路中频宽带模拟信号的模数转换;信号预处理完成对中频信号的数字下变频、滤波等功能;信号处理完成信号处理机的核心算法;数据处理完成对信号处理结果的后处理工作;接口控制负责信号处理机内部模块之间的接口和信号处理机对外的接口的管理及控制;模块管理功能实现对信号处理机各模块状态的实时检测。

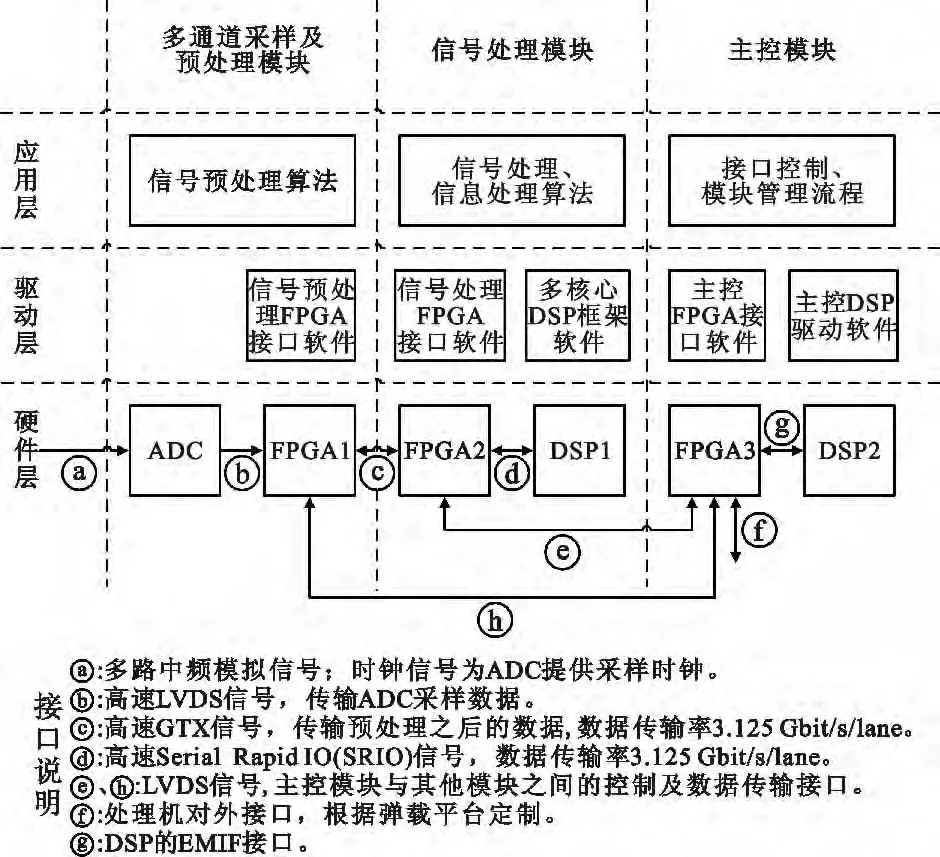

图1是弹载小型化高速信号处理机的设计框图。根据对弹载处理机功能要求的分析,将弹载处理机划分为3个主要模块:多通道采样及预处理模块、信号处理模块、主控模块。多通道采样及预处理模块完成对信号采样和信号预处理功能;信号处理模块完成信号处理和数据处理功能;主控模块完成接口控制和模块管理功能。各模块之间通过底板互联。

图1 处理机设计框图Fig.1 Block diagram of computer design

同时,在处理机设计时,为提高模块的可复用性能,降低开发难度,提高研发效率,将处理机设计划分为三个层次,从下至上分别是硬件层、驱动层和应用层。

2.1 多通道采样及预处理模块

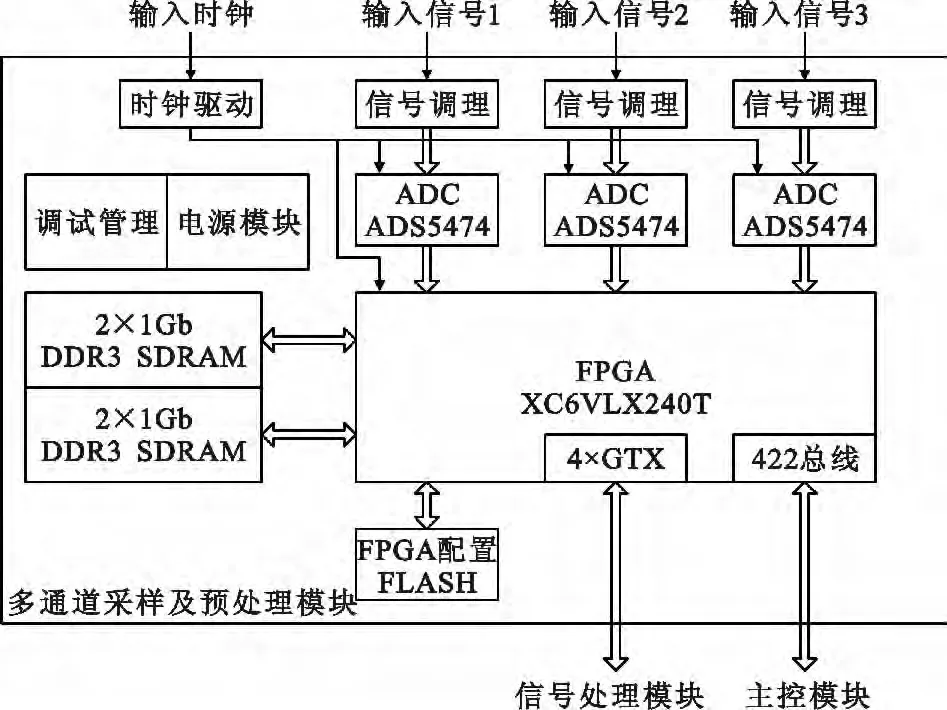

多通道采样及预处理模块采用ADC+FPGA的构架方式,图2是模块的设计框图。

图2 多通道采样及预处理模块设计框图Fig.2 Block diagram of the multi- channel sampling and preprocessing module

ADC采用TI公司的产品ADS5474,其输入带宽最高可达1.4 GHz,转换速率最大可达400 Msample/s,采样位宽为14 bit。ADC采样电路设计要求高质量低相位噪声的采样时钟,时钟信号的孔径抖动对ADC的性能影响较大,因此选用ADCLK854时钟分配器将单端时钟转换为差分时钟,该驱动器具有极低的100 fs的抖动时间。

FPGA采用Xilinx公司的XC6VLX240T,其配置FLASH为Platform flash XL。FPGA的GTX接口是一种高速串行接口,在方案中设计为3.125 Gbit/s波特率的全双工串行收发,提供8B/10B、用户定义FPGA逻辑或无编码选项,收发器可以支持多种协议。FPGA外挂4 Gbit DDR3 SDRAM存储器。

在驱动层,信号预处理FPGA接口软件由时钟管理模块、ADC接口管理模块、DDR存储器控制模块、FLASH存储器控制模块、GTX接口管理模块、同步信号管理模块、RS422总线管理模块、CAN总线管理模块、I/O管理模块等组成。

在应用层,FPGA完成对中频模拟信号的数字下变频和滤波等功能。应用软件不是本文讨论重点,在此处不再赘述。

2.2 信号处理模块

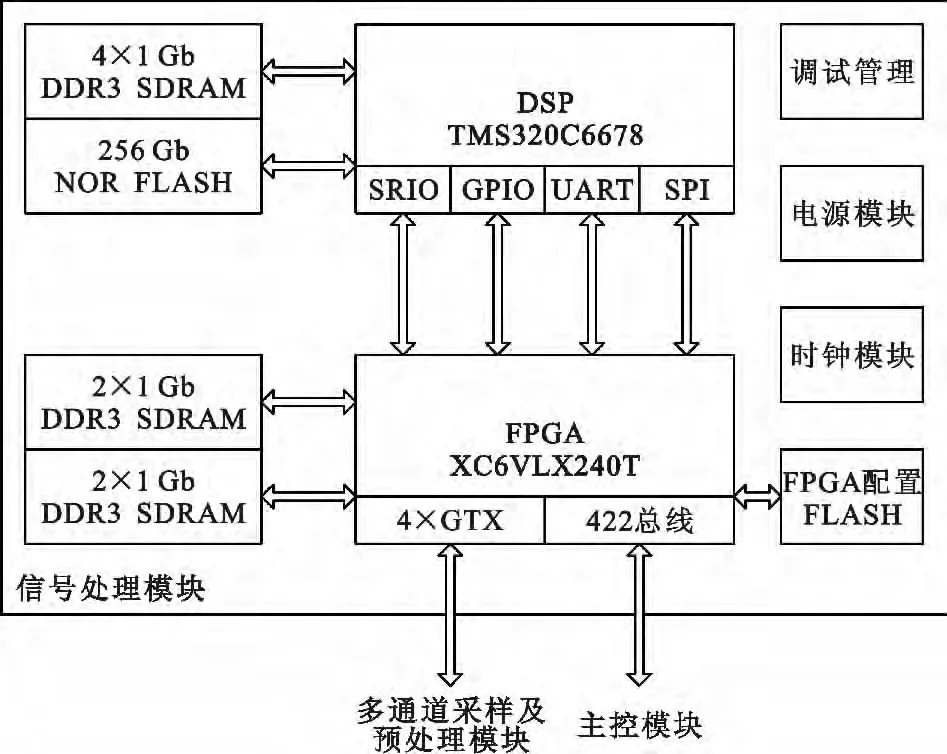

图3是信号处理模块的设计框图。信号处理模块采用FPGA+DSP的构架方式,其中FPGA同样采用Xilinx公司的XC6VLX240T,DSP采用TI公司的TMS320C6678多核心DSP处理器。DSP外挂4片128 MByte的 DDR3存储器、1片32 MByte的 Nor Flash存储器,并通过 SRIO、GPIO、URAT、SPI与 FPGA进行连接。时钟缓冲器采用ON公司的NB6N14SMNG,将晶振提供的125 MHz时钟多路分发到FPGA和DSP,作为GTX和SRIO高速串行总线的工作时钟。

图3 信号处理模块设计框图Fig.3 Block diagram of signal processing module

在驱动层,信号处理FPGA接口软件与信号预处理FPGA接口软件类似,只是增加了SRIO接口管理模块,同时裁剪了ADC接口管理模块。

为解决多核心协同工作问题并提高DSP的工作效率,设计了多核心DSP框架软件。软件从下至上包含了BSP板级支持包、DSP管理框架、API用户界面三个部分,BSP板级支持包根据TI公司提供的底层驱动函数库进行封装;DSP管理框架包括了多核管理、资源管理、存储管理、数据通信等部分,实现了多核心之间的行为同步、资源共享,提高了存储器的访问效率,并有效管理了DSP片内外的数据传输;API用户界面对下层的DSP管理框架进行封装,为上层用户程序提供简洁的API函数,使用户在不需要了解底层硬件的情况下进行调用。

在应用层,FPGA和DSP协同完成信号处理、数据处理算法的实现。

2.3 主控模块

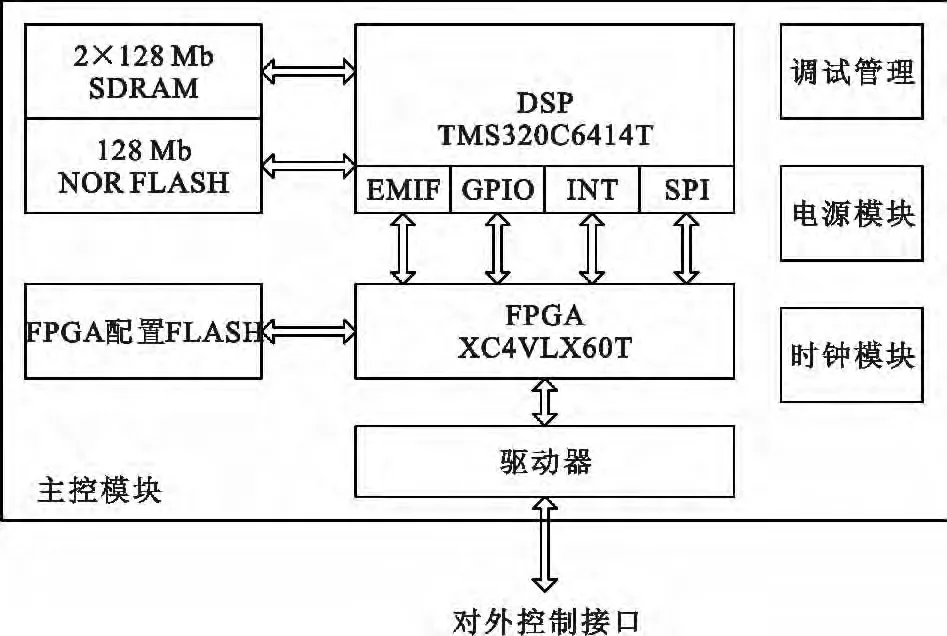

主控模块主要负责处理机接口控制和模块管理,通过DSP实现流程管理,通过FPGA实现接口通信。DSP采用TI公司的TMS320C6414T处理器,外挂2片16 MByte SDRAM、1片16 MByte Nor Flash,并通过EMIF总线以及GPIO、INT(中断信号4个)与FPGA进行连接。FPGA采用 XILINX公司的XC4VLX60 FPGA及相应的FLASH配置芯片XCF32PVO48C。主控模块的设计框图如图4所示。

图4 主控模块设计框图Fig.4 Block diagram of main control module

在驱动层,主控FPGA接口软件由时钟管理模块、同步RS422管理、异步RS422管理、CAN总线管理、SPI总线管理、LVDS总线管理、I2C总线管理、EMIF总线管理、看门狗复位、自检及健康管理等组成。主控DSP驱动软件由CPU初始化函数、中断初始化函数、片上 PLL驱动函数、EMIF驱动函数、SDRAM驱动函数、GPIO驱动函数、SPI驱动函数、Timers驱动函数、DMA驱动函数等组成。

在应用层主控模块将实现接口控制和模块管理的整个工作流程。

3 处理机关键技术分析

3.1 高速高密度小型化电路设计技术

受限于弹载平台,弹载处理机通常具有非常严苛的结构要求。但与此同时,对弹载处理机处理性能的要求却越来越高。由此带来的就是高速高密度电路设计、小型化、散热等问题。

(1)高速高密度电路仿真技术

传统的低频电路设计通常依赖于厂商提供的器件资料和研发人员自身的设计经验,以规避可能出现的电路设计问题和电磁兼容问题。

弹载处理机的信号处理模块由高性能的FPGA、DSP等处理芯片及相关电路组成,其中FPGA工作频率为300 MHz,DSP 主频最高为1.25 GHz,GTX和SRIO总线的数据率更是高达3.125 Gbit/s。此外,多通道采样及预处理模块由复杂的模拟采样电路和高速数字电路组成,设计难度较大。同时,弹载处理机对模块体积也有非常严苛的要求。因此,只有采用有效的电路仿真手段,在设计阶段进行信号完整性仿真,预先发现可能存在的电磁兼容问题,才能提高高速高密度电路设计的成功率,降低设计成本并缩短开发周期[1]。在弹载处理机设计过程中,采用Candence电路设计工具进行高速数模混合电路仿真,解决了电源纹波对时钟信号的影响和信号线间串扰两个关键技术问题。

通过仿真发现,由于DSP核电压滤波电容的寄生电感(ESL)和寄生电阻(ESR)值较大,导致其对电源纹波的滤除性能较差,使DSP的内部锁相环无法稳定工作。通过选用ESL和ESR较小的陶瓷电容,可有效滤除电源纹波,降低对时钟信号的干扰,保证DSP的正常工作。经仿真后发现电源纹波降低了一个数量级。

在完成信号处理模块的PCB布线之后,通过仿真发现某控制信号受邻近时钟信号干扰较为严重。在对该控制信号附近进行铺地处理后再次仿真发现干扰已降低到可忍受程度。

(2)采样一致性技术

高速多通道采样带来了信号幅度一致性和相位一致性的问题。对于幅度一致性要求,通过在ADC之前增加线性保持和放大电路实现对信号的调理。采用宽带运算放大器完成ADC变换前信号的放大与保持,可降低在宽带情况下不同频率信号的畸变,同时减少多路信号之间的幅度差。运算放大器在系统允许的条件下虽然会带来一定的插损,但相对变压器组而言对不同频率信号间的幅度一致性更好,不同通道间的延迟也更加稳定一致。对相位一致性要求,则选择具有相位一致性调整功能的ADC,通过FPGA实现对ADC采样信号相位的调整,实现多路信号的同步。

(3)散热技术

高密度高性能电路带来的最严峻的问题就是散热。以TMS320C6678为核心的处理电路,其工作温度和功耗成为相互加速的因子。如果不采取有效的散热措施,上电后DSP的温度将会迅速升高,最后发生雪崩效应,导致DSP功耗过高,工作温度超过芯片结温,轻则出现程序跑飞的情况,严重将会损坏硬件电路。而弹载情况下通常是不能采用强制对流的方式进行散热的,因此必须通过结构仿真,设计具有良好散热效果的冷板及机箱,才能保证处理机的正常工作。通过仿真表明,采用某钨基合金材料制作的冷板,具有较好的导冷散热效果,可保证DSP正常工作。

3.2 高速浮点DSP多核心协同工作技术

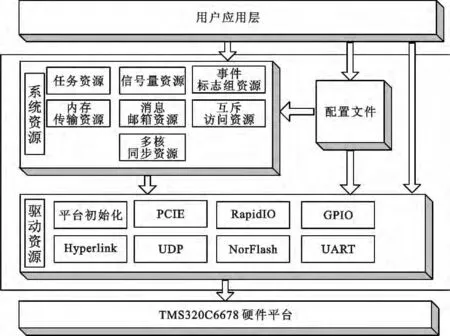

TMS320C6678是业界目前最高性能的定、浮点DSP,它的出现虽然带来处理能力的提高,但是由于体系结构复杂,给软件设计人员带来很大负担:首先必须花时间了解复杂的芯片体系结构,然后花大量的时间精力去实现多核间的行为同步、资源同步、数据通信和各种底层驱动(平台初始化、PCIE、RapidIO、Hyperlink、UDP、NorFlash、GPIO、UART)等功能,最后才能专注于自己的算法或应用开发。为了将研发人员从底层驱动、多核体系结构中解放出来,将主要精力花在应用开发或算法实现上,本处理机设计方案提出C6678框架软件的设计理念,如图5所示。

图5 TMS320C6678框架软件Fig.5 Framework software of TMS320C6678

为满足实时性要求,C6678框架软件不采用任何操作系统,但为多核心DSP开发引入嵌入式操作系统[2-4]的设计理念,使应用软件开发人员在编写应用软件(或者具体算法)时,无需考虑多核的体系架构,只需将软件或算法科学地划分为多个任务,然后调用本框架软件的提供的系统资源(比如任务资源、信号量资源、事件标志组资源、多核同步资源、互斥访问资源、消息邮箱资源、内存传输资源)、驱动资源(平台初始化、PCIE、RapidIO、Hyperlink、UDP、NorFlash、GPIO、UART)和平台配置文件,即可在应用层快速搭建所需环境,提高应用软件或算法的编写效率。

C6678框架软件主要集成了多核间同步与通信、常用底层驱动和软件平台配置文件,并通过大量测试确保此平台的稳定性。在用户设计一个复杂系统时,使用此平台将大大提高效率和可靠性。

4 测试情况

弹载处理机的性能指标主要体现在处理性能和数据传输两个方面。

表1是针对某SAR图像处理算法,分别采用传统弹载处理机和弹载小型化高速信号处理机,完成信号处理及数据传输的耗时统计。

表1 耗时统计Table1 Time consuming statistics ms

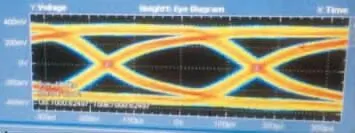

图6所示是采用高性能示波器对模块间高速GTX总线进行测试的结果,数据速率为3.125 Gbit/s。由图可见,眼图质量很好,数据传输的校验结果也表明误码率低于10-12。

图6 GTX总线测试结果Fig.6 Test result of GTX bus

多项测试表明,弹载小型化高速信号处理机的处理性能、数据传输能力均比传统弹载信号处理机有很大提高,可满足弹载多领域的项目需求。

5 结束语

弹载小型化高速信号处理机具有高性能的采样和信号处理能力、高速超大容量的数据传输能力,经过性能指标的测试和工程项目的验证,可满足装备的需求。

多功能、多任务、高性能、微小型化、低功耗将是未来弹载信号处理机的发展方向。进一步的研究重点将包括基于多通道采样的阵列信号处理技术、高速光纤网络传输技术等,以满足不断提升的弹载处理机的性能需求。

[1]Montrose M.电磁兼容的印制板电路板设计[M].吕英华,于学萍,张金玲,等,译.北京:机械工业出版社,2013.Montrose M.Printed Circuit Board Degisn Techniques for EMC Compliance[M].Translated by LYU Yinghua,YU Xueping,ZHANG Jinling,et al.Beijing:Mechanical Industry Press of China,2013.(in Chinese)

[2]周本海,乔建忠,林树宽.基于多核处理器的动态共享缓存分配算法[J].东北大学学报(自然科学版),2011,32(1):44 -47.ZHOU Benhai,QIAO Jianzhong,LIN Shukuan.Research on the Dynamic Allocation Algorithmof Shared Cache for Multi- core Processor[J].Journal of Northeastern University(Natural Science),2011,32(1):44 -47.(in Chinese)

[3]张骏,樊晓桠,刘松鹤.多核、多线程处理器的低功耗设计技术研究[J].计算机科学,2007,34(10):301 -305.ZHANG Jun,FAN Xiaoya,LIU Songhe.Research of Low Power Degisn Techniques for Multi-Core and Multithreading Microprocessor[J].Computer Science,2007,34(10):301 -305.(in Chinese)

[4]徐帆,沈立,王志英.基于多核平台的多线程动态优化框架[J].计算机工程与科学,2011,33(5):48-53.XU Fan,SHEN Li,WANG Zhiying.A Dynamic Optimization Framework for Multi-Threads Based on Multi-Core Platforms[J].ComputerEngineering & Science,2011,33(5):48 -53.(in Chinese)