基于FPGA的ARINC429协议设计

曾锋 冯宇

摘 要: 针对传统ARINC429总线电路设计中采用的协议芯片的方式有扩展性差,占面积大的问题,提出一种基于FPGA的ARINC429协议电路设计。协议电路的设计分为接收电路设计和发送电路设计两部分,并且对电路进行了仿真和验证。协议电路可以通过配置模块的I/O口,方便地对ARINC429总线通信的波特率、奇偶校验等参数进行设置。该协议采用的独立的收/发电路设计可以很方便地进行ARINC429总线通道的扩展。除FPGA外,电路外围只需要使用总线驱动电路,从而大大地减少了电路面积。该协议电路设计通过严格的测试,已经应用在实际的产品中。

关键词: FPGA; ARINC429总线; 模块配置; 电路设计

中图分类号: TN911?34 文献标识码: A 文章编号: 1004?373X(2015)18?0092?03

Abstract: For the design way based on ARINC429 protocol chip has poor expansibility and big occupied area in the traditional circuit design of ARINC429 bus, a ARINC429 protocol circuit design base on FPGA is proposed. The design of protocol circuit is divided into two parts (receiving circuit design and transmitting circuit design). The circuit was simulated and verified. Baud rate, parity check parameter and other parameters of the ARINC429 bus communication can be set easily by configuring the I/O interfaces of modules. The extension of ARINC429 bus channel can be realized conveniently by the independent transmitting circuit design and receiving circuit design adopted by this protocol. In addition to FPGA, the peripheral circuit only need to use the bus driver circuit, by which the circuit area is greatly reduced. The circuit design of this protocol has passed the strict test and was used in the products.

Keywords: FPGA; ARINC429 bus; module configuration; circuit design

ARINC429总线是航空电子系统中最常用的通信总线之一。ARINC429总线电路是通过ARINC429总线接收/发送协议芯片加驱动芯片来实现的。协议芯片占用板卡面积,且每个协议芯片接收/发送通道数量固定,当电路需要多个ARINC429总线通道时,硬件面积占用较大。随着FPGA的大量应用,可通过在有FPGA的系统中,通过FPGA来实现ARINC429总线协议[1]。在FPGA中,通过设计通用的、可配置的ARINC429协议,可以方便地扩展ARINC429通信通道,减少ARINC429协议芯片的使用,缩小产品尺寸,并且通过配置ARINC429总线,可方便适用于各种要求的ARINC429通信。

1 方案设计

1.1 方案概述

本方案中基于FPGA的ARINC429协议分为两部分:发送部分和接收部分。这两部分协议独立工作,接收协议和发送协议都可以通过对模块I/O的配置,实现不同的波特率、奇偶校验,数据格式等功能的设置。

由于ARINC429总线由两条差分线构成,总线上的电平范围为-5~5 V,见图1的A(ARINC429),B(ARINC429)。该电平不能与FPGA直接进行接口[2],需要总线接口驱动芯片进行电平转换后才能与FPGA进行接口。对应转换后的TTL电平见图1的A(TTL),B(TTL)[3]。

利用本协议方案的ARINC429的通信电路采用FPGA加外围驱动电路的方式实现,方案见图2。其中ARINC429协议在FPGA内部实现,外围使用驱动芯片,如HI?3182和DEI?1046。ARINC429协议中每一路的收/发协议搭配上一路对应的驱动芯片,就可以成为一个独立的ARINC429收/发通道。

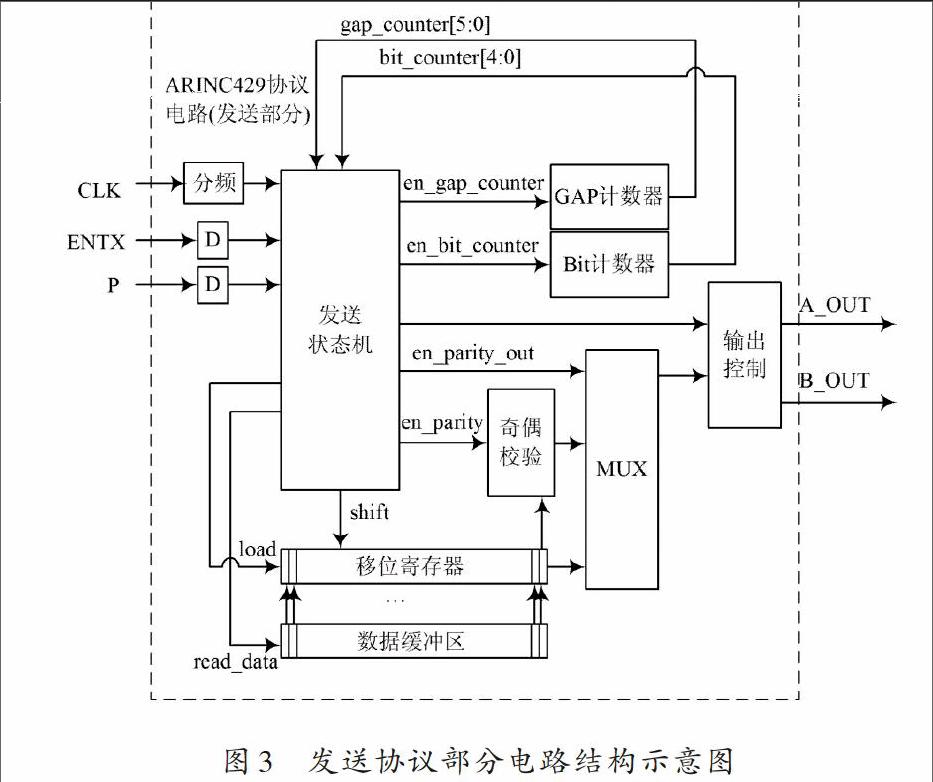

1.2 ARINC429发送部分

电路框图如图3所示,主要由发送状态机、计数器、奇偶校验、输出控制等部分构成。电路CLK使用的是25 MHz时钟,可以通过设置分频电路的分频系数,使得电路工作在不同的ARINC429总线波特率下。

信号ENTX为电路工作的使能信号,“1”为使能发送功能;信号P为奇偶校验位的选择位,默认为“1”奇校验。外部信号在进入状态机前通过D触发器进行时钟同步。发送状态机控制计数器工作,计数器的结果返回状态机作为状态机的输入控制状态机的状态跳转。其中Bit计数器为数据位的计数,Gap计数器为两个数据之间的时间间隔计数。

发送状态机是整个电路工作的核心。当状态机判断有数据需要发送时,先从数据缓冲区中取数,并存到移位寄存器中。然后根据预先分频的时钟频率逐位右移输出。当输出位为1时,A_OUT和B_OUT分别输出1和0;输出位为0时,A_OUT和B_OUT分别输出0和1。根据ARINC429的协议,每一位数据前半个周期为数据,后半个周期输出同时为0。同时,每移出一位数据,奇偶校验电路就会统计移出的“1”的个数,当移位寄存器移到最后一位的时候,发送状态机选择奇偶校验电路生成的校验位进行输出。发送完32位数据后,最后会等待4个位时的时间,即“GAP”的时间,状态机再回到初始状态。状态机状态转换图见图4。

1.3 ARINC429接收部分

接收协议电路如图5所示,主要由接收状态机、计数器和奇偶校验等部分组成。接收部分的分频电路与发送的电路相同,信号P为奇偶校验位的选择位。信号A_IN和信号B_IN 为输入的ARINC429的TTL电平。信号在进入状态机前通过D触发器进行时钟同步。

发送状态机判断信号A_IN和信号B_IN起始位,开始启动工作,并对信号A_IN和信号B_IN进行采样,判断数据,完成后将数据存入移位寄存器最低位,同时移位寄存器往高位移1位。待Bit计数器增加后,状态机跳回到采样状态,进行下一位的数据采样。同时状态机控制奇偶校验电路工作,奇偶校验电路根据接收到的值进行“1”的个数统计。采样完第32位数据时,状态机对奇偶校验位进行判断,根据之前奇偶校验电路的统计结果和采样到的数据进行对比,判断数据是否正确。判断正确将整个数据存入数据缓冲区;不正确,则报故障。数据接收完成后,置信号Data_Ready有效。发送状态机状态转换图见图6。

电路经分频后的采样频率为ARINC429数据传输波特率的10倍。接收数据时,当两个差分输入不相同时,则认为开始接收数据。数据的每个bit进行3次采样,如图7所示。只有三次采样都符合ARINC429的TTL电平才认为数据有效,否则认为数据出错。采样 1和采样2对数据进行采样确认,只有2次采样相同,数据才会被采用,存入移位寄存器。采样3是对数据位之间的间隔进行采样,只有A_IN和B_IN全0才认为正确。以上任何一次采样出现错误,则认为数据错误。

2 设计仿真

发送部分的仿真图如图8所示(部分截图),通过编写testbench对发送数据缓冲区写入0~128,写入数据的时钟为系统时钟25 MHz,设置ARINC429总线发送波特率为100 Kb/s,奇校验,发送使能。可以看到A_OUT和B_OUT输出与预期波形一致,确认数据发送正确。

将ARINC429总线发送的串行数据引入串行数据输入端,如图9所示;读取接收缓冲RAM的数据如图10所示。输入的ARINC429总线数据波特率为100 Kb/s,输入数据为0~128。从数据缓冲区中读取数据,得到数据为0~128,与输入数据一致,数据接收正确。

3 电路验证和结论

本文ARINC429协议电路的设计基于VerilogHDL语言[4],FPGA型号使用了ACTEL的APA600[5],该电路成功地应用在多个型号产品上,并且随产品通过了严格的测试和验证。基于FPGA的ARINC429协议的设计极大地方便了PCB电路的设计,节省了板卡面积,方便通信通道的扩展。此协议还可以通过简单的设置,实现数据的交叉,LABEL的识别等功能,具有良好的实用价值。

参考文献

[1] 王春雷,罗阳,朱智强.某专用429总线接口协议的FPGA实现[J].航空兵器,2012(1):41?43.

[2] 赵显红,何谷惠.基于FPGA的ARINC429机载总线接口[J].现代电子技术,2008,31(10):93?95.

[3] ARINC公司.ARINC429传输规范[EB/OL]. [2012?02?09].http://wenku.baidu.com.

[4] 夏宇闻.Verilog数字系统设计教程[M].2版.北京:北京航空航天大学出版社,2008.

[5] Actel Corporation. ProASIC?PLUS flash family FPGAs [DB/OL]. [2003?05?30]. http://www.actel.com.

[6] 崔海青,李宏,刘博,等.一种多通道ARINC429总线收发容错方法的研究[J].现代电子技术,2013,36(6):125?128.