用于高速图像处理的DDR2SDRAM控制器

韩 刚

(西北工业大学 电子信息学院,陕西 西安 710072)

利用现场可编程门阵列(Field Programmable Gate Array,FPGA)进行高速数字图像信号处理,需解决大容量图像数据高速缓存的问题[1-3]。双倍数据率同步动态随机存取存储器(Double Data Rate 2Synchronous Dynamic Random Access Memory,DDR2SDRAM)是一种新型高速、大容量的双速率存储器,与DDR相比,DDR2的数据传输速率更高,并已成为主流。利用DDR2SDRAM可以满足高速图像处理对高速率和大容量存储的要求[4-7]。

文献[4-7]所用DDR2SDRAM 容量小,不适合于G容量超大图像处理。通过分析DDR2SDRAM的工作原理,本文拟采用硬件描述语言和模块化思想,设计一种4Gbit大容量的DDR2SDRAM控制器,并借助Xilinx公司Virtex-5系列FPGA,和MICRON公司DDR2SDRAM[8],搭建测试电路对其加以验证。

1 DDR2SDRAM控制原理

DDR2SDRAM使用差分时钟采样,数据传输在时钟的上升和下降沿交叉处进行,其片内工作频率可以降低。采用差分DQS/DQS#信号作为数据的同步信号,写入时由控制器发出,与写数据的中心对齐,读出时由DDR2产生,与读数据的边沿对齐,以此减少信号间的串扰。

对DDR2SDRAM器件的读/写访问均为突发式,以对几个地址进行连续操作来完成。控制信号有行地址选择信号、列地址选择信号和写使能信号。激活命令寄存器后开始访问,然后根据需要进行读/写命令操作。寄存地址位在激活命令时刻完成对待访问组或行的选择,在读/写命令时刻完成对突发访问选择组或起始列位置[6]的操作。

DDR2SDRAM的命令模式如表1所示。

表1 DDR2命令模式

设计不妨针对单片内存大小为2Gbit,有3个bank,14条行地址线,10条列地址线,数据位宽为16的DDR2SDRAM。设计使用2片DDR2 SDRAM按位扩展,总存储量为4Gbit,芯片接口数据位宽为32,这样对2片DDR2SDRAM的同时读写,不仅查扩展存储容量,还可加快数据读写速率。

2 DDR2SDRAM控制器设计

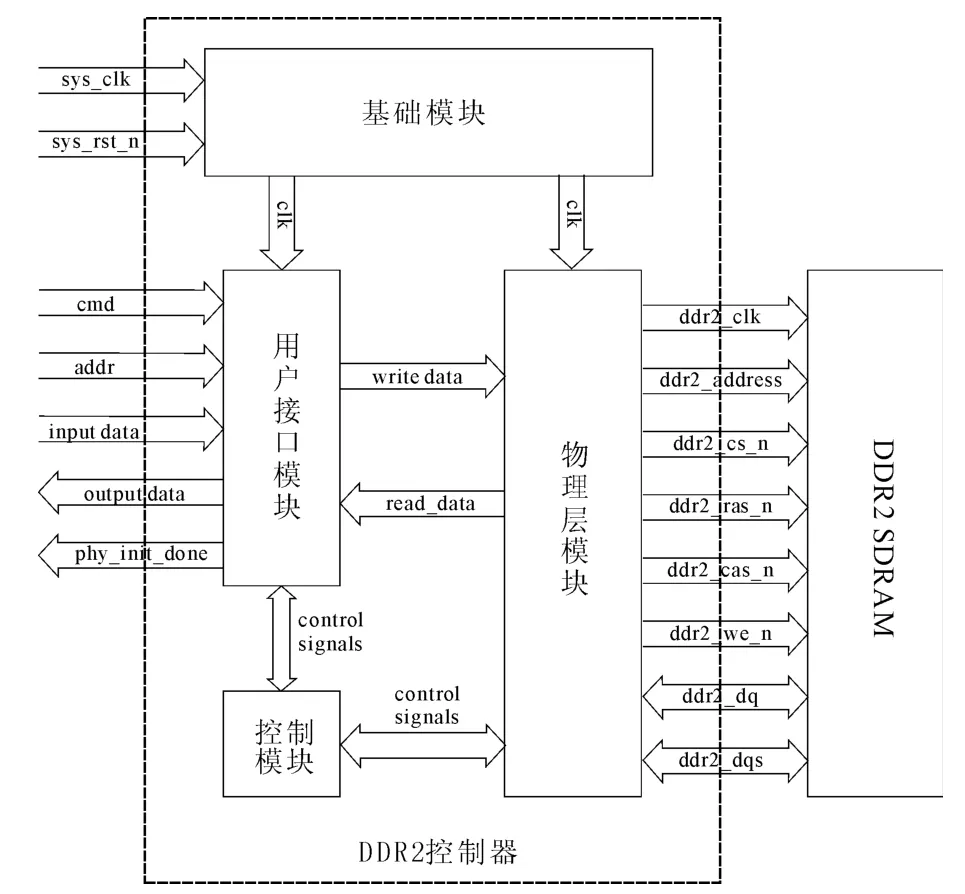

DDR2SDRAM控制器由4个模块组成,其顶层模块设计如图1所示。

图1 DDR2SDRAM控制器的顶层模块设计

(1)基础模块(Infrastructure)

基础模块用来产生控制器中所有模块的时钟信号。外部用户时钟通过锁相环(Phase Locking Loop,PLL)处理后,提供控制器所需时钟信号。该模块通过延迟校准模块,完成对读数据选通脉冲延迟的校准,以便DQS(Data Strobe)的边沿能正确对齐数据质量(data quality,DQ)信号有效电平的中间位置。

(2)物理层模块(Phy top)

物理层模块对用户的访问地址和指令进行解释和匹配,它通过DDR2SDRAM控制指令信号协调指令、地址和数据的同步,以及维持在此期间信号的有效性。

(3)用户接口模块(User Interface top)

用户接口模块在控制信号的控制下接收和存储用户的数据、命令和地址等信息。它提供读、写数据和地址三类FIFO,用户可利用该FIFO机制缓冲和同步数据。

(4)控制模块(Ctrl)

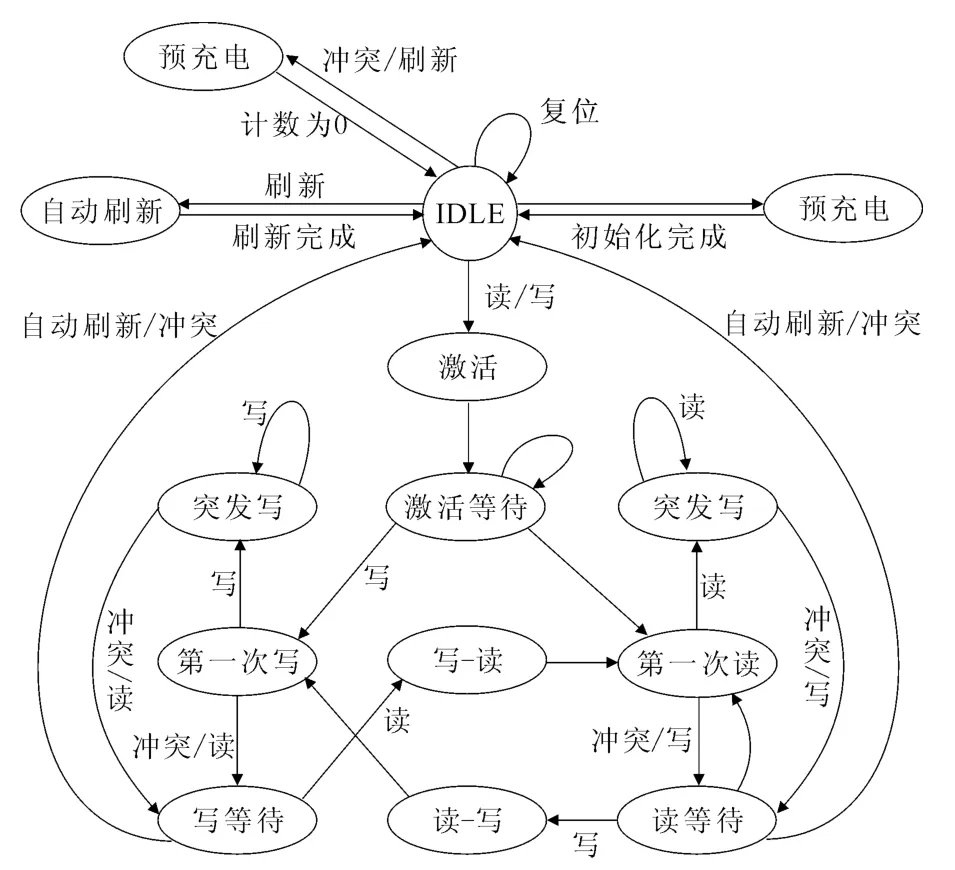

控制模块在系统加电复位时,与初始化模块一起对控制器以及DDR2SDRAM进行初始化设置和复位延时保护等操作,在系统正常工作期间,为用户接口模块、物理层模块产生相应的控制信号,为系统提供控制器状态指示信号,系统接收和应答读写请求指令,以及采样与同步访问地址,从而实现任务调度、总线仲裁、状态转换和时序同步[7]。该模块的状态机结构图如图2所示。

图2 DDR2SDRAM控制器状态机

3 DDR2SDRAM控制器功能验证

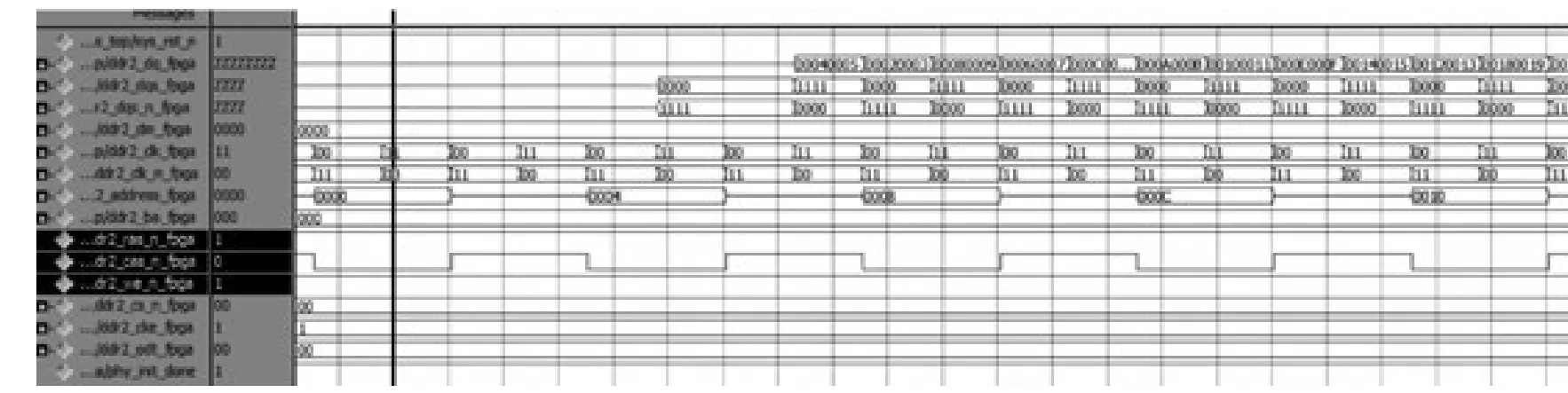

DDR2SDRAM在正常工作之前首先要进行初始化,初始化过程是设计的难点。DDR2初始化时序如图3所示。

图3 DDR2初始化时序

系统上电复位完成后,根据命令模式,控制器首先向DDR2SDRAM发送初始化指令,设置控制器的初始化参数,完成上电初始化操作,如200us上电等待后cke信号拉高、400ns所有bank预充电、OCD校准、寄存器参数装载和DLL重置等。系统初始化完成之后,DDR2SDRAM芯片的初始化完成(phy_init_done)信号由低电平变为高电平。在DDR2SDRAM初始化完成之后,系统就可以对DDR2SDRAM进行正常的读写操作。

由图3可知,系统写数据之前要先发布一个组激活命令,使行地址选择信号ddr2_ras_n为低电平,列地址选择信号ddr2_cas_n和写使能信号ddr2_we_n为高电平。

DDR2SDRAM写时序如图4所示。3个时钟周期之后发布写命令,ddr2_ras_n为高电平,ddr2_cas_n和ddr2_we_n为低电平,同时给出写地址0000,2个时钟周期之后数据总线ddr2_dq开始传输数据,差分随路时钟dd2_dqs和dd2_dqs_n边沿与数据中心对齐,以保证数据的正确采样。写完数据之后需发布一个空操作命令,ddr2_ras_n,ddr2_cas_n和ddr2_we_n均为高电平,才可以进行下一次写操作。

图4 DDR2写操作时序

DDR2SDRAM读时序如图5所示。系统读数据时需发布读命令,设置ddr2_cas_n为低电平,ddr2_ras_n和ddr2_we_n为高电平,并同时给出写地址0000,3个时钟周期之后数据总线ddr2_dq开始传输数据,差分随路时钟dd2_dqs和dd2_dqs_n边沿与数据边沿对齐,以保证读出数据与时钟的同步。读完数据之后需发布一个空操作命令,ddr2_ras_n,ddr2_cas_n和ddr2_we_n均为高电平,才可以进行下一次读操作。

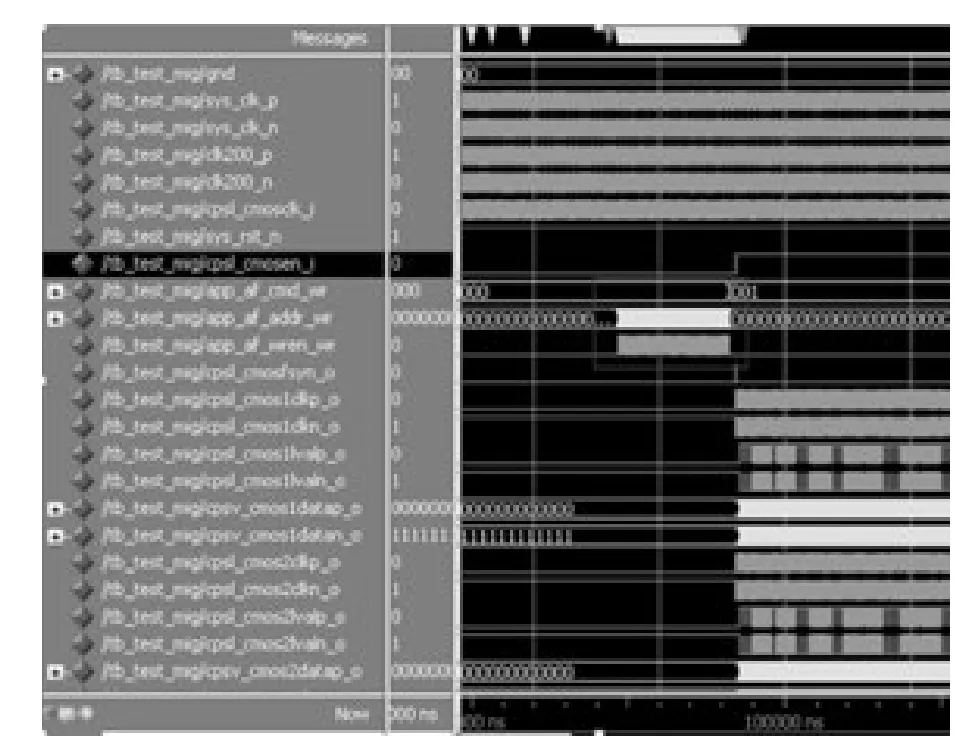

为了验证DDR2SDRAM工作的可行性,图像处理系统模拟5路CMOS图像传感器的输出,FPGA采用 Xilinx公司的 Virtex-XC5VLX130T,DDR2SDRAM选用美光的 MT47H128M16,将两片DDR2SDRAM并联,并选用ISE12.2软件进行设计。系统支持DDR2SDRAM工作频率最高为200MHz,因此最大总线传输率可达12.8Gbps。

图5 DDR2读操作时序

高速CMOS图像数据输出测试结果如图6所示。

图6 图像数据输出

给DDR2SDRAM中写入仿真图像数据。写入完毕后,将CMOS模块使能信号Cpsl_CmosEn_i置高。从图6可见,图像数据不是在Cpsl_CmosEn_i低电平使能有效时直接、不间断的写入DDR2 SDRAM,它需先往DDR2写读地址,经过一段延迟才有效,即有效数据才输出。

4 结束语

为了满足目前高速图像处理对大容量和高速缓存的设计需求,给出了一种大容量高速DDR2 SDRAM控制器的设计方法,它所支持的数据宽度为32位,最高频率为200MHz,最大总线传输率为12.8Gbit/s,可以应用于高速高性能系统。

[1]须文波,胡丹.DDR2SDRAM控制器的FPGA实现[J].江南大学学报,2006,5(2):145-148.

[2]陈雨,陈科,安涛.高速图像处理系统中 DDR2-SDRAM 接口的设计[J].现代电子技术,2011(12):104-107.

[3]莫迪涵,杜慧敏,沈绪榜.基于线性插值法图像缩放的设计与FPGA实现[J].西安邮电大学学报,2013,18(3):52-55.

[4]赵天云,王洪迅,郭雷,等.DDR2SDRAM控制器的设计与实现[J].微电子学与 计 算 机,2005,22(3):203-207.

[5]舒展.DDR2控制器IP的设计与FPGA实现[D].合肥:合肥工业大学,2009:1-33.

[6]任颖,黄建国.基于FPGA的DRR2-SDRAM控制器接口的简化设计方法及实现[J].电子质量,2008(11):31-33.

[7]黎德文,胡小文.基于FPGA的PCI总线接口设计[J].硅谷,2009(8):49-51.

[8]Xilinx.Memory interface generator(MIG)user guide[M].USA:Xilinx,2008.