全并行FIR滤波器的FPGA实现与优化

王英喆,王振宇,严伟,时广轶

(北京大学 软件与微电子学院,北京 100871)

数字信号处理及相关芯片的迅速发展与数字滤波是息息相关的,长久以来,数字滤波都是研究的热点。FIR滤波器的硬件实现方法有3种:ASIC(专用集成电路)(Application Specific Integrated Circuit)、DSP (数字信 号处理器)(digital singnal processor)以及 FPGA (现场可编程门阵列)(Field Programmable Gate Array)[1-2]。FPGA拥有全并行的处理架构,在实时信号处理、可移植的代码等方面具有优势[3]。文章在FPGA上实现高速全并行FIR (Finite Impulse Response),并针对FIR固定系数提出优化方案。

1 数学表示

FIR滤波器存在N个抽头h(n),N被称为滤波器的阶数,滤波器的输出可以通过卷积的形式表示为[4]:

通过Z变换可以将其方便地表示为:

2 全并行FIR的结构

在某些场合,需要FIR滤波器很强的实时性[5],这要求其具有高吞吐率与处理速度。全并行结构以“资源换速度”为方法,以同时运算多个乘加为方手段,使其拥有较串行高几倍的处理速度,进而获得高吞吐率。

直接型结构FIR滤波器[6]如图1所示,引入流水线技术,得到基于直接型结构的15抽头全并行FIR滤波器硬件结构。此结构同时执行所有乘法。

3 硬件实现

用Verilog HDL语言对15阶线性相位FIR进行RTL(Register TransferLeve)描述,在 Xilinx的 FPGA芯片中完成了逻辑综合、布局布线、时序分析和硬件测试。在设计和实现过程中,采用多级流水线结构,在加法器和乘法器后面都插入相应的寄存器,以FPGA设计资源换取对信号的处理速度。

3.1 逻辑设计

FIR设计的整体框图如图2所示,数据8路并行,Enable为输入有效信号、End为输出有效信号。具体可划分成三大模块,输入数据与滤波器系数点乘模块,分级寄存器数据缓存模块,并行加法模块。详细实现过程如下:

图1 全并行FIR滤波器结构Fig.1 The structure of fully parallel FIR

图2 FIR整体框架图Fig.2 The global structure of FIR

每个时钟周期进8组数据,各个数据对点乘的结果使用规律不尽相同,将输入数据与所有系数相乘得到的结果寄存,在不同周期分批使用。图3为第1、3个有效数据的分级寄存器,对于第1个数据,与H0~H7点乘的结果在本时钟周期内使用,与H8~H14点乘的结果缓存一个周期使用。第3个数据与第1个数据类似,不同的是,第3个数据与H14点乘的结果需缓冲两个周期使用,而且本周期仅用到与H0~H5的点乘结果。同理,其余6组亦如此。

图3 分级寄存器Fig.3 Hierarchical register

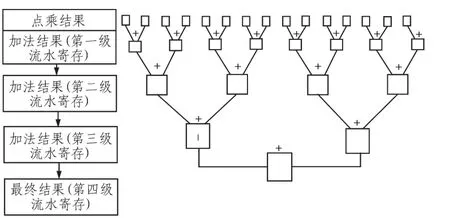

为了运行速度的最大化,加法采用全并行方式,15组数据相加,需要4个周期得到最终结果,如图4所示。

3.2 流水设计

流水线设计方法可以大幅度提高工作频率,整个数据处理是单流向的。本设计的数据流水线结构如图5,第一级将8组输入数据与所有对应系数相乘,结果进入分级寄存器中待用;第二级从分级寄存器中取数,做并行加法的第一级,第三至第五级做并行加法的第二至第四级。因此有效数据到来后第5个周期输出有效数据。

图4 并行加法模块Fig.4 Parallel adder module

3.3 验证设计

Testbench是包含3个部分,分别是FIR设计、TB生成、数据输出校验。搭建的testbench如图6所示,从文本中读取向量i_data,经过待测滤波器处理得到结果o_data,并根据end信号将向量写入相应文档中,与正确结果进行比对。

图5 FIR流水线结构Fig.5 The pipeline structure of FIR

3.4 仿真结果

如图7,在i_fir_enable信号到来后,5个周期后o_fir_enable信号拉高,之后输出一直有效,与相应matlab软件测试结果对比一致,仿真结果正确。

3.5 综合资源

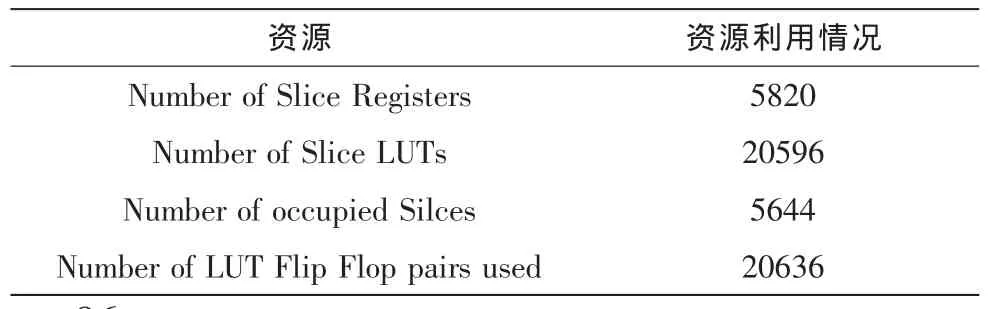

得到了正确的仿真波形后,经过综合、布局布线,能进一步得到FIR的资源利用情况,如表1。利用全并行直接乘加方法,消耗的片上资源很多,需要寻求方法来减小资源利用。

4 改进措施

设计的FIR为固定系数滤波器,针对系数固定的特点,对此提出以下两种改进措施。

图6 验证框架Fig.6 The validation diagram

图7 仿真波形Fig.7 The simulation waveform

表1 资源利用情况Tab.1 Resource utilization

4.1 措施一

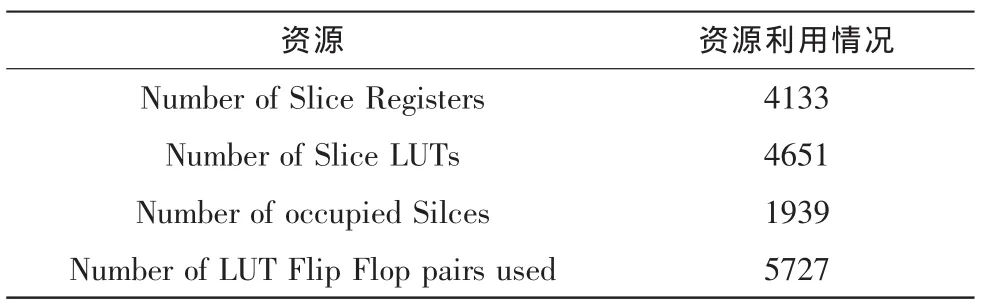

在整体结构不做调整的情况下,可以改进的地方仅有乘法器。固定系数乘法器的实现可用移位相加代替,可将资源替换成普通的LUT与FF。经改进,综合后得到的资源利用情况如表2。

4.2 措施二

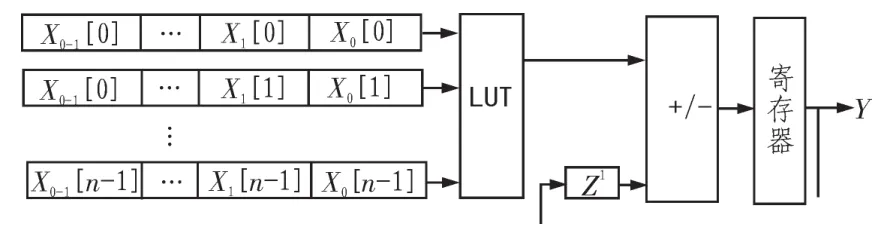

分布式算法是一种以实现乘加运算为目的的运算方法,可以用分布式算法改变FIR结构。基本FIR分布式结构如图8,而查找表构造方法如表3[6]。设计仍为15阶FIR滤波器,但将输入数据调整为8 bit,滤波器的系数h(n)以及由这些系数演算出的ROM的初始化数据文件由MATLAB产生。实现后的资源情况如表4所示。在两种优化方案中,分布式FIR占明显优势,但缺点灵活度差,如果改动数据位宽或FIR阶数,则程序需做较大改动。

表2 资源利用情况(措施一)Tab.2 Resource utilization (Measure 1)

图8 FIR分布式结构Fig.8 The distributed structure of FIR

表3 分布式结构查表方法Tab.3 The distributed structure of the look-up table method

5 结 论

文章首先介绍了FIR滤波器的数学原理与基本架构,实现了基于直接型的利用乘法器IP核的全并行FIR滤波器,并仿真验证了其正确性,同时得到所消耗资源。而后,按照两种不同的优化途径进行优化,分别针对乘法器IP核及FIR结构进行改进,得到相应资源利用情况,并进行比较。结果,对于8输入15阶FIR选择分布式结构能在达到高吞吐率高速率的情况下,节省更多逻辑资源。

表4 资源利用情况(措施二)Tab.4 Resource utilization (Measure 2)

[1]Albicocco P,Dep of Electron,Univ.of Rome Tor Vergata.Degrading precision arithmetics for low-power FIR implementation[J].Circuits and Systems (MWSCAS),2011,8(1):4.

[2]Mirzaei S,California Univ,Santa Barbara,Hosangadi A,Kastner R.FPGA implementation of high speed FIR filters using Add and shift method[J].Computer Design,2006,308:313.

[3]Chao Cheng,Parhi K K.Low-cost parallel FIR filter structures with 2-stage parallelism[J].Circuits and Systems I, 2007,280:290.

[4]高亚军.基于FPGA的数字信号处理[M].电子工业出版社,2012.

[5]徐远泽,戴立新,高晓蓉,等.FIR滤波器的FPGA实现方法[J].现代电子技术, 2010,22(2):64-70.

[6]余琳,黄光明.基于FPGA的FIR滤波器的性能的研究[J].电子设计工程,2011,19(9):125-128.