一种改进的低功耗NANDF l a s h控制器设计❋

陈小莹,于宗光,吴瑞祥,李殿英,董 杰,张梁坤

(1.江南大学物联网工程学院,无锡214122;2.中国电子科技集团第58研究所,无锡214035;3.无锡中微爱芯电子有限公司,无锡214079)

·大规模集成电路设计、制造与应用·

一种改进的低功耗NANDF l a s h控制器设计❋

陈小莹1,3,于宗光1,2,吴瑞祥3,李殿英3,董 杰3,张梁坤3

(1.江南大学物联网工程学院,无锡214122;2.中国电子科技集团第58研究所,无锡214035;3.无锡中微爱芯电子有限公司,无锡214079)

介绍了一种低功耗低成本Nand Flash控制器,控制器能够根据输入的命令码产生满足擦除、读写功能的时序完成相应操作。具有功耗低、面积小、电路实现简单的特点,采用中芯国际0.18μm工艺库进行DC综合验证,最高工作频率可达28.5MHz,面积仅需6805μm2。32位命令码仅用到低八位,能够有效实现抗干扰,在命令码判别方面,采用改进的判别电路,将命令码进行分块比较,将命令码分成高16位和低16位,然后再细分进行比较判断,减少了计数器和移位寄存器的使用,从而减小了面积。

Flash控制器;低功耗;判别电路;状态机;分块比较;低成本

1 引 言

NAND Flash存储器由于其访问时间短,功耗低,抗干扰性强等特点,广泛应用在手机设备,数码相机及固态硬盘(SSD)等媒体设备。由于集成电路的快速发展,Nand Flash存储密度呈现指数级高速增长。由于NAND Flash操作时序相对复杂,如果采用软件方式通过CPU直接控制flash的读/写操作,将会耗费CPU时间和资源,影响系统工作效率。针对flash控制器这一特点,可以采用软硬件结合方法,相对纯硬件方法,能够在牺牲一定性能的情况下降低面积[1]。

针对一款Flash存储器,设计了一种控制器,能够产生读、写、页擦除、宏擦除基本操作时序,经过仿真和综合验证,表明本设计功能的正确性,具有工程应用价值[2]。

2 总体实现方案

Flash控制器接收来自CPU的命令,然后将其转换成详细的控制信号给flash存储器,按照操作时序要求准确地控制存储器的各种操作[3],包括读/写、页擦除和宏擦除。内部存储区域又分为ROM区和Operation区,Operation区包含256个字节,ROM区容量为32Kbyte,一页大小为1024Byte,地址宽度为13位,数据宽度为16位。图1所示为flash控制器和存储器端口连接示意图,clk_low为全局时钟,clk_in为烧录时钟,data_in为串行数据输入端口,控制器根据从data_in口灌入的命令,产生相应的操作时序并输出给flash存储器,产生相应的操作。

根据烧录协议,命令码,地址及数据均从data_in口输入,因此要能够准确判断出命令码地址和数据的位置。首先控制器能够检测到从data_in输入的开始信号,即在低速时钟(clk_low)上升沿监视输入clk_in。如果检测到满足条件要求,则认为此时可以进入工作状态。

图1为所设计的flash控制器顶层端口示意图,输入包括复位时钟信号以及两个串口,分别输入时钟以及数据。输出信号data_out是一个串行输出口,输出八位命令码供检测使用,其余输出信号包括片选信号cs,地址锁存信号ae,输出使能信号oe,写编程信号prog,页擦除和宏擦除信号等。以及一些进入测试模式的控制信号。

图1 flash控制器端口示意图

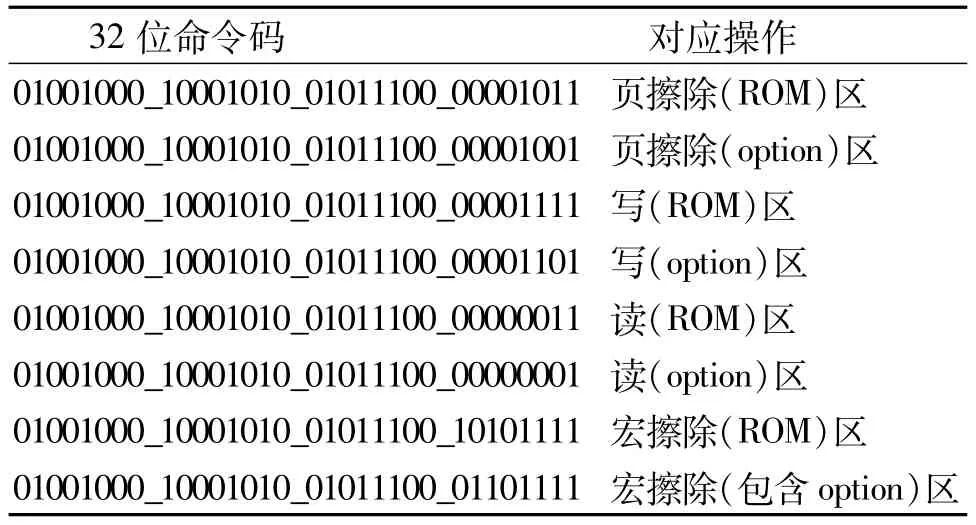

从表1中可以看出,不同操作命令码的前24位均相同,因而在判别过程可以将命令码分多次判别。以达到节省电路面积的目的。实现过程可以用图2所示。

图2 命令码判别电路

表1 命令码及对应操作

在判别过程中,没有将从串口输入的数据移位寄存到32位寄存器后再与表格中命令码比较,这样会使用较大的移位寄存器和计数器。采用将32位数据分成高16位和低16位,且判别过程仅使用一个16位寄存器,大大节省了面积。

具体地,将32位命令码分成高16位和低16位两个部分,首先将串行移入的数据用移位寄存器进行并行转换,并将移位15次后的代码存入16位cmd_code寄存器中。此时输入的是高16位命令码,将寄存器中值与表格中命令码的高16位数16’b01001000_10001010通过一个16位比较器进行比较,如果相等,则进行命令码低16位比较。此时命令寄存器中值已经更新,移位15次后,命令码低16位存入寄存器cmd_code中,低16位中的高八位与8’b01011100数进行比较,如果一致,则比较命令码的低八位,八种操作分别对应八个不同的命令码,通过选择器,如果判别结果是写命令码,则产生一个写使能控制信号。

在判别过程中,如果比较结果不一致,则不会进行后续操作,将会等待下一操作。即clk_in变为低电平且持续两个低速时钟以上,高电平持续一个时钟周期以上,重新输入命令码并进行判别。

命令码判定完成后,根据其不同,有八种操作,如表中所示。这一工作过程可用图示状态机来表示。

状态机共由九个状态组成,空闲状态、读ROM、写ROM、页擦除ROM、宏擦除ROM,及对应的Option区。当满足启动条件即clk_in持续两个低电平时间,且高电平持续时间在1~12系统时钟周期之间,则控制器从空闲状态进入工作状态。根据输入的命令码判别,分别进入不同状态,例如信号go_wr_rom有效,对ROM写入数据,按照写时序要求,控制器发送控制信号,从data_in依次输入写命令码,地址以及数据。并按照写时序产生AE、PROG、 NVSTR信号,实现将数据写入flash存储器。

图3 控制器工作状态机

3 写ROM区

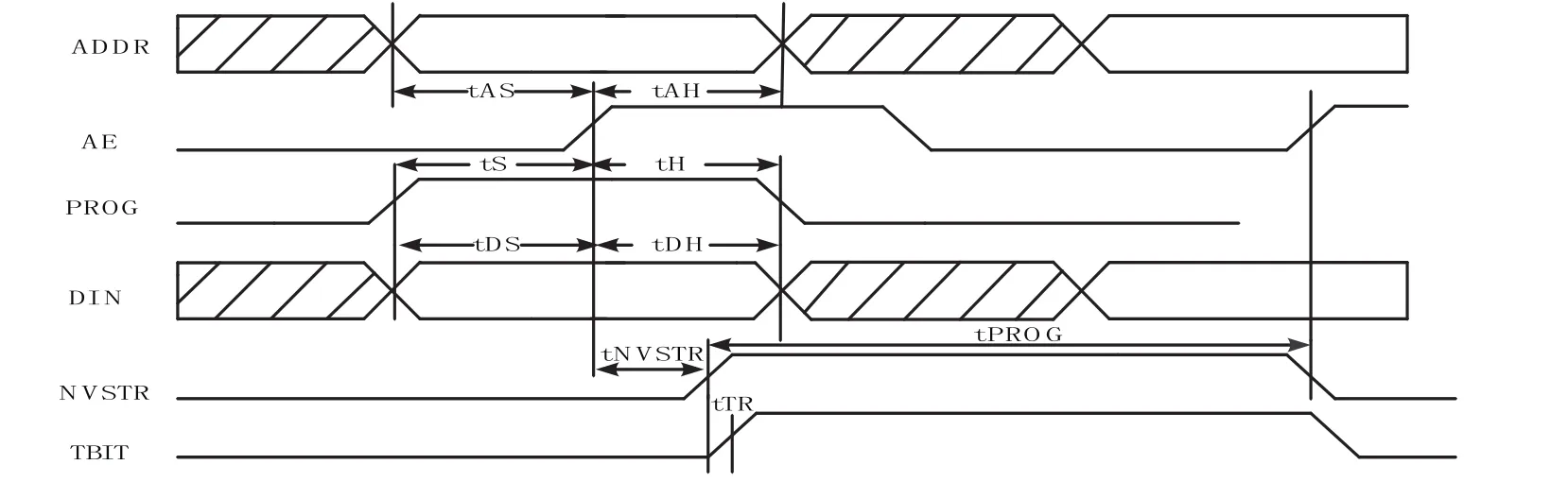

以写操作为例具体说明写时序的产生过程。图4是写操作时序,要满足规定的建立时间和保持时间以及字节编程时间要求。

图4 写操作时序

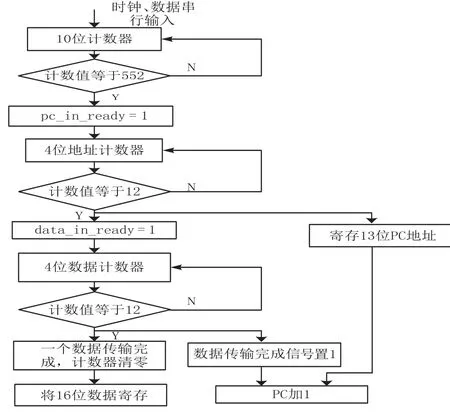

从串口输入命令码经移位比较判断后是写命令,go_wr_rom信号有效,进行写ROM区操作。32位命令码输入完成后等待8个时钟周期将命令码低八位输出,然后再等待512个时钟周期,开始输入地址初值和数据。到数据输入结束这一过程共使用三个计数器,分别从开始输入命令码到输入地址时用一个10位计数器进行计数;当计数到552时,开始进行地址输入,此时用一个4位计数器对13位地址进行计数;首地址输入完成后开始输入待写入存储器的数据,用一个4位计数器计数,每个数据传输完成后产生一个完成信号da_completed,然后计数器清零,重新开始计数。这一过程可用如图5所示。

使写入的地址和数据一一对应,并产生写操作下的地址使能信号AE、编程信号PROG以及NVSTR信号。具体地,一个数据最终移位完成需要15个clk_in时钟周期将最终移位结果寄存起来,因而数据稳定时间为16个Tc(PA2口输入的时钟周期),只输入首地址PC,控制每个数据传输完成后地址自动加1,因而地址和数据均持续16个时钟周期。

图5 写操作执行过程流程框图

使写入的地址和数据一一对应,并产生写操作下的地址使能信号AE、编程信号PROG以及NVSTR信号。具体地,一个数据最终移位完成需要15个clk_in时钟周期将最终移位结果寄存起来,因而数据稳定时间为16个Tc(PA2口输入的时钟周期),只输入首地址PC,控制每个数据传输完成后地址自动加1,因而地址和数据均持续16个时钟周期。

地址和IFREN信号至少稳定2ns后,控制AE上升沿到来,而编程信号PROG需要在AE上升沿到来5ns之前有效,保证写编程时间保持20μs以上,利用地址/数据持续时间产生这些控制信号,其他信号在写操作时拉低。

4 仿真与综合验证

4.1 仿真验证

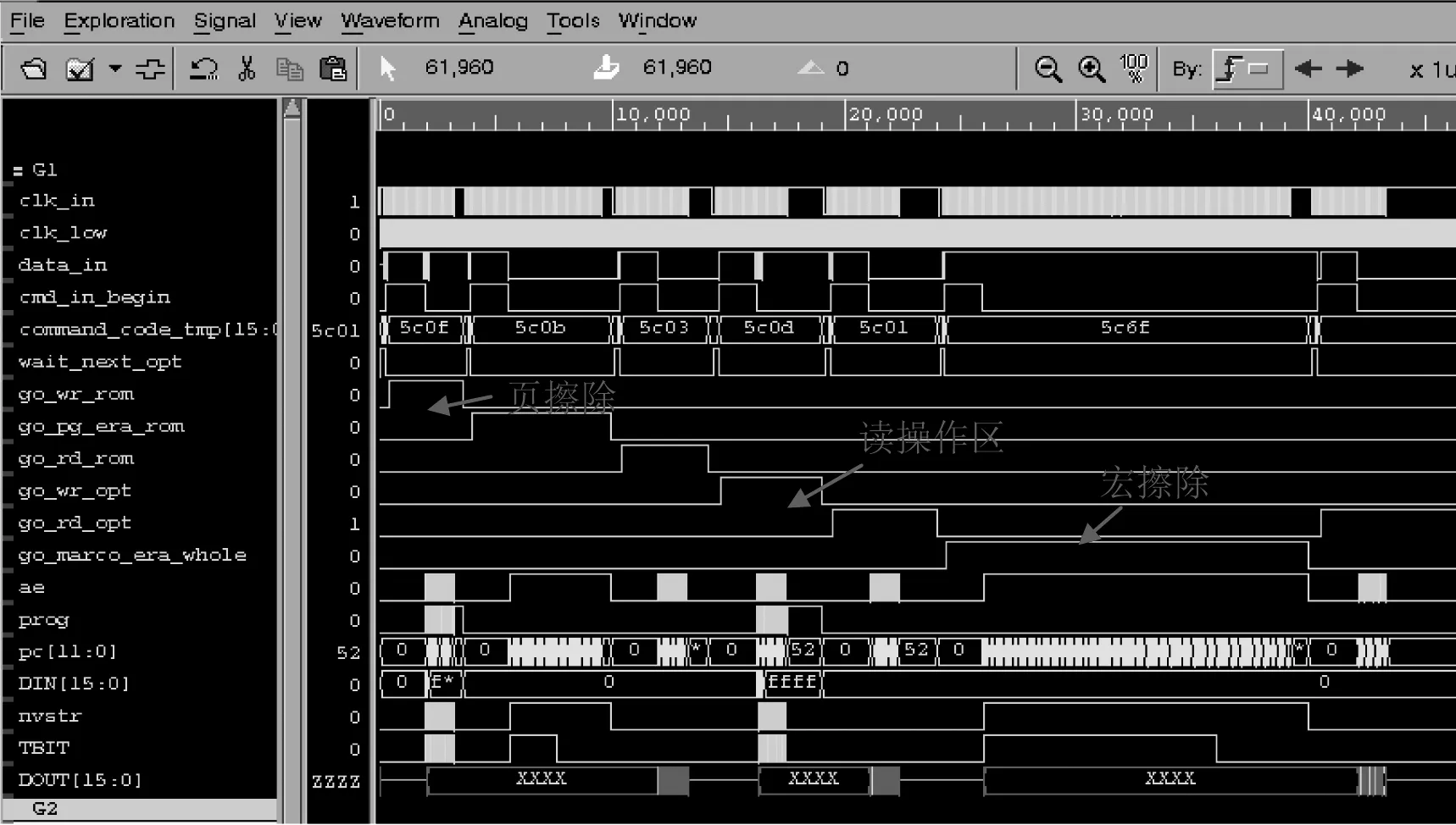

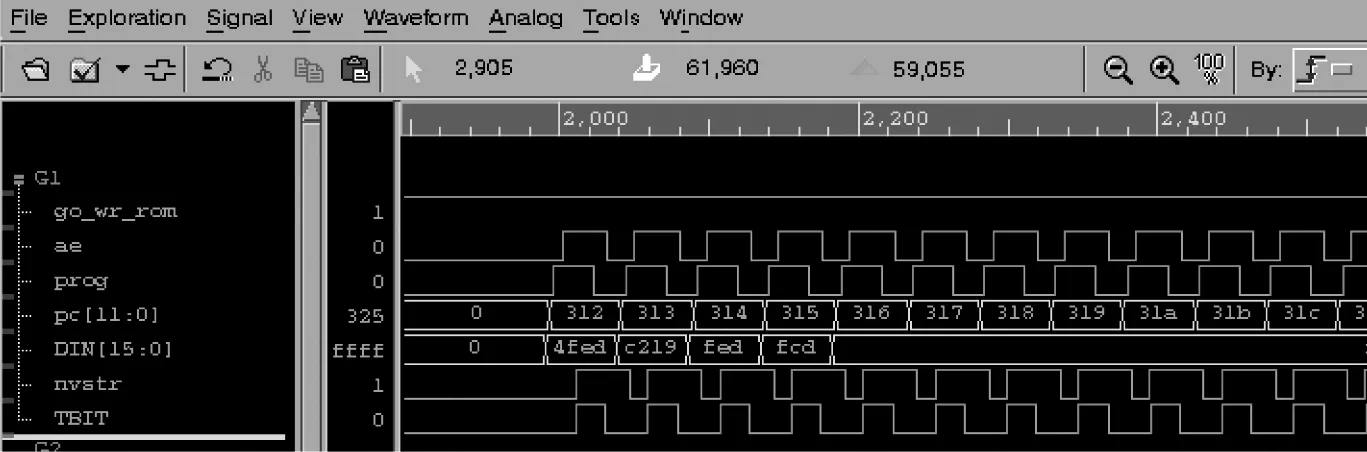

RTL代码完成后搭建仿真平台添加相应激励用ncverilog进行验证,并用Springsoft软件分析波形。在测试平台中进行了读、写,页擦除,宏擦除操作验证,从串口data_in输入对应的命令码,验证是否能够完成相应操作,仿真结果如图6所示。

图6 各种操作仿真波形

clk_low是系统时钟,clk_in为从串口输入的时钟,从data_in口输入命令码,pc地址,以及数据。首先进行写ROM区操作,从data_in输入写操作对应的命令码,经过图2所示判别电路后,产生go_wr_rom信号,写ROM区信号有效,等待一定的时钟周期后,data_in口输入要写入数据的首地址PC,然后地址自动加1。地址输入完成后输入对应地址要写入的数据,操作完成后,等待下一操作wait_next_opt信号有效,控制器进入空闲状态。直到满足开始条件,控制器开始进入工作状态。写操作完成后,flash存储器的数据输入口DIN此时已经写入数据。如图7所示,首地址312及地址自加依次写入数据4fed,c219,0fed,0fcd四个数据,每个数据写入成功后,在nvstr信号上升沿到来100ns后,产生TBIT信号。

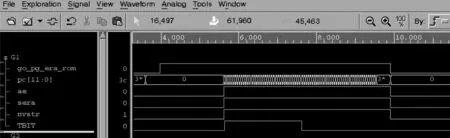

写操作完成后,进行页擦除,go_pg_era_rom信号有效,进行页擦除时,只需要给定要擦除页的首地址,然后擦除1024Byte字节。如果擦除的是Option区(IFREN=1),则只需将首地址之后所有Option区内容全部擦除。页擦除时间至少持续2ms,擦除一页成功会产生TBIT变为高电平。页擦除波形放大后如图7所示。

图7 写操作对应时序波形

为了验证页擦除是否成功,在擦除操作后对之前写入数据的地址内容进行读操作,输入读操作对应的命令码,经判别电路判别后产生go_rd_rom信号,并给出要读的首地址,控制器产生读操作对应的时序给flash存储器,读出的信号经DOUT端口输出,经验证页擦除完成后,之前写入数据的地址读出的数据为16’hFFFF,表明擦除成功。

页擦除操作后又连续进行了写操作区,读操作区,宏擦除,读操作区四个操作,如图6所示,均通过验证。表明所设计的flash控制器能够根据输入的指令码产生相应的操作时序完成对应操作。根据给定的Flash存储器时序,页擦除最少时间为2ms,宏擦除最短时间为10ms,表2列出了仿真时各操作对应的操作时间。

图8 页擦除对应时序波形

表2 完成各操作对应时间

4.2 DC综合

仿真验证通过后,对所设计的flash控制器进行综合验证。选用SMIC0.18μm工艺库进行DC综合。系统时钟clk_low设置为频率28.5M,从串口输入的时钟clk_in为100M,工艺库规定的setup时间0.18ns。仿真报告如表3所示。

表3 综合报告汇总

综合结果表明,所设计的flash控制器能够达到28.5MHz工作频率,且在SMIC 0.18μm工艺库下能够实现时序收敛。本设计与检验模块等功能[4-6]的设计相比,最大的优点就是功耗低,占用面积很小,能够满足一般应用场合[7]。

5 结束语

设计了一款flash控制器[8],能够跟已有flash存储器连接产生相应的操作时序,仿真和综合验证表明满足功能要求。在命令码判别电路实现方面,采用改进的判别电路,比直接判别32位命令码减少了计数器和移位寄存器的使用,节省了面积,能够适应干扰较小,工作频率要求不太高的场合,电路简单容易实现,很大程度上节约了设计成本。

[1] 韩睦华,支军,刘雷波,等.新型智能存储SoC中NAND Flash控制器的软/硬件设计[J].微电子学,2009,39(2):185-189.

Han Mu-hua,Zhi Jun,Liu Lei-bo,et al.The software and hardware design of NAND Flash controller in new smart storage system[J].Microelectronics,2009,39(2):185-189.

[2] Wei Lin,Shao-Wei Yen,Yu-Cheng Hsu,et al.A low power and ultra high reliability LDPC error correction engine with Digital Signal Processing for embedded NAND Flash Controller in 40nm CMOS[C].VLSICircuits Digest of Technical Papers,2014:1-2.

[3] 陈超文,彭国杰,王忆文,等.基于PLB总线的NOR FLASH控制器设计[J].微电子学与计算机,2014,31(5):83-86.

Chen Chao-wen,Peng Guo-jie,Wang Yi-wen,et al.Design of NOR Flash controller based on PLB bus[J].Microelectronics&Computer,2014,31(5):83-86.

[4] 刘宁宁,田泽,裴希杰.基于Core Connect总线的NAND Flash控制器设计[J].计算机应用,2014,34(S1):327-329,344.

Liu Ning-ning,Tian Ze,Pei Xi-jie.Design of NAND Flash controller based on Core Connectbus[J].Journalof computer applications,2014,34(S1):327-329,344.

[5] LEE C,BAEK SH,PARK K H.A hybrid flash file system based on NOR and NAND Flash Memories for embedded devices[J].IEEE Transactions on Computeers,2008,57(7):1002-1008.

[6] Eyec Hyun Nam,Kim,B.S.J.,Hyeonsand Eom,et al.An Out-of-Order Flash Memory Controller Architecture[J].IEEE Transactions on Computers,2011,60(5):653-666.

[7] 郭瑞,赵新辉,高性能NAND Flash控制器在SoC平台中的设计与应用[J].计算机应用与软件,2012,29(12):116-119.

Guo Rui,Zhao Xin-hui.Design and application of high performance NAND Flash controller in SoC system[J].Computer applications and software,2012,29(12):116-119.

[8] Yu-Hsiang Kao,Juinn-Dar Huang.High-Peformance NAND Flash Controller Exploiting Parallel Out-of-Order Command Execution[C].//VLSI Design Automationand Test(VLSI-DAT),2010 International Symposium on.IEEE,2010:160-163.

Design on An Im proved Low Power Consum ption NAND Flash Controller

Chen Xiaoying1,3,Yu Zongguang1,2,Wu Ruixiang3,Li Dianying3,Dong Jie3,Zhang Liangkun3

(1.College of Internet of Things,Jiangnan University,Wuxi214122,China;2.No.58 Research Institute of China Electronics Technology Group Corporation,Wuxi214035,China;3.Wuxi I-Core Electronics Co.,Ltd.,Wuxi214079,China)

This paper introduces an improved NAND Flash controller which can easily realize some basic operations by generating the corresponding timing.The circuit has advantage of low power consumption,simple structure and small area size,based on SMIC 0.18μm standard CMOS process library,and works at28.5MHzwith the area of6805μm2.The lower-eight bits of total32bits command code are used for increasing stability and reliability.The improved command judging circuit needs less area resource through reducing the use of counters and shift registers.

Flash Controller;Low power consumption;Judging-circuit;State machine;Block comparison;Low cost

10.3969/j.issn.1002-2279.2015.06.001

TP333.7

A

1002-2279(2015)06-0001-05

陈小莹(1990-),女,江苏省宿迁市泗阳县人,硕士研究生,主研方向:数字集成电路设计。

于宗光(1964-),男,山东省潍坊市人,博士,教授/博导,中国电科集团首席专家,主研方向:集成电路设计与可靠性。

2015-08-26