基于?C/OS—II硬件加速模块的研究与实现

隋宇晖++范延滨++杨厚俊

摘 要:为了满足嵌入式操作系统对实时性的要求,提出了基于FPGA的硬件加速模块的实现,将?C/OS-II操作系统中原有的调度器与定时器部分进行合理的硬件化实现。整个设计采用Verilog硬件描述语言,通过Quartus II 13.1软件进行时序仿真验证,通过仿真,得出此方法可以提高系统的实时性,降低系统的额外开销。

关键词:实时性;FPGA;调度器;定时器

中图分类号:TP393 文献标识码:A 文章编号:2095-1302(2015)05-00-02

0 引 言

嵌入式实时操作系统[1]是一种实时的、支持嵌入式系统应用的操作系统软件,它是嵌入式系统的重要组成部分。与通用操作系统相比,嵌入式操作系统在系统实时高效性、硬件的相关依赖性、软件固态化以及应用的专用性等方面有较为突出的特点。嵌入式实时操作系统?C/OS-II[2]是一种基于优先级的抢占式操作系统,具有很强的实时性。但是,航空航天、工业控制和核电站建设等领域的发展,对嵌入式操作系统的实时性提出了越来越高的要求。随着FPGA[3]的集成度和速度的不断提高,使嵌入式操作系统的硬件化实现成为可能[4]。我们提出将?C/OS-II的调度器[5]与定时器[6]进行硬件化实现,来提高嵌入式系统的实时性。

1 ?C/OS-II的任务调度器和时钟

1.1 ?C/OS-II中的调度器

在?C/OS-II中,任务调度由任务调度器来完成。任务调度器的主要工作有两项:一是在任务就绪表中查找具有最高优先级别的就绪任务;二是实现任务的切换。

?C/OS-II调度器用于获取优先级别最高的就绪任务的代码,如下[7]所示:

y = OSUnMapTbl[OSRdyGrp];

x = OSUnMapTbl[OSRdyTbl[y]];

prio = ( y << 3 ) + x;

其中,OSRdyTbl[]是就绪任务登记表,登记了系统中所有处于就绪状态的任务。它本质上是一个类型为INT8U的数组,它的每一个二进制位对应一个任务,每一位的1/0表示对应的任务处于就绪/非就绪状态。OSRdyGrp是一个数据类型为INT8U的变量,每一位都对应OSRdyTbl[]的一个任务组。OSUnMapTbl[]是?C/OS-II为提高查找速度定义的一个数组,共有256个元素。

任务切换的工作是靠OSCtxSW()来完成,中止正在运行的任务,转而去运行就绪任务中优先级别最高的任务。

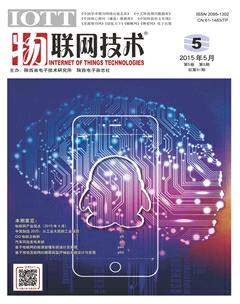

由于任务切换时需要对CPU的寄存器进行操作,所以我们只是对查找最高优先级任务这一部分进行硬件化实现。如图1所示。

1.2 ?C/OS-II中的时钟

?C/OS-II与大多数计算机系统一样,用定时器产生一个周期为毫秒(ms)级的周期性中断来实现系统时钟。定时器以时钟节拍为周期定时的产生中断,该中断的中断服务程序叫做OSTickISR()。中断服务程序通过调用时钟节拍服务函数OSTimeTick()来完成系统在每个时钟节拍时需要做的工作。

每次响应定时中断时,?C/OS-II调用OSTimeTick()进行如下操作:一是给计数器OSTime加1;二是遍历任务控制块链表中的所有任务控制块,把各个任务控制块中用来存放任务延时时限的OSTCBDly变量减1,并使该项为0,同时又不使被挂起的任务进入就绪状态。简单的说,函数OSTimeTick()的任务就是在每个时钟节拍了解每个任务的延时状态,使其中已经到了延时时限的非挂起任务进入就绪状态。

定时器相关函数的顺序执行使实时操作系统的实时性受到影响。因此,我们提出将定时器硬件化,以改善操作系统的实时性。

2 调度器的硬件化设计与实现

任务调度器实现任务控制块TCB(Task Control Block)队列(简称任务队列)的操作与管理。所有未执行任务放在等待队列和就绪队列中,等待队列中的任务在条件(如定时到、事件到达、中断到达等)满足时将变为就绪任务,等待任务调度。任务调度器在每个调度时钟内计算出优先级最高的就绪任务,调度器采用抢占式调度机制,每个调度时钟输出优先级最高的就绪任务,通过中断方式向处理器提出任务服务,转向执行任务代码。

图1 任务调度器结构

在?C/OS-II中,系统内核基本工作是任务调度,系统运行中,将会有一定的资源消耗在调度上,大约占用CPU资源的2%~5%[8]。在硬件完成系统调度器中查找最高优先级任务这一部分,释放调度占用的CPU资源,将就绪表硬件化。在任务就绪表中,每一位与一个任务相对应,每一位的地址与任务优先级相同,第n位为1表示任务n处于就绪状态,第n位为0表示任务n处于非就绪状态。这样,从处于就绪态状态的任务中找到优先级最高的任务只需要一个时钟节拍。如图2所示。

图2 任务调度器仿真

以8个任务为例,tbl_in是当前就绪表的状态,prio_o是当前就绪任务中的最高优先级,flag作为中断请求标志位,每个调度时钟输出优先级最高的就绪任务,通过该中断请求信号向处理器提出中断请求。

3 可编程硬件定时器的设计与实现

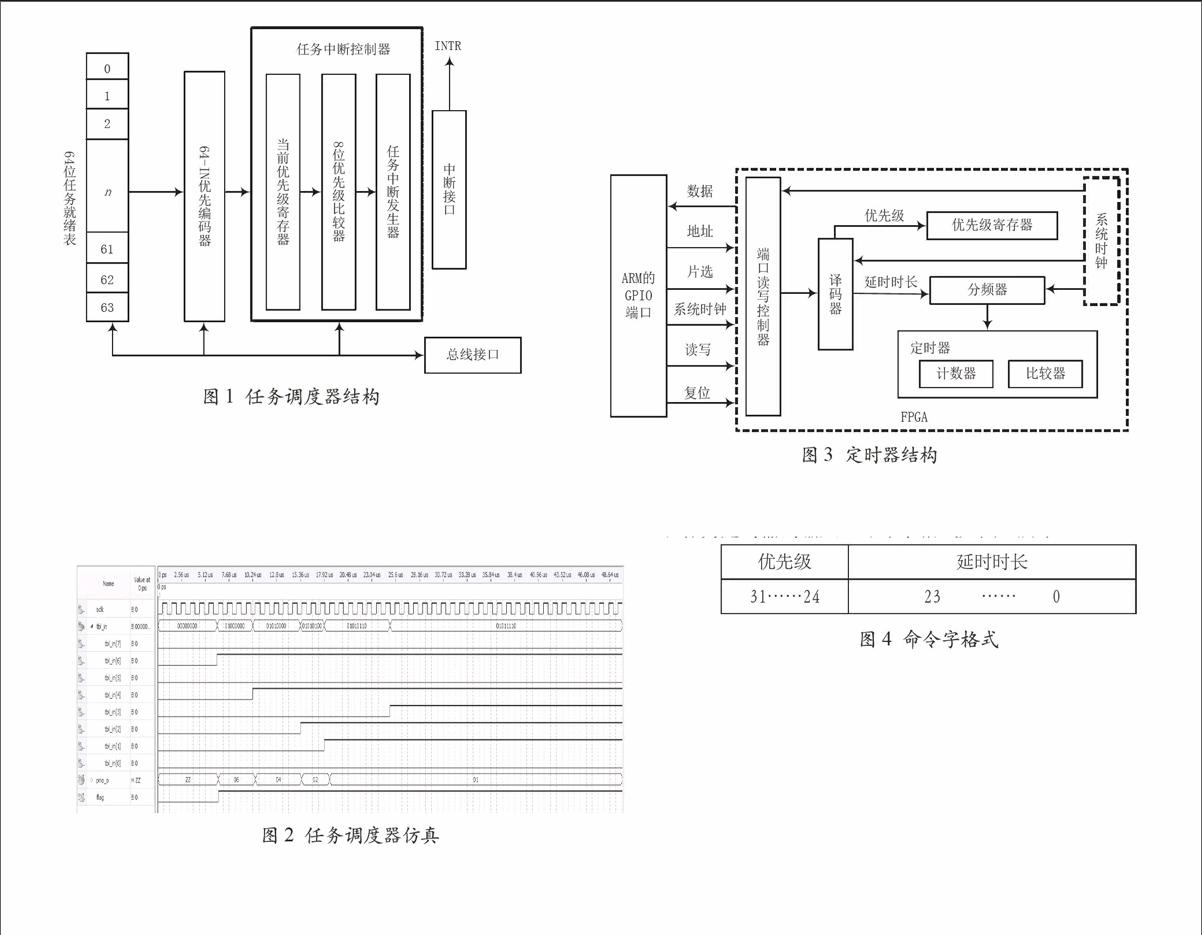

系统中软件定时器实现函数是顺序执行的[9],降低了系统的实时性。要实现定时或延时控制,主要有三种方法:软件定时、不可编程的硬件定时器、可编程的硬件定时器。其中,可编程定时器电路的定时值及范围可很容易的由软件来确定和改变,功能较强,使用灵活。因此,本文将?C/OS-II的软件定时器用可编程的硬件定时器替换,从而提高系统的实时性。如图3所示。

我们为每一个任务设计一个定时器,用于管理任务的延时和运行周期。软件通过向硬件模块传送定时命令字来指定延时任务以及延时时长。硬件模块接收该定时命令字后,对该命令字进行译码,获得延时任务的优先级以及延时时长,进行定时操作。当设定的定时时间到,进行一次任务调度,让出CPU的使用权。

图3 定时器结构

可编程硬件定时器由定时命令字、分频器、定时器(计数器以及比较器)三部分组成,三个部分的实现分别如下:

(1)定时命令字

从软件传送来的32位定时命令字,高8位为优先级,用来指定延时任务;低24位为延时时长,用来指定定时时间。经过译码器解析之后,优先级置于优先级寄存器中,延时时长作为定时器的输入。命令字格式如图4所示。

优先级 延时时长

31……24 23 …… 0

图4 命令字格式

(2)分频器

通过分频器来控制定时器精度。如果系统时钟是50MHz,将50 MHz的系统时钟转换为1 MHz,时钟周期为1 ?s,定时器精度为1 ?s,则我们可以将延时范围控制在0~16777 216 ?s(224 ?s)之间。

(3)定时器

调用LPM(Library of Parameterized Modules 参数可设置模块库)的计数器和比较器来综合实现定时器功能。

计数器:24位加1普通二进制计数器,Clock Enable作为使能信号。输入为时钟和时钟使能,输出为计数值。

比较器:输入为两个24位的二进制数dataa、datab,输出为aeb(a equal b),若两数相等,输出为1,否则为0。

定时器:对计数器和比较器分别例化,计数器的输出作为比较器的一个输入dataa,比较器的另一个输入是通过解析命令字得到的延时时长。定时器的输入为时钟及定时命令字,高8位作为优先级,低24位作为比较器的输入datab;输出为优先级及比较器的输出结果。比较器的输出可作为定时已到的标志位。如图5所示。

图5 定时器RTL图

4 结 语

采用硬件逻辑实现实时操作系统中的任务调度和定时器管理功能,可使其实时性和确定性显著提高。因为硬件逻辑独立于处理器运行,不占用处理器的处理时间,所节省的时间用于执行任务程序,从而提高了任务集合的可调度性和实时性。实时操作系统的硬化随着EDA(Electronic Design Automation)设计技术的发展、可编程逻辑器件及相关技术的提高,它在很多处理系统尤其是嵌入式系统与单片机系统中,将会有广泛的应用前景。

参考文献

[1]林建民.嵌入式操作系统技术发展趋势[J].计算机工程,2001,27(10):1-4.

[2]任哲.嵌入式实时操作系统mC/OS-II原理及应用[M].第2版,北京:北京航空航天大学出版社,2009.

[3]潘松,黄继业,潘明.EDA技术实用教程-Verilog HDL版[M].第4版,北京:科学出版社,2010.

[4]尹震宇,赵海,王金英,等.一种嵌入式处理器上的HOS设计[J].计算机工程,2008,34(5):268-270.

[5]李岩,崔晓英,李贤尧,等.基于FPGA的mC/OS-II任务管理硬件设计[J].电子技术应用,2010,36(2):25-29.

[6]张炜,李克俭,蔡启仲,等.基于FPGA的PLC并行定时器的设计[J].计算机工程与设计,2013,34(4):1244-1249.

[7] Jean J.Labrosse,邵贝贝译.嵌入式实时操作系统mC/OS-II [M].第2版,北京:北京航空航天大学出版社,2007.

[8]张涛,廖力清,王颂.mC/OS-II内核在FPGA上的硬件化设计与实现[J].电子技术应用,2009,35(4):41-44.

[9]沈国新,张德学,王贵海,等. 一种实时操作系统硬件加速设计[J]. 微型机与应用,2010,29(6):17-19.