铁路轨边数据采集系统的设计与实现

陈天柱,李旭伟,李甫永,秦 菊

(中国铁道科学研究院 铁道建筑研究所,北京 100081)

铁路轨边数据采集系统的设计与实现

陈天柱,李旭伟,李甫永,秦 菊

(中国铁道科学研究院 铁道建筑研究所,北京 100081)

针对铁路线路复杂和恶劣的测试环境,设计了轨边数据采集系统,本系统利用无线传输模块进行传输,使远程数据采集、分析和处理成为现实,更少地受到自然条件的制约。本设计采用一种以Altera FPGA为核心控制器,通过对模拟开关ADG408、模数转换器AD976控制,实现了8路模拟信号的采集;同时利用单片机C8051F020对GPRS网络模块MC37I控制,实现无线数据控制和传输。

数据采集;无线传输;Altera FPGA;单片机

在铁路线测试中,经常需要对钢轨受力等进行监测,对数据采集设备有灵活性和机动性的要求,轨边数据采集系统很好地满足这一需求。该数据采集系统实现了对铁路铁轨以及限界测试中的各种传感器产生的电压信号进行采集,有效克服恶劣自然条件对数据采集的影响。

1 系统框架

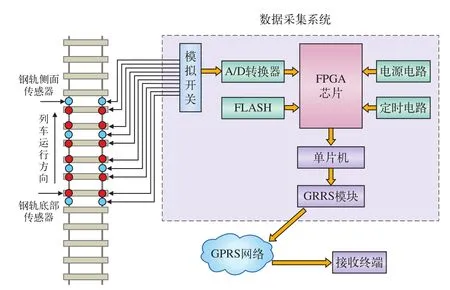

轨边数据采集系统由数据采集、存储处理、接口控制、无线控制和传输等部分组成,如图1中虚线框中所示。

该系统主要是将传感器输出的模拟电压信号,通过模拟开关由选择的输入给A/D转换电路,经过处理后,通过通用无线分组业务(GPRS)网络传输到接收终端,可以实现8路模拟信号输入,通过控制A/D转换器实现对采样速率的控制。

图1 轨边数据采集系统框图

2 系统硬件设计

2.1 FPGA硬件设计

在整个轨边数据采集系统中,既要对数据采集模块进行控制,又要对采集到的数据进行存储并发送给微控器,实现数据的无线传输。本系统选用Cyclone系列EP1C12的现场可编程门阵列(FPGA)。它具有12 060个逻辑单元(LE),一个LE由4输入查找表和一个可编程触发器以及辅助电路组成,支持双数据速率同步动态存储器(SDRAM)快速可靠的数据交换,支持联合测试协议(JTAG)配置方式。

2.1.1 EP1C12配置电路

电源电路:根据EP1C12芯片对电源的要求,在本系统中需要的电源如下:1.5V/3A、2.5V/6A、3.3V/3A,选用的电压转换芯片分别为AS2830AT-1.5、AS2830AT-2.5、AS2830AT-3.3,采用50 MHz的4脚晶振。

FPGA是使用静态存储器(SRAM)工艺生产的,掉电后SRAM的数据丢失,因而FPGA每次启动都需要重新加载数据。主动配置方式(AS),将配置数据从配置芯片EPCS4中读到SRAM里,不需要外部下载设备进行配置,可实现断电后的自动加载。

2.1.2 数据采集模块

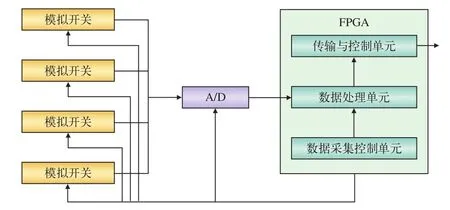

数据采集模块主要有模拟开关、A/D转换器、FPGA控制器组成,结构如图2所示。

图2 数据采集结构框图

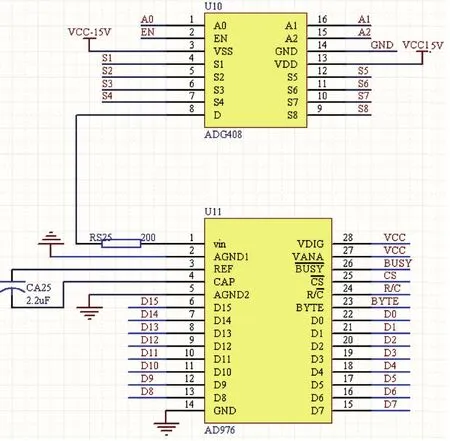

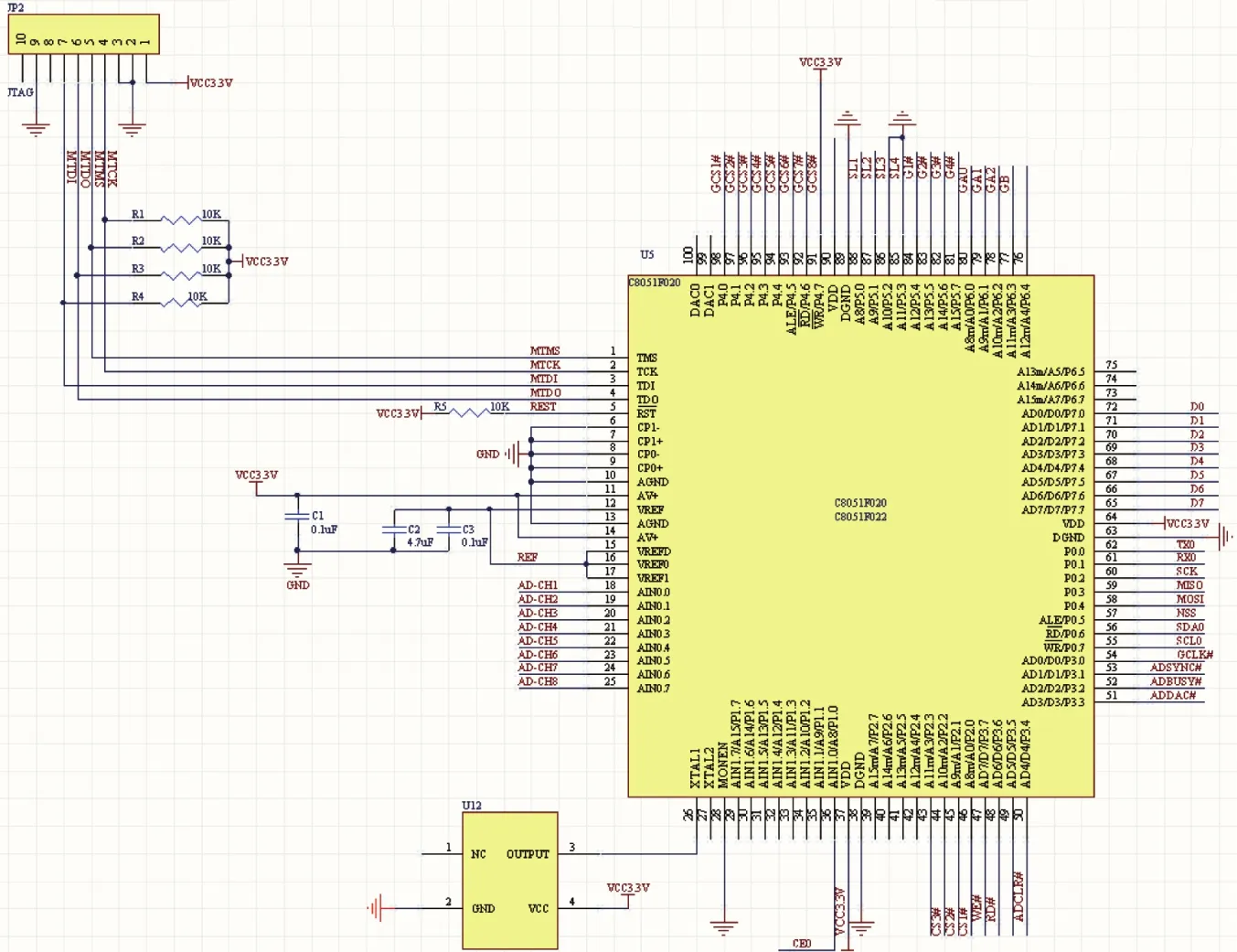

图3 ADG408与AD976的电路原理图

由模拟开关ADG408,A/D转换芯片AD976组成的电路原理图,如图3所示。

2.2 单片机硬件设计部分

在整个轨边数据采集系统中,单片机部分主要负责从FPGA中读取数据,然后通过GPRS芯片实现无线传输。无线传输部分主要是有单片机和GPRS芯片以及一些辅助电路组成。

单片机C8051F020是Silicon Labs推出的高度集成混合信号单片机,具有25 MIPS 8 051 CPU内核、64 KB Flash存储器和4 352 BRAM,两个独立的ADC转换器。可以通过片上4脚JTAG调试电路允许使用安装在最终产品上的单片机进行非侵入、全速度、在系统调试。基于以上特点,采用C8051F020作为整个系统的单片机处理芯片。

2.3 无线传输模块

无线传输模块主要是由CF8051F020的UART与GPRS通信模块MC37I的全双工通信串口相连接,实现CF8051F020对MC37I的控制和通信。原理如图4所示。

图4 无线传输模块电路原理图

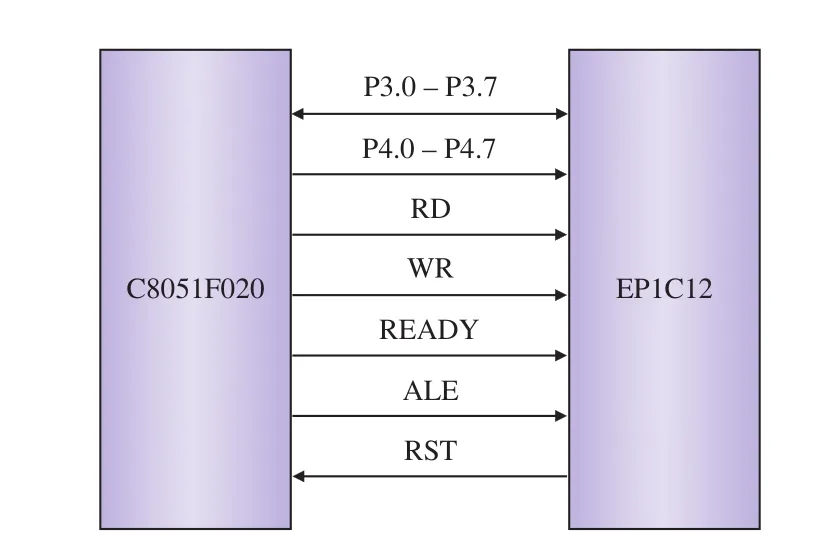

2.4 FPGA与单片机的接口

目前,单片机或微控器与各种可编制逻辑门阵列芯片相级联,实现多机通信。C8051F020与FPGA EP1C12之间通信的方式也有两种方式,分别是串口通信和并口通信,两种方式各有优缺点。本系统采用C8051F020与FPGA EP1C12之间通过并口连接来通信,如图5所示。

图5 单片机与FPGA并口通信框图

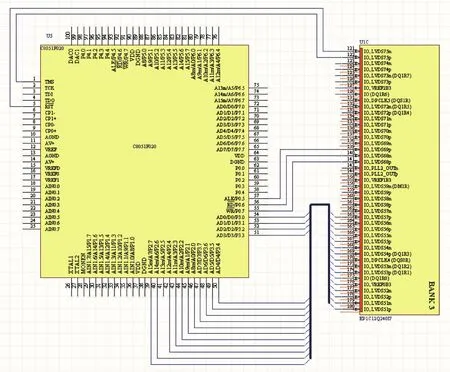

C8051F020的端口P2、P3的16个数据位端口与EP1C12的16个数据端口相连接,可以通过系统总线从EP1C12中读取采集到的数据; EP1C12可以对单片机C8051F020发送复位信号RST;ALE为地址锁存信号,低电平有效;RD为读出使能信号,当RD被置高电平时有效。WR为写出使能信号,当被置高电平时有效;READY为系统准备好信号,高电平有效,C8051F020可以从系统总线上读取数据。C8051F020与EP1C12采用总线方式连接的原理图如图6所示。

3 系统软件设计

系统的软件设计分为数据采集模块、FPGA与单片机通信模块和无线传输模块的软件设计。

3.1 数据采集模块的软件设计

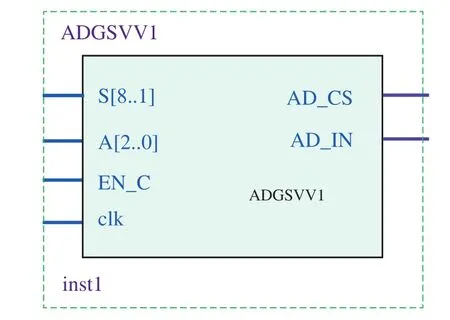

模拟开关控制电路的主要功能是负责对不同地址的输入信号进行控制,确定哪个通道的信号被允许输入到模数转换器中,从而保证各通道信号依次输入到AD976中,不断循环。ADG408的3个地址选通端A0、A1、A2以及使能控制端共同决定相应地址的信号输入,使得从ADG408的S1,S2,…,S8这8个输入端的输入信号,依次被AD976进行采样,依次循环,完成对输入信号的周期性数据采集。ADG408工作时,每次使能信号(EN)被置位时,稍后向系统发送转换脉冲,模拟开关控制电路在FPGA上的设计模块如图7所示。

图6 C8051F020与EP1C12采用总线方式连接的原理图

图7 模拟开关控制模块框图

本模块共有15个信号端。S1、S2、…、S8是外部信号输入端;A0、A1、A2是地址信号端;clk是系统时钟输入端;EN_C是芯片选通使能信号端;AD_CS是片选信号输出端;AD_IN是信号输出端。

A/D转换电路主要是把从ADG408输出过来的模拟信号转换成数字信号,在输送到EP1C12中完成数据处理,实现AD转换工作。D15、D14、…、D8是输出数据的高8位;D7、D6、…、D0是输出数据的低8位;BYTE是输出高低字节的选择端;clk是时钟输入端;CS_N是芯片选通端,低电平有效;R_ C是转换控制端;BUSY_N是转换完成标志位,低电平有效。

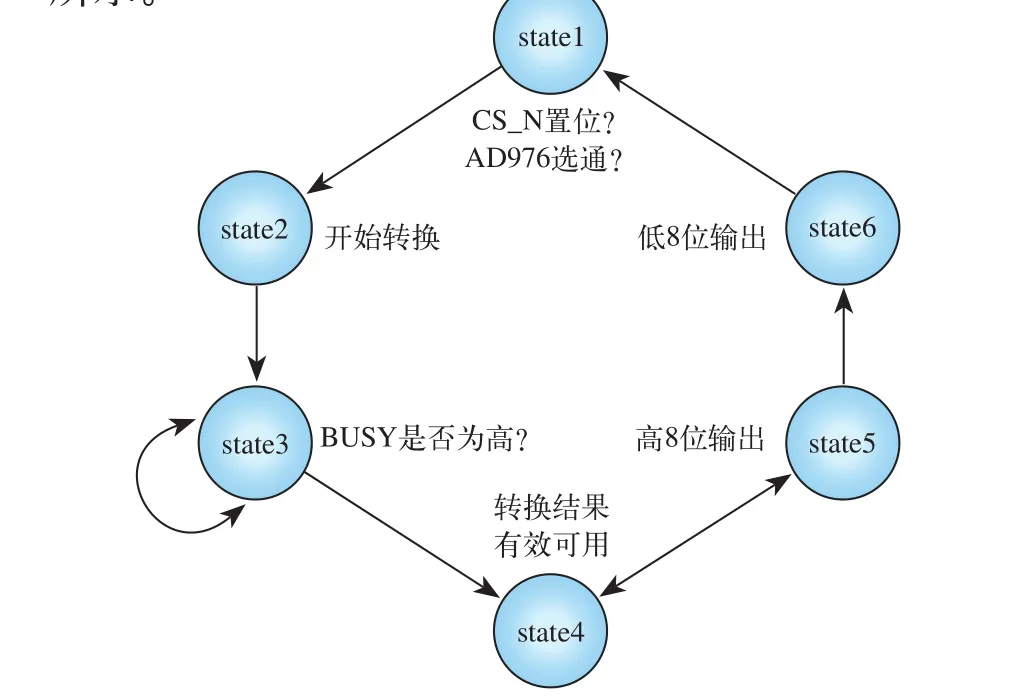

A/D转换电路采用一个有限状态机来产生AD976的工作时序。工作过程为:在state1状态时将CS_N置位,使其有效;进入state2状态,在R_ C信号的下降沿时,BUSY_N被置为低电平,输入信号进行转换;在state3状态,等待BUSY_N变为高电平,表明转换结束,在BUSY_N的上升沿将输出数据进行锁存;在state4状态下,R_C被置为高电平,此时将转换结果发到数据总线,数据有效可用;在state5状态时,BYTE为低电平,数据的高8位被输出,在state6状态时,BYTE为高电平,数据的低8位被输出,如此循环可以连续不断对模拟输入信号进行数据转换。AD976转换过程的有限状态机如图8所示。

图8 AD976转换过程的有限状态机

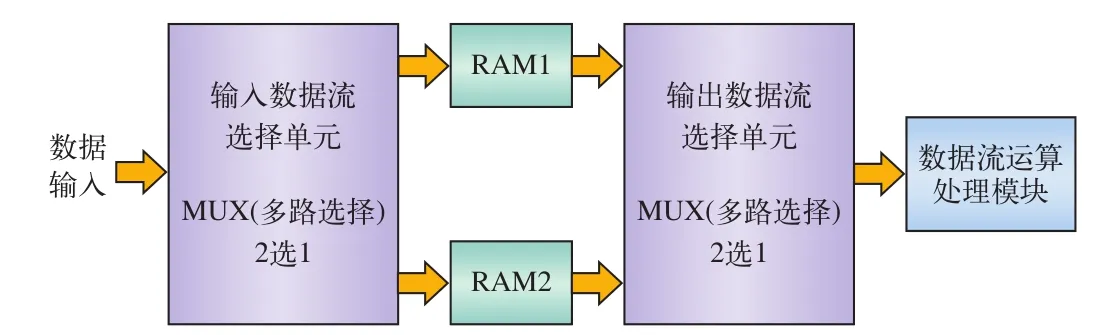

利用FPGA内部双口RAM存储单元将AD976读取的数据进行转换与存储,同时将数据输出到与其相连的单片机,实现数据的双向传输。本系统通过乒乓操作对两片RAM(RAM1、RAM2)轮流进行读,实现数据的缓冲和处理,乒乓操作方法如图9所示。

图9 乒乓操作流程图

乒乓操作的处理流程为:“输入数据选择单元”将输入数据流分配到RAM1和RAM2中。在第1个处理周期,输入数据流被缓存到RAM1中;在第2个处理周期,“输入数据选择单元”进行切换,将输入数据流缓存到RAM2,同时将RAM1缓存的数据通过“输出数据选择单元”的选择,送到 “数据流运算处理模块”进行运算处理;在第3个缓冲周期通过“输入数据选择单元”的再次切换,将输入的数据流缓存到RAM1中,同时将RAM2缓存的数据通过“输出数据选择单元”切换,送到“数据流运算处理模块”进行运算处理。如此循环,实现了数据转换和处理。

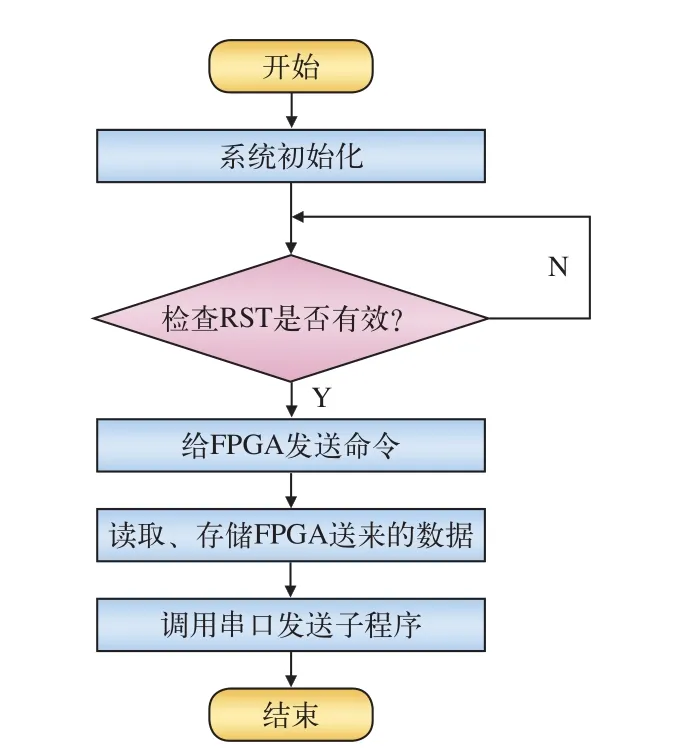

3.2 FPGA与单片机通信模块

为了更加充分地利用FPGA的系统资源,提高通信效率和稳定性,本系统在FPGA与单片机进行控制与通信时采用总线方式相连接,软件流程如图10所示。

图10 FPGA与单片机通信软件流程图

通过对单片机C8051F020总线时序的分析,当检测到RST信号有效后,地址锁存信号ALE将FPGA中高8位与低8位地址进行编码,组成16 位地址,然后根据C8051F020单片机的读写命令,实现对FPGA的读写操作,然后将数据给串口进行后续传输。

3.3 无线传输模块的软件设计

无线传输模块的主要内容是利用C8051F020的UART与MC37I芯片上的标准串口RS232进行通信。通过C8051F020的程序设计对GPRS模块MC37I发送指令实现对其控制。主要从以下两个方面来进行软件设计:(1)对单片机C8051F020初始化等程序设计;(2)C8051F020对GPRS模块MC37I芯片控制的程序设计,向其发送不同的AT命令,来完成MC37I初始化、GPRS网络登录、数据发送等。

通过专用下载线,利用JTAG接口,将程序下载到单片机C8051F020芯片中,可以在线实现对程序的编译和运行调试,即可实现GPRS模块MC37I的控制。

4 系统仿真、调试与验证

在系统全部设计完成后,必须对系统的各个组成部分及功能进行仿真、调试与验证,保证所设计的系统设计合理。

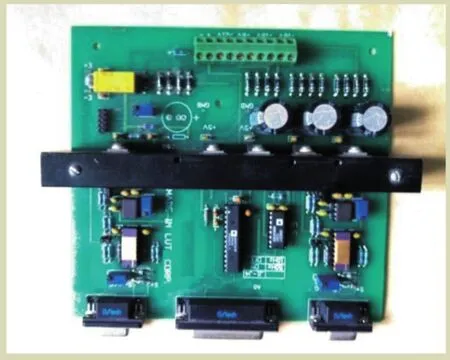

利用模拟开关ADG408和模数转换器AD976搭建的数据采集模块测试电路板如图11所示。

图11 ADG408和AD976搭建的数据采集板

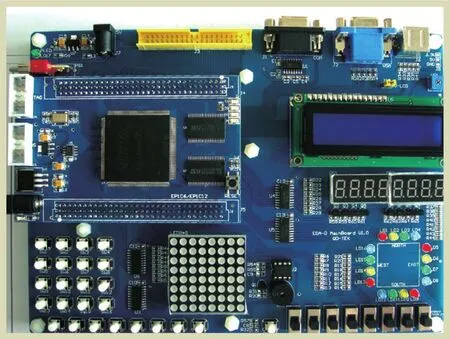

系统的控制核心FPGA EP1C12测试板如图12所示。

图12 EP1C12测试板

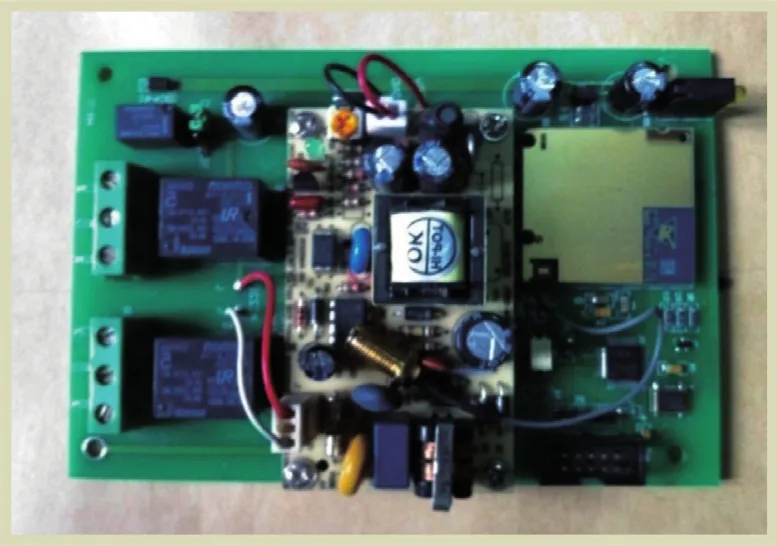

由C8051F和MC37I搭建的无线传输测试板,将SIM卡放入MC37I的SIM卡槽中,建立起该号码与指定号码通过GPRS网络建立起网络通路,通过单片机启动数据采集系统,并传输到网络上。无线传输测试板如图13所示。

图13 无线传输测试板

通过GPRS终端,发送短信息GPRS START给无线传输测试板,得到回复GPRSREADY,表明测试板与接收终端的GPRS连接正常,可以传输数据,接收终端软件生成以年月日为文件名的文件。在计算机上回放数据波形图。

5 结束语

轨边数据采集系统很好地解决了在铁路线路上复杂、恶劣测试环境进行数据采集的问题,发挥了灵活性和机动性的特点,满足了实际测试工作中对轨道上各种传感器数据的采集需要。在轨边数据采集系统的基础上,可以结合实际情况采用有线传输和海量存储等性价比更高的方式。本系统适合短期低速率数据采集的情况使用。

[1]柴雪松,朱兴红. 车辆运行状态监测系统(TPDS)在轨道负荷监测中的应用[J].铁道建筑,2008(11):93-95.

[2]徐 洋,李 彦. 基于Verilog HDL 的PFGA设计与工程应用[M]. 北京:人民邮电出版社,2009.

[3]张培仁,孙 力. 基于C语言C8051F系列微控制器原理与应用[M]. 北京:清华大学出版社,2009.

[4]李文仲,段朝玉. ARM9微控制器与嵌入式无线网络实战[M].北京:北京航空航天大学出版社,2003.

[5]葛亚明,彭永丰,薛 冰.零基础学FPGA[M]. 北京:机械工业出版社,2010.

[6]李东生,张 勇,许四毛.Protel99SE电路设计教程[M]. 北京:电子工业出版社,2007.

[7]何立民. 单片机应用系统设计[M]. 北京:北京航空航天大学出版社,1990.

[8]章坚武. 移动通信[M]. 西安:西安电子科技大学出版社,2003.

责任编辑 方 圆

Railway Track Edge Data Acquisition System

CHEN Tianzhu, LI Xuwei, LI Fuyong, QIN Ju

( Railway Engineering Research Institute, China Academy of Railway Sciences, Beijing 100081, China )

Aiming to the complexity of the railway line and the harsh test environment, the Railway Track Edge Data Acquisition System was designed. The System was used wireless transmission module to make transmission, the remote data acquisition of analysis and processing become true, and be less restricted by natural conditions. In this design, the Altera FPGA was used as the core controller. Through controlling the analog switch ADG408 and analog to digital converter AD976, the eight analog signals acquisition was implemented. At the same time, the wireless data control and transmission were implemented by using C8051F020 MCU to control MC37I module of GPRS network.

data acquisition; wireless transmission; Altera FPGA; micro control unit (MCU)

U213.4∶TP39

A

1005-8451(2015)06-0031-05

2015-01-07

陈天柱,助理研究员;李旭伟,副研究员。