基于BU—64843T8的1553B总线接口设计

张挺前 范祥辉 闫海明

摘要:提出了基于BU-64843T8的1553B总线接口设计方案。该设计采用了DDC公司最新发布BU-64843T8芯片作为1553B总线协议转换芯片,该芯片集成了1553B总线协议转换接口、1553B总线收发器和隔离变压器,实现了硬件设计小型化、低成本的目标。软件设计应用了传输层和驱动层的分层设计。

关键词:1553B总线;BU-64843T8;DSP

中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2015)02-0221-02

在上世纪70年代末,美军制定了MIL-STD-1553B标准(以下简称1553B)作为军用飞机的总线通信协议。因其高可靠性和实时性,1553B显现出强大的生命力,它不仅为第三代战斗机广泛使用,而且至今仍应用于以F22和F35为代表第四代战斗机。

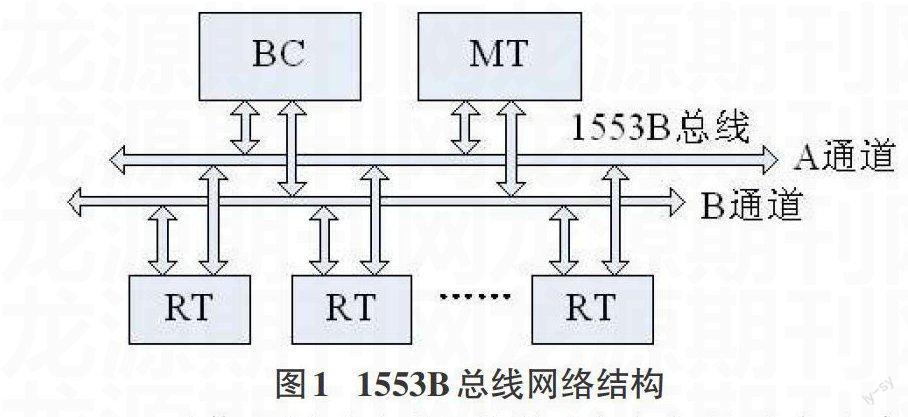

1553B标准规定了数字式时分制指令/响应型多路传输数据总线协议及其接口电子设备的技术要求,同时规定了多路传输数据总线的工作原理、总线上的信息流及要采用的电气和功能格式。1553B总线的网络结构如图1所示。总线控制器(BC)、远程终端(RT)和总线监控器(BM)作为总线上的通信终端。其中,BC控制总线数据的传输;BM监控总线上传输的信息;RT指所有不作为BC或BM的通信终端。

1553B通信必须还通过三种类型字来实现,它们有命令字、数据字和状态字。每一个字的长度都是20位,每个字的最前3位是同步位,指示新字的开始;后续的16位作为信息位,三种类型字的信息位都有各自的定义;最后1位的作用是整个字的奇偶校验位,标准规定奇校验指示正确。命令字由BC发送给RT,规定了一次信息传输的要求,远程终端地址指示BC要和哪个RT通信;“T/R”指示该RT是接收信息还是发送信息;子地址指出和该RT的哪一个子地址通信;数据字数量表示一次通信所传输的数据字字数。数据字可在BC与RT、RT与RT之间双向传输。状态字则由RT发给BC,用于响应命令字。

1 硬件设计

1.1 硬件架构

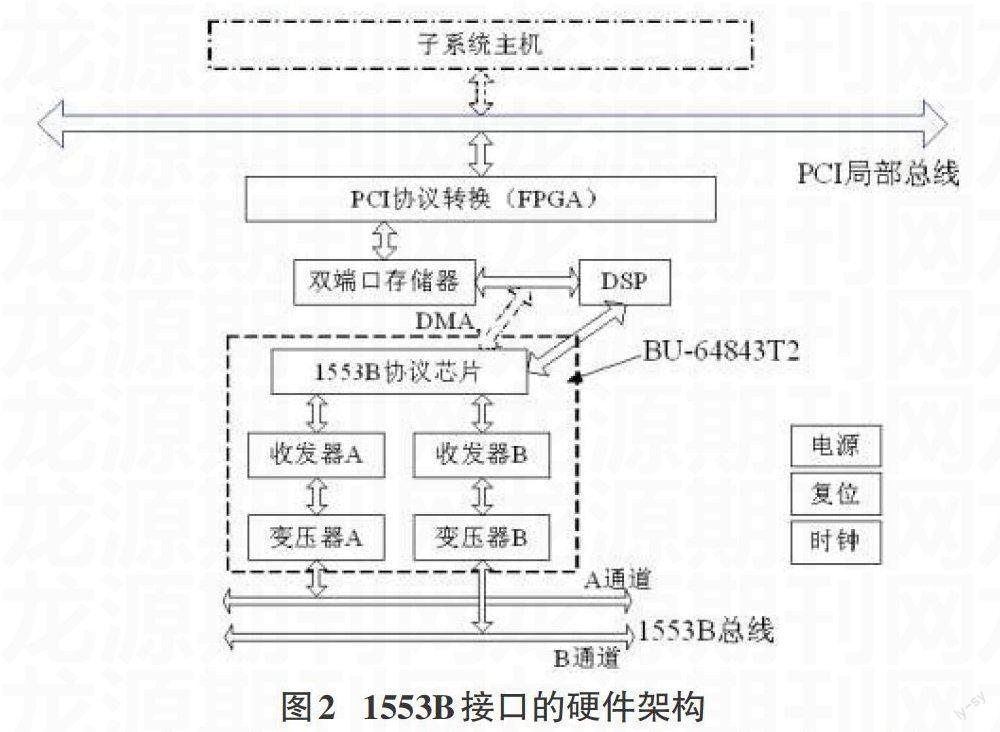

1553B通信接口的硬件架构如图2所示,,它由电源电路、复位电路、时钟电路、数字信号处理器(DSP)、1553B总线协议芯片、双端口存储器和FPGA组成。本接口通过PCI局部总线与子系统主机相连接。1553B通信接口采用了DDC公司最新的BU-64843T8,该芯片为设计者提供了一套完整的1553B多路数据总线的解决方案,在单芯片上不仅实现了BC、RT和BM功能,而且还集成了协议芯片、收发器和隔离变压器。与其他同类芯片(例如UT1553BCRTM)相比,BU-64843T8集成度更高、体积更小。通信控制器采用TI公司的TMS320F2812,它是一款32位定点数字信号处理器(DSP),能在一个时钟周期内完成32×32位的乘法运算,工作时钟频率最高可达150MHz。在本设计中,这个DSP工作在100MHz,这个时钟是由外部20MHz晶振提供,再由DSP内部5倍频产生。DSP承担1553B总线传输层任务,包括控制BU-64843T8的工作状态、通信错误处理和响应子系统主机命令等功能。本接口通过PCI局部总线与子系统主机相连接,采用PCI局部总线使得子系统主机能够和多个1553B总线接口连接,因此本设计具有灵活的扩展能力。PCI协议转换由Xilinx公司的FPGA XC5VLX50-1FFG324I实现,这款FPGA体积小、功耗低。子系统主机和1553B总线数据交换由双端口存储器实现,作为来自FPGA和BU-64843T8之间的收发数据缓冲区。

子系统主机向1553B总线发送数据的过程如下。子系统主机向PCI总线发送数据,FPGA则将PCI总线上的数据通过协议转换后放在双端口存储器的左端。DSP从双端口存储器右端读出这些数据中的指令,根据指令控制,控制BU-64843T8的工作状态。接下来BU-64843T8读出双端口存储器右端的数据,把这些数据处理成转换成曼彻斯特编码的命令字、数据字和状态字,再通过收发器和变压器变成1553B差分信号。子系统主机接收数据的过程则和发送过程方向相反。

1.2 处理器和BU-64843T8的硬件接口设计

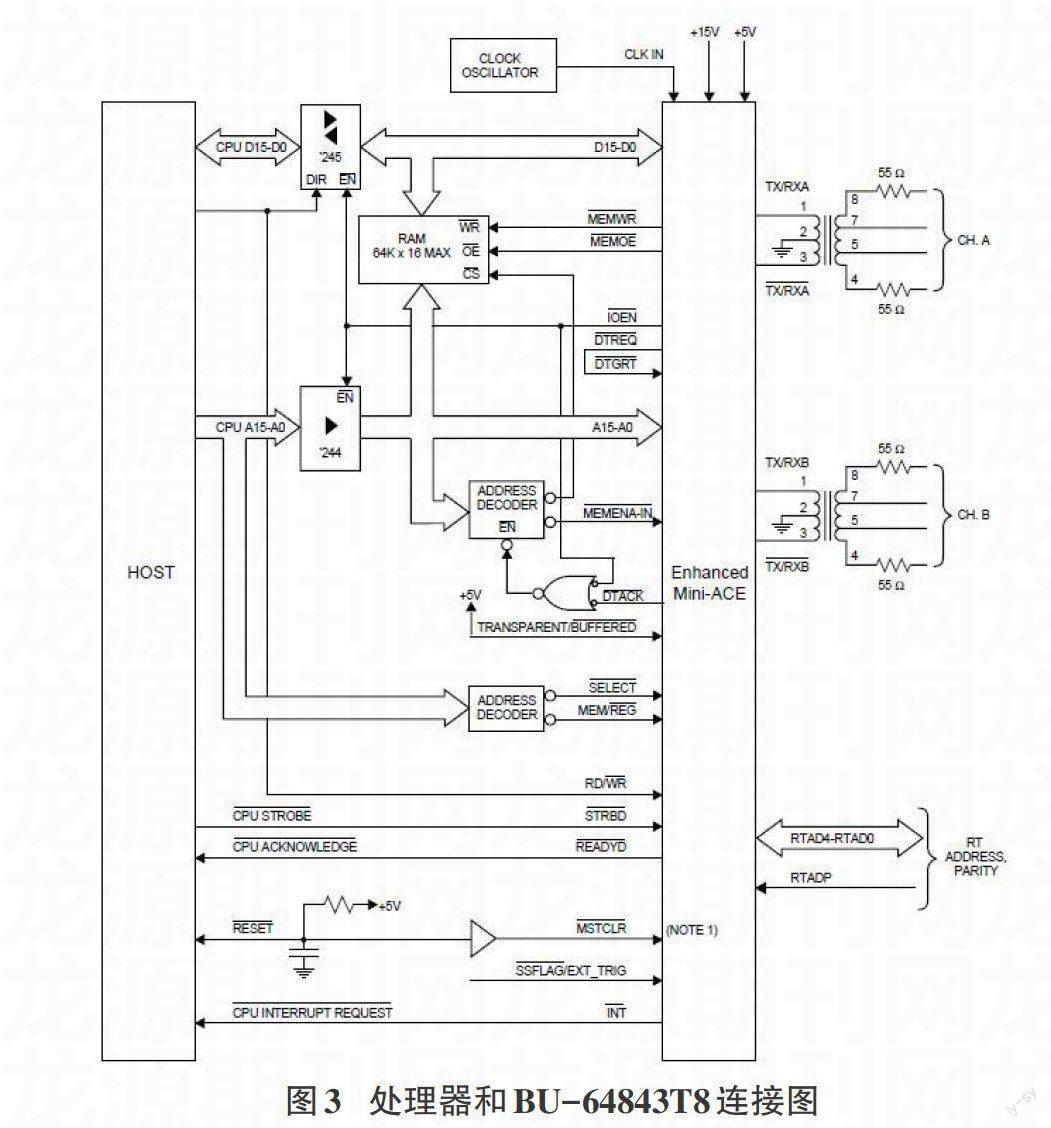

BU-64843T8(Enhanced Mini-ACE)在本方案中与处理器(HOST)采用透明模式连接,连接方式如图3。

因为BU-64843T8工作在透明模式下,所以引脚“TRANSPARENT”必须接高。本设计中的处理器(HOST)就是DSP。DSP和BU-64843T8共同使用一片64k字(16位)的外部RAM,但是需要隔离DSP的总线和BU-64843T8的总线。通过隔离总线,在DSP能够使用自己总线的同时,BU-64843T8可以读写这片外部RAM。而隔离总线通过使用“245”和“244”三态缓冲器来实现。外部RAM的片选信号“/CS”(外部地址解码器的输入)由“DTACK”信号和“IOEN”信号生成,生成的逻辑由FPGA来实现。

2 软件设计

本文设计的1553B通信接口软件由传输软件和驱动软件组成。

传输软件固化在DSP内部的Flash中,主要实现对1553B总线不同类型消息的处理、出错信息的处理、同步、启动测试。传输软件实现通信管理和数据传输功能,传输软件由上电初始化、命令处理和中断服务三大部分组成。上电初始化主要完成硬件初始化设置和自测试,上电初始化包括DSP初始化,上电自测试,双端口存储器内信息的初始化和ACE初始化等模块。命令处理主要根据驱动软件的命令完成相应服务,命令处理主要包括初始化、启动、停止、自测试等模块。中断服务处理主要包括外部时钟中断、看门狗时钟中断、消息结束中断处理。

驱动软件驻留在子系统主机上,是应用软件与传输软件的接口软件,为实现应用软件的管理功能,驱动软件通过双端口存储器与传输软件之间进行信息交互,控制1553B总线接口的初始化、启动、停止、自测试、1553B总线接口和子系统主机的数据交换。子系统主机应用程序通过调用1553B总线接口驱动程序中的标准API函数接口使用1553B总线接口功能。驱动软件按其功能可分为状态控制程序、系统控制程序、时间控制程序、消息控制程序和1553B总线接口中断服务程序。其中状态控制程序包括MBI_GoDrv、MBI_StopDrv、MBI_BitDrv等函数用于控制总线接口的状态转换;系统控制程序包括MBI_SetFuncDrv、MBI_InitDrv、MBI_ResetDrv等控制总线接口的初始化、运行模式、复位等;消息控制程序包括MBI_ReadBlock、MBI_WriteBlock、MBI_RefreshBlock等,主要用来读写消息;时间控制程序包括MBI_SetRealTime、MBI_ReadRealTime和MBI_ReadDeltaTime,主要用来维护系统时间。总线接口驱动软件提供中断服务函数挂接处理,当中断到达时,通过回调函数的方式调用主机程序中中断处理函数处理中断。

参考文献:

[1] GJB289A-1997 数字式时分制指令/响应型多路传输数据总线[S]. 国防科学技术工业委员会, 1997.

[2] 赵月琴.基于BU-61580的嵌入式1553B终端的设计[J]. 航空兵器,2004( 4) : 28-31.

[3]苏奎峰,吕强.TMS320F2812原理与开发[M].北京:电子工业出版社,2005.

[4] DDC.MIL-STD-1553B Designers Guide[Z].2003.

[5] ACE/ Mini-ACE Series BC/RT/MT Advanced Communication Engine Integrated 1553 Terminal Users Guide [Z] . DDC,1999.