基于Camera Link数字相机的实时小型化系统

巩稼民, 陈 博, 曾祥忠

(1.西安邮电大学 电子工程学院, 陕西 西安 710121; 2.西安中川光电科技有限公司, 陕西 西安 710075)

基于Camera Link数字相机的实时小型化系统

巩稼民1, 陈 博1, 曾祥忠2

(1.西安邮电大学 电子工程学院, 陕西 西安 710121; 2.西安中川光电科技有限公司, 陕西 西安 710075)

设计一套基于Camera Link数字相机的实时小型化系统。根据Camera Link协议以及Bayer变换算法,采用Cyclone III 系列FPGA EP3C40F484芯片,通过采集输入的Camera Link信号,异步FIFO与单片SDRAM方式进行数据缓存,利用ADV7123芯片实现8位数模转换,输出1024×768 ×60Hz的VGA信号。实验结果表明,该系统可以不通过携带Camera Link图像采集卡的计算机,完成对Camera Link 信号的转换并直接显示图像,并实现彩色与黑白模式切换。

实时小型化;Camera Link;FPGA;SDRAM 控制器;Bayer

Camera Link数字相机逐渐成为机器视觉方面的热点,相比于千兆网、USB2.0以及IEEE 1394接口,Camera Link具有高传输速度、高分辨率、强稳定性、通信协议灵活简单等特点,可应用于军事侦查、光学遥感和飞船预警等领域[1-2]。而基于Camera Link数字相机的实时显示系统主要是通过载有Camera Link图像采集卡的计算机进行间接显示。目前Camera Link图像采集卡是基于PCI总线或者PCI Express总线进行数据的控制与传输[3-5],虽然系统的高速实时性得到满足,但体积较为庞大,使用携带不方便,对于空间要求严格的地点并不适合,其灵活性较低,具有一定的局限性[6-7]。

为了实现一种基于Camera Link数字相机高速实时小型化系统,就需要基于Camera Link信号采集原理、Bayer算法以及FPGA编程技术,在不通过计算机的情况下完成对Camera Link数据及控制信号进行图像采集、图像缓存、信号转换并显示等一系列数据处理。图像缓存模块可以通过双SDRAM[8]或者双SRAM[9]乒乓操作进行高速大容量数据的处理,本系统则采用单片SDRAM加异步FIFO的方法实现,另外在图像的显示方面增加了彩色/黑白模式的变换。

本文采用STC-CLC83A型号彩色Camera Link数字相机,根据DS90CR288解码芯片采集Camera Link信号,基于EP3C40F484芯片完成控制器的设计,将输入的有效像素1 024×768×30 fps的Camera Link信号缓存到单片SDRAM,并通过数模转换芯片ADV7123进行转换,输出1 024×768×60 Hz的标准VGA信号,外置拨码开关进行输出图像模式选择。

1 Camera Link协议与Bayer算法

1.1 Camera Link协议

Camera Link协议是基于低压差分信号(Low Voltage Differential Signaling,LVDS)数据传输信号之上的,LVDS信号在传输过程中产生一对电压值大小不同信号,在接收时对这对差异信号进行相应的信号解码成TTL信号,从而得到原始数据信息。

STC-CLC83A数字相机采用Camera Link配置下的Base型结构,因此选用单片DS90CR288解码芯片作为Camera Link信号接收器。从MDR26接口发送包含图像信息的4路LVDS串行数据流和1路作为高速数据同步的LVDS时钟流。5路LVDS信号在标准Camera Link电缆中传输并在DS90CR288接收到信号时将其串并转换,解码恢复成28位的并行数据进行后续图像处理[10],如图1所示。

图1 Camera Link传输协议

1.2 Bayer算法

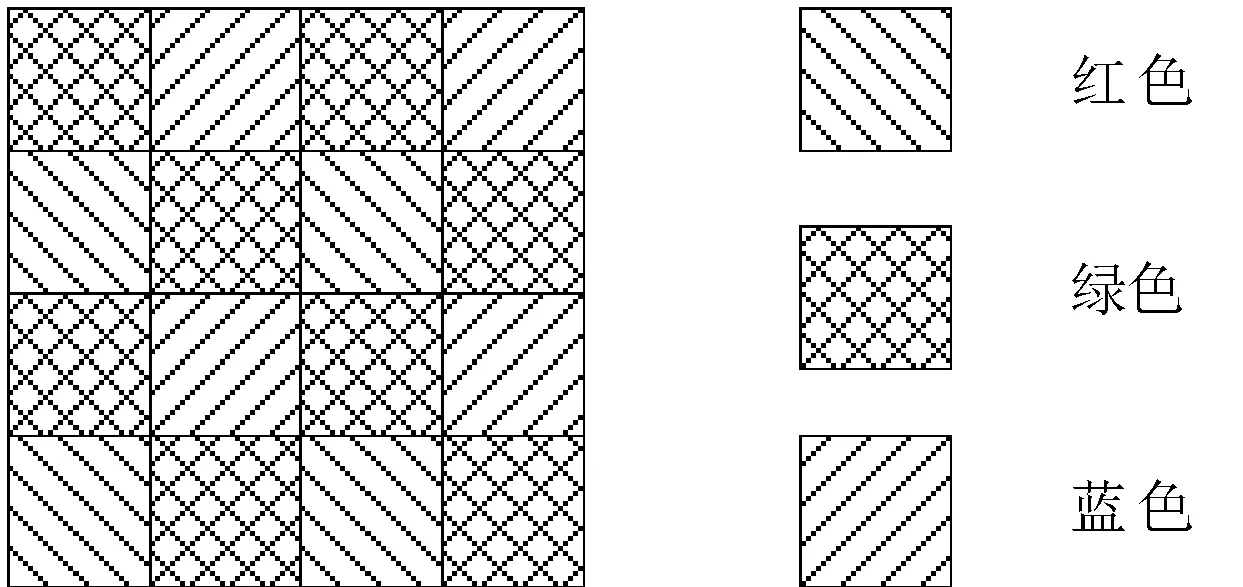

还原彩色图像通常是在CCD传感器的表面按一定顺序排列的镀含有红绿蓝三色的马克膜,对接收的数据进行一定的算法来获取彩色图像。Bayer CFA模板是目前广泛采用的彩色图像还原模板,它交替使用一组红绿滤镜和一组绿蓝滤镜,其中绿色像素占据总像素的50%,红色像素占据25%,蓝色像素占据25%,如图2所示。

经过Bayer CFA模板采集的图像数据因为绿色像素分量占了全部像素的一半,所以不经过算法处理,图像在整体的显示效果上会呈现绿色。在算法上使用占用逻辑资源最少的2×2块的Bayer模板。

图2 Bayer CFA模板

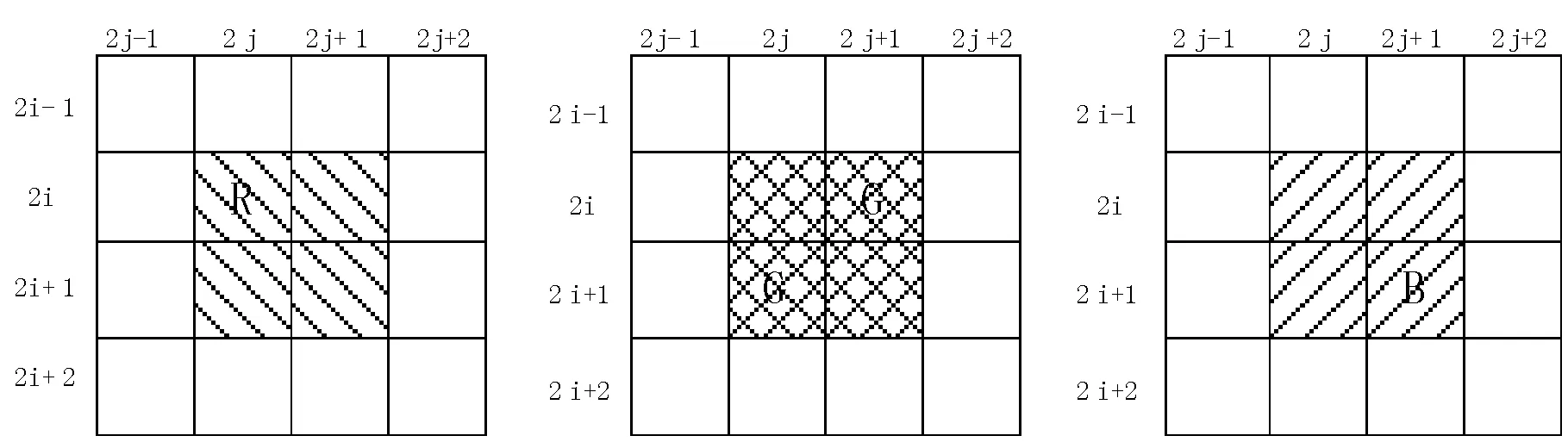

在2×2块的Bayer模板基本单元如图3所示。内对缺失的R、B分量完全使用相同颜色的分量,而对缺失的G分量使用均值方法,通过颜色分量辅助实现色彩还原。程序基本设计思路为在2×2单位块内的4个像素单元具有相同的R值和B值,第1列和第2列的两个像元的G值为两像素的平均值[11-13]。

图3 2×2块的拜尔模板基本单元

2 实时小型化设计

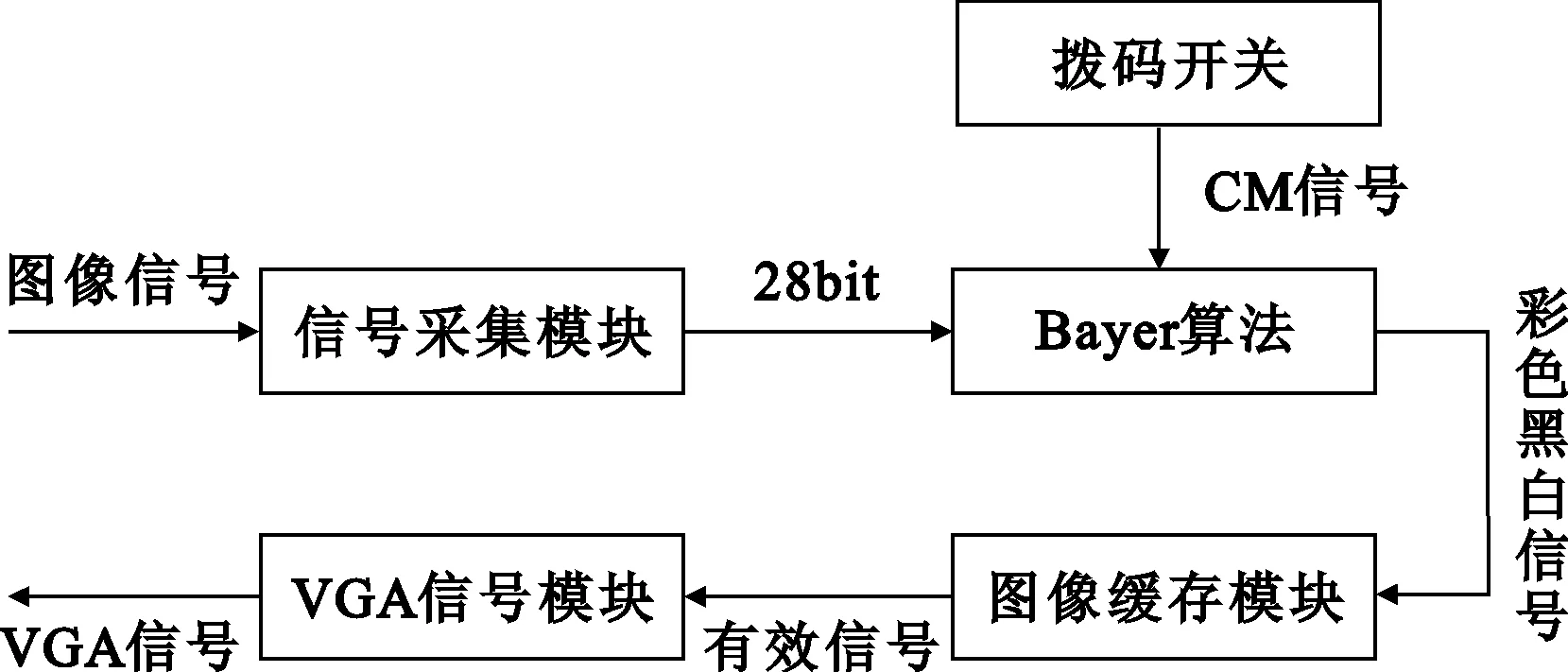

系统的总体设计由信号采集、图像缓存、Bayer变换以及VGA信号模块4个部分组成,如图4所示。

图4 总体设计框图

2.1 信号采集模块

相机通过MDR26输出的5路LVDS串行差分信号经DS90CR288A芯片恢复相机图像信号,由芯片解码输出1路时钟信号和28路数据信号,其数据信号包括24bit图像有效数据信号和包含帧有效信号FVAL、行有效信号LVAL、数据有效信号DVAL、预留信号SPARE的4路控制信号。当控制器检测到行/场同步信号同时有效的情况下,以相机的输入频率作为信号采集模块的像素时钟,进行接收图像数据的采集工作。

2.2 实时Bayer转换

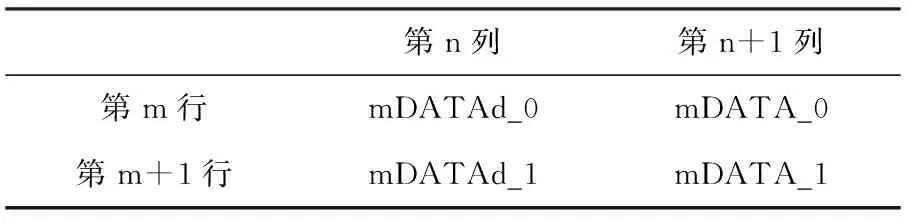

相机的输出数据按2×2 Bayer模板设4个变量,分别为mDATA_0,mDATA_1,mDATAd_0和mDATAd_1。4个变量组成了一个空间模板,mDATAd_0位于模板左上方,如表1所示。

表1 2×2 Bayer空间模板

模板中4个变量必然包含GRBG 4个色彩分量,根据2×2的Bayer变换模板的色彩变换原理,在模板中任意像素取邻域的红色像素值、蓝色像素值和两个绿色像素的平均值。在程序设计中,不同的位置采取不同的取值方法,其中mCCD_G的值在程序处理时再进行均值,部分程序设计为

if ({iY_Cont[0],iX_Cont[0]} == 2'b00)

begin

mCCD_R <= mDATAd_0;

mCCD_G <= mDATA0+mDATAd_1;

mCCD_B <= mDATA_1;

end

else if…..

为了实现彩色Camera Link数字相机灵活的优势特点,并符合特定场所的要求,设计了通过拨码开关调节CM信号实现黑白及彩色信号切换,部分程序为

采用SPSS 25.0统计学软件对该次研究数据进行统计处理,其中计量资料为血糖水平控制情况,用(±s)表示,进行t检验,治疗效果为计数资料,用[n(%)]表示,进行χ2检验。P<0.05为差异有统计学意义。

assign oRed = CM?rRed : iDATA ;

assign oGreen = CM?rGreen[10:1] : iDATA ;

assign oBlue = CM?rBlue : iDATA ;

2.3 高速SDRAM缓存控制

采用单片MT48LC8M32B2(8M×32)型号、容量为256Mb、工作电压为3.3V的SDRAM芯片,系统时钟同步运行的接口方式。其包括32bit Data Bus, 4banks (BA0~BA1),每Bank的64Mb的存储架构是4096行×512列×32bit,每个Bank存储单元通过行和列寻址,最终完成存储单元的寻址工作。其SDRAM芯片引脚有DQ0~DQ31(数据输入输出引脚)、A0~A11(地址输入引脚)、CLK、CKE、CS(芯片选择)、RAS(行地址选择)、CAS(列地址选择)、WE(写使能)、BA0~BA1(Bank地址输入信号引脚)、DQM、VSS、VDD等引脚。设计程序通过初始化、预充电、行激活、读/写操作、自动刷新等操作控制SDRAM工作。在模式寄存器操作命令下进行主要工作参数设置,其中包括Burst Length、Burst Type、CAS Latency以及OP Code。

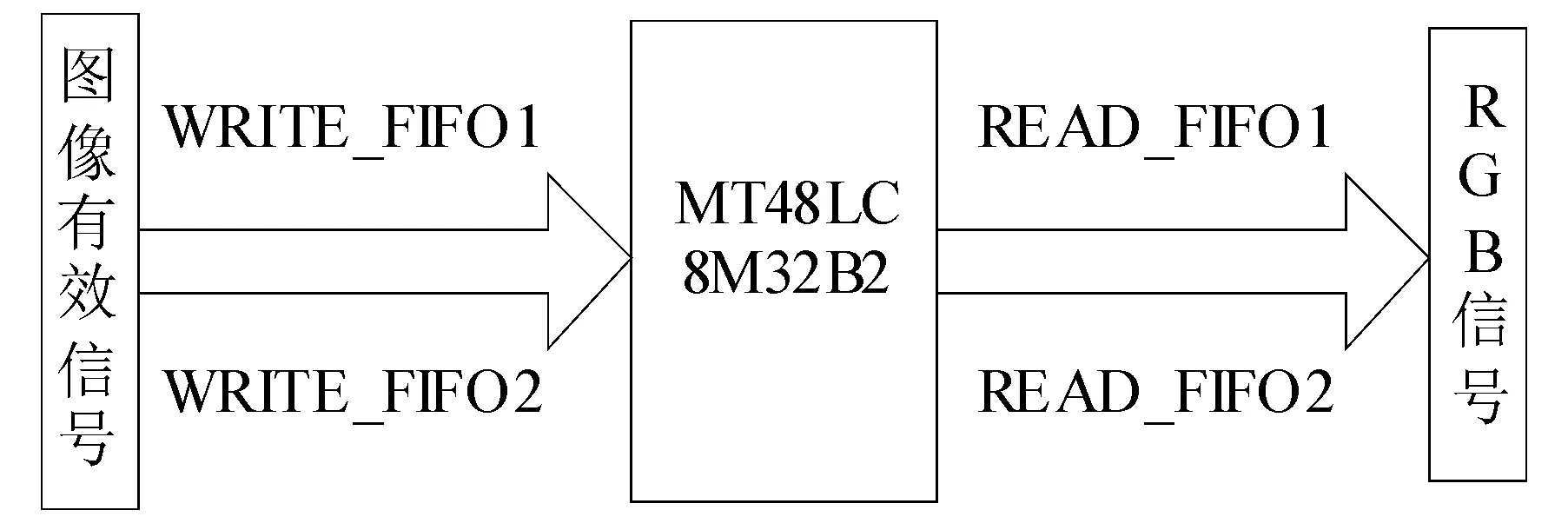

因为Camera Link数字相机输入的图像数据量大,速率快,所以采用异步FIFO实现乒乓缓存的机制进行数据缓存,如图5所示。

图5 SDRAM模块设计

为避免Camera Link信号(30fps)与VGA标准(60Hz)在帧频上的干扰,首先将相机采集的图像数据缓存到FIFO1中,当FIFO1写满数据后,SDRAM开始存储FIFO1的数据,在FIFO1读操作的同时FIFO2进行相机数据的写操作,当FIFO1读空时等待FIFO2的写满信号,当FIFO2的写满信号有效时进行FIFO1的写操作。在写FIFO2的同时对FIFO1进行读操作,当读操作读空时等待FIFO2的写满信号,当写满信号有效时再对FIFO1进行写操作,同时对FIFO2进行读操作。读写切换可以由FIFO的写满和读空信号来控制,将图像缓存到单片的SDRAM中,便于后续的图像显示处理。而在读取图像有效时同样利用异步FIFO的乒乓操作,进行缓存RGB信号提取并结合VGA模块产生的行/场同步信号输出信号。

接收的Camera Link相机时钟信号为60MHz,而标准XGA信号的时钟频率为65MHz,利用50MHz晶振倍频,将SDRAM的工作时钟控制到166MHz,将有效图像信号在SDRAM中进行缓存,最大限度地保证在写入以及读取图像信号时保证数据无失真。

2.4 VGA模块输出

选用ADV7123芯片作为视频D/A转换器,由于相机采用8位数据流,所以只用到ADV7123高8位端口。经过ADV7123转换后的3路模拟数据结合行、场同步信号,传输给VGA接口显示器进行显示[14-16]。

根据VESA 1024×768×60Hz的时序标准,其行频要求为48.363kHz,场频要求为60Hz,像素时钟为65MHz,有效行像素周期数为1024,有效场像素周期数为768,而FPGA核心板的晶振为50 MHz的时钟信号,所以对其进行PLL锁相环产生像素时钟。

行周期数= 65MHz÷48.363kHz = 1344,

帧周期数= 48.363kHz÷60Hz=806,

行消隐周期数=1344-1024=320,

场消隐周期数=806 -768=38。

在显示信号消隐期间不进行SDRAM中缓存图像信息的读取,只有在输出1024×768有效像素时读取信号。

构建hsync行像素计数器,当hsync=1344时清零,而当行脉冲计数≥h_blank(=320)时,行同步信号输出高电平1有效,其余在h_blank消隐期内输出低电平0,从而以行计数器hsync信号为单位构建场像素计数器vsync。当场计数值≥v_blank(= 38)时输出有效信号高电平1,在v_blank消隐期内的输出低电平0,当vsync (=806) 场同步信号时,场计数器清零以此作为场同步信号vsync。

3 系统测试及结果

在防静电实验台上,将STC-CLC83A数字相机和显示器连接于系统(如图6),输入5V+电压,进行测试。

图6 系统实现效果

在显示器上显示1024×768×60Hz 实时图像,并对目标区域进行彩色/黑白图像信号的相互切换,如图7所示。

(a) 黑白 (b) 彩色

图7 图像切换效果

测试结果表明,该系统已经实现了基于Camera Link数字相机的小型化要求,支持Camera Link的高速稳定信号的传输,满足特定场所需求,替代Camera Link图像采集卡进行图像直接显示。

4 结束语

该小型化实时显示系统针对于特定场所对空间以及实时性的要求,实现了摒弃在计算机工作环境下的Camera Link数字相机的直接显示。通过Camera Link图像高速采集在FPGA系统中进行SDRAM数据缓存模块和VGA信号产生与输出,采用拨码开关实现彩色与黑白信号的切换控制,不仅保证Camera Link实时系统的高速稳定的特点,而且缩小体积,提高了系统的灵活性。

[1] 沈鸽,王美娇,嵇晓强.基于Camera Link 的视频图像采集与传输系统[J]. 嵌入式与SOC,2011(8):99-100.

[2] 陈炎斌,金刚.基于Camera Link标准的DSP_FPGA高速实时数字图像处理系统设计[J]. 现代科学仪器,2010, 12(6):61-63.

[3] 王雪松.基于PCI9054的Camera Link图像采集卡设计[J].仪器仪表用户,2009(16):64-67.

[4] 钟文峰. 基于 Camera Link 图像采集卡的设计与实现[D]. 成都:电子科技大学, 2011:9-12.

[5] 黄影. 基于 PCIe 总线的 Camera Link 图像采集卡设计[D]. 大连:大连理工大学, 2013:9-12.

[6] Zhao Wenge, He Huiming. FPGA-based video image processing system research [C]//Chengdu:Computer Science and Information Technology,2010:680-682.

[7] Benkrid K, Crookes D, Smith J, et al. High Level Programming for FPGA Based Image and Video Processing using Hardware Skeletons[C]//Rohnert Park:FCCM01, 2001:219-226.

[8] 孙春凤, 袁峰,丁振良.基于FPGA 的多通道高速CMOS 图像采集系统[J]. 计算机工程与应用,2008, 44(21):46-49.

[9] 董亚则,王顺.高速数字图像采集显示系统的设计与研究[J].吉林大学学报,2011,29(6):543-547.

[10] 于建军,吴志勇. Camera Link在视频控制系统中的应用[J]. 光机电信息,2011,28(5):42-45.

[11] 王渊博.基于FPGA的Bayer格式实时彩色恢复系统研究[D].北京:中国科学院大学,2013:15-28.

[12] 孙辉,柏旭光,孙丽娜,等.Bayer图像色彩还原线性插值方法[J]. 液晶与显示,2013,28(3):418-424.

[13] 莫迪涵, 杜慧敏, 沈绪榜. 基于线性插值法图像缩放的设计与 FPGA 实现[J]. 西安邮电大学学报, 2013,18(3): 52-55.

[14] 王鸣浩,陈涛,吴小霞.基于Camera Link接口的高帧频数字图像采集显示系统[J].微电子学与计算机,2011, 28(3):149-152.

[15] 刘慧,朱勇.基于FPGA 的VGA 彩色图片的显示[J]. 科技向导,2011(20):84-85.

[16] 杨小勇,葛彦麟,毛瑞娟. 基于FPGA+A/D的数据采集设计及验证[J]. 西安邮电学院学报, 2011,16(1): 98-102.

[责任编辑:祝剑]

《西安邮电大学学报》版权声明

为适应我国信息化建设的需要,扩大刊物影响,拓宽信息交流渠道,本刊已加入“中国知网CNKI系列期刊数据库”、“中国核心期刊(遴选)数据库”(万方数据——数字化期刊群)、“中国期刊网”等数据库。本刊已许可以上数据库以数字化方式复制、汇编、发行、信息网络传播本刊所载文章的全文信息。稿件一经刊登,将在本刊稿酬中一次性支付著作权使用报酬(包括印刷版、光盘版和网络版等各种使用方式的报酬)。作者向本刊提交文章的行为即视为同意我刊上述声明。

西安邮电大学学报编辑部

A real-time miniaturization system based on Camera Link CCD camera

GONG Jiamin1, CHEN Bo1, ZENG Xiangzhong2

(1.School of Electronics Engineering, Xi’an University of Posts and Telecommunications, Xi’an 710121,China;2.Xi’an Mid-River Photoelectric technology Co.,Ltd, Xi’an 710075,China)

A design of the real-time miniaturization system is designed in this paper. In this system, Cyclone III (series FPGA EP3C40F484) is used to design a real-time display system and asynchronous FIFO and SDRAM are adopted to frame buffer and then transform Camera Link signal input to a 1024×768×60Hz format output. At the meantime, ADV7123 chip is used to transform the signal into an 8 digits format model and the output signals are displayed on a monitor through VGA port. Experiment result shows that this system can transfer and display images through Camera Link without the help of images capture cards. Thus, it allows the images to be switched from black and white to colour.

real-time miniaturization system, Camera Link, FPGA, SDRAM, Bayer

2015-01-16

西安邮电大学研究生创新基金资助项目(ZL2013-22)

巩稼民(1962-),男,博士,教授,博导,从事光电技术研究。E-mail:gjm@xupt.edu.cn 陈博(1989-),男,硕士研究生,研究方向为光电图像处理。E-mail:tooth_of_dark@sina.com

10.13682/j.issn.2095-6533.2015.03.018

TN27

A

2095-6533(2015)03-0100-05