水站监控系统的Modbus通信协议设计

陈佳晖 衷卫声 王文海

(南昌大学信息工程学院1,江西 南昌 330031;浙江大学信息学部2 ,浙江 杭州 310027)

水站监控系统的Modbus通信协议设计

陈佳晖1衷卫声1王文海2

(南昌大学信息工程学院1,江西 南昌 330031;浙江大学信息学部2,浙江 杭州 310027)

针对水站监控系统中存在的可扩展性、成本高等问题,将FPGA技术应用于水站监控系统。对水站监控系统进行了总体结构设计,控制器与分析仪表的通信采用Modbus协议,通过仔细分析该协议后,用FPGA的模块化设计方法,将该协议划分为波特率发生器模块、接收模块、发送模块和CRC校验模块,并用Verilog HDL语言完成了对各模块的设计和功能仿真。实验仿真结果表明,该设计满足Modbus协议的通信要求,在工业通信领域具有一定的实用价值。

FPGA Modbus 通信协议 水站监控 Verilog HDL

0 引言

21世纪以来,我国的工业化水平得到了迅速提高,面对日益严重的水污染及水资源短缺等问题,监测江河、湖泊、水库等地表水的水质成为当今环境监测的研究热点[1]。随着计算机技术及传感器技术的快速发展,监控技术的自动化水平越来越高,参数的测量精度也越来越高,系统变得更加灵活。由于水站分布在不同地域,工作环境比较恶劣,并且针对不同的水环境有不同的监测指标,因此,控制中心与现场仪表之间的通信面临着可扩展性及可靠性的问题。

现场可编程门阵列(field-programmable gate array,FPGA),已从最初的一千多个逻辑门发展到现在的百万门以上[2]。用户可通过编程将内部的逻辑单元组成任何复杂的数字系统,并支持动态可重构技术,应用领域越来越广,如SOPC技术、嵌入式系统开发、高性能数字信号处理系统、可重配置计算机系统、基于网络的可从配置技术、IP核的开发和复用技术等。

Modbus以其扩展性好、兼容性强、可靠性高和免费开放等优点得到了广泛应用[3]。目前主要是通过单片机或PLC实现Modbus协议,而本文研究了一种基于FPGA的Modbus通信协议实现方案。由于FPGA具备开发周期短、速度快等优点,该方案具有很好的通用性和实用价值。

1 系统总体概述

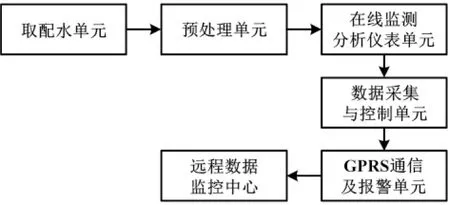

水站监控系统的总体结构如图1所示。

图1 水站监控系统的总体结构

取配水单元主要负责水样的采集,并将水样通过取样水泵输送至沉砂分离单元和分析仪器单元;在线监测分析仪器单元的任务是针对不同的水质参数检测要求,选择合适的水质在线分析仪表,并将测量结果及工作状态等信息发送给FPGA。为便于通信,这些仪器都支持Modbus通信协议[4]。GPRS模块负责数据的远程传输和报警功能;远程数据管理中心负责对监测数据进行实时显示和存储,为工作人员提供可视化的监控管理平台。

数据采集与控制单元是系统的核心部分,与以往的监控系统相比,该系统以FPGA作为现场控制单元。它主要负责对各分析仪器的监测数据进行采集,分析仪器与FPGA之间的通信采用Modbus协议;FPGA会将采集的数据发给GPRS模块,以实现远程通信功能;现场设备执行检测、取样及清洗等功能也是由FPGA实现的。本系统适用于地表水水域或断面水质的在线检测,可供有关环境监测部门参考和使用。

2 Modbus通信协议介绍

Modbus协议是当今自动化协议中使用最普遍的一种通信协议,它是一种主从式点对点通信协议,通过该协议,控制器之间、控制器经由网络(如以太网)和其他设备之间可以进行通信,现在己经成为一种通用的工业标准通信协议。有了Modbus协议,不同厂商生产的控制设备可以组成工业网络,进行集中监控。Modbus串行链路系统可以使用RS-485、RS-232两种物理接口,其中RS-485两线制接口最常用[5]。为了提高通信模块的稳定性和抗干扰性,接口芯片与FPGA核心模块之间需要采用高速光耦进行隔离,并采用屏蔽双绞线作为通信介质。

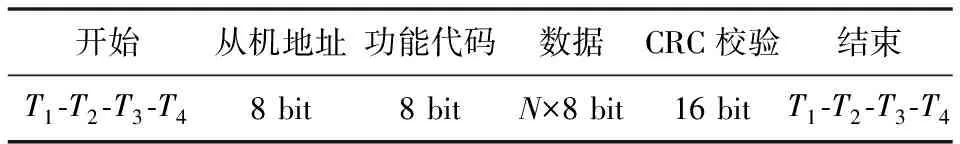

在标准Modbus通信协议中,控制器可以使用ACSII或RTU通信模式进行通信[6]。当控制器使用ASCII模式通信时,消息中的每个8位字节都要用2个ASCII字符发送,这种方式的主要优点是字符间的时间间隔可以达到1 s而不会产生错误。以RTU模式通信时,消息中的每个8位字节包含2个4位的十六进制字符。该模式的优点是,在相同的波特率下,可以比ASCII模式发送更多的数据[7]。本设计采用RTU模式进行通信,其消息帧格式如表1所示。

表1 RTU模式的消息帧格式

在RTU模式中,规定消息以至少3.5个字符静止时间表示开始,当确定了波特率后,很容易计算得到这个静止时间。各区发送的字符均采用十六进制,第一个数据区是从机的地址,在同一个网络中只允许有1台主机和最多247台从机,从机的地址编码范围是1~247(十进制)。当从设备接收到第一个地址数据时,每台设备都要立即对它解码,以判断是否是自己的地址;第二个数据区代表功能码,Modbus通信协议定义了255个功能码,但大部分功能码用于异常应答;第三个数据区代表数据信息,它包括各种数据地址、寄存器数量、数据信息和数据的字节数;第四个是错误校验码区,本系统采用循环冗余校验CRC16;最后是至少3.5个字符静止时间,代表消息的结束。整个消息必须连续发送,如果发送消息时出现大于1.5个字符静止时间,则接收设备会刷新不完整的信息,重新接收消息数据。

3 Modbus通信协议设计

3.1 整体功能模块划分

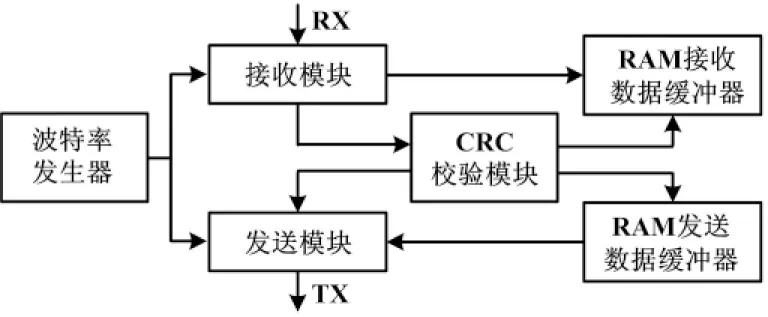

Modbus通信协议是通过FPGA来实现的,根据Modbus通信协议的要求,采用自顶向下的设计方法,将整个通信模块划分为若干个功能模块,如果功能模块还比较复杂就再进行细化,以实现模块的功能最简化,然后用Verilog HDL语言实现各模块的功能[8]。采用模块化的设计思想,不仅使设计更加简单,而且使代码维护和升级变得更加方便。Modbus通信协议的顶层模块如图2所示。

图2 Modbus协议的FPGA功能模块划分

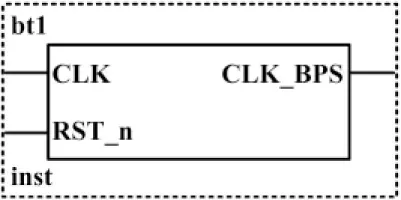

3.2 波特率发生器

波特率发生器其实就是一个分频器,根据系统的时钟频率和要求的波特率算出波特率分频因子,并以此作为分频器的分频数,它的主要功能是控制Modbus协议的数据传输速率。本系统的FPGA控制板使用的是50 MHz的晶振,波特率采用Modbus协议推荐的19 200 bit/s,这样就可以得到传输一位数据需要的时间长度为2 604个时钟脉冲周期,半周期为1 302。波特率发生器的模块图如图3所示。

图3 波特率发生器功能模块图

3.3 接收模块

接收模块由消息帧信号检测模块、串并转换模块和数据缓存模块组成。

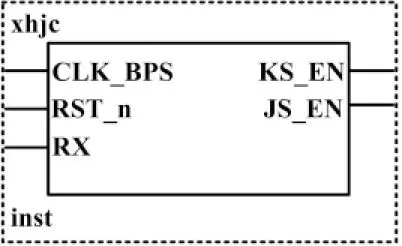

① 信号检测模块。信号检测模块的功能是检测消息帧的开始与结束。当模块检测到串口至少有3.5个字符时间的停顿间隔,则置位起始信号标志位,如果没有就接着检测;当数据信息全部接收完毕,模块又检测到至少3.5个字符时间的停顿间隔,则置位终止信号标志位,表示消息帧已经结束。信号检测模块的功能图如图4所示。其中,RX是串口输入数据,CLK_BPS是数据传输时钟,RST_n是复位信号,KS_EN和JS_EN分别代表起始信号和终止信号。

图4 信号监测功能模块图

② 串并转换模块。串并转换模块的功能是接收数据的串行比特流,将输入数据转换为8位并行数据,并将并行数据发送给数据缓存模块和CRC校验模块[9]。该模块的功能图如图5所示。CLK_BPS是波特率时钟信号;RX是串行输入数据;当KS_EN为1时,模块开始工作;RX_D是8位并行输出数据;WR_EN是写数据寄存器使能信号;当JS_EN为1时,该模块停止工作,表示数据转换完毕。

图5 串并转换功能模块图

当KS_EN为1时,该模块开始工作,并检测起始位0,当串行输入“00101100101”(首先接收最低位)时,输出端输出的8位并行数据为“10011010”,因此该模块正确地完成了串并转换功能。

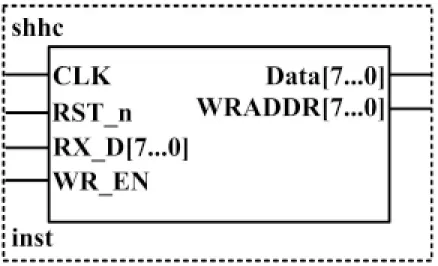

③ 数据缓存模块。数据缓存模块是将接收端收到的数据进行缓存,并认为缓存的第一个字节为从机地址,第二个字节为功能码,而第三个字节及后续字节(不包括CRC校验码)为消息帧的数据信息。数据缓存模块的功能图如图6所示,RX_D为缓存的8位并行数据,WR_EN为1时该模块开始工作,WRADDR为写入数据的地址,Data为写入存储区的数据。

图6 数据缓存功能模块图

3.4 发送模块

发送模块相当于接收模块的逆过程,该模块由发送控制模块、并串转换模块和读数据模块组成。发送控制模块与接收模块中的信号检测模块相似,它产生至少3.5个字符时间的停顿间隔;并串转换是将读取的8位并行数据转换为串行数据,并将串行数据发送给串口,由TX引脚发送出去;读数据模块是根据处理器的指令读取数据缓存区的8位并行数据,每取完一个字节后,数据长度寄存器加1。当数据长度寄存器的值与数据长度字节的值相等时,就取出CRC模块所产生的16位CRC值。当CRC校验值发送完毕,则表示整个消息帧发送完毕。由于发送模块各子模块与上述接收模块相似,这里就不详细列出了。

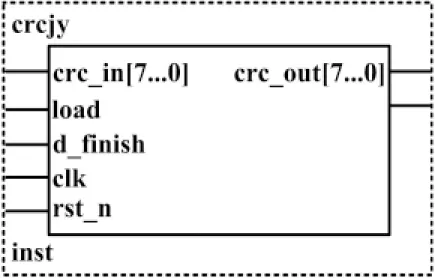

3.5 CRC16校验

CRC校验模块主要完成两个任务,一个是对主机发送给从机的消息帧进行CRC计算,并将校验结果发给发送模块;另一个是对从机返回给主机的消息帧进行CRC校验。CRC校验码是两个字节、16位的二进制数。CRC校验开始时,将一个16位的CRC寄存器各位置1;然后将消息帧中的第一个8位字节与CRC寄存器的低字节进行异或运算(只有每个字符中的8位数据进行CRC计算,而起始位、停止位及校验位不进行CRC计算);接着向最低有效位(LSB)方向移位,并用0填充最高有效位(MSB);检查LSB的值,如果LSB=1,则与寄存器的预置值进行异或运算,如果LSB=0,则不作异或运算。重复以上处理过程,直到移位8次,当第8次移位后,将下一个8位数据与寄存器的当前值进行异或运算,并重复上面的步骤[10]。当整个消息帧的数据都处理完后,CRC寄存器的值就是该消息帧的CRC校验值。

CRC校验的模块图如图7所示。其中,crc_in[7:0]是输入数据,load表示开始编码,d_finish表示编码结束,crc_out[15:0]是最后得到的CRC值。

图7 CRC校验模块图

FPGA收到从机发来的消息帧“01,03,00,9a,00,07,e0,ef”,其中efe0为该消息帧的CRC校验码,因为发生时是先发低字节再发高字节,因此ef是高8位,CRC模块对该帧的计算结果为efe0,两者相等,因此满足CRC校验的要求。

4 结束语

为了实现水站监控系统中对各检测仪表的数据采集,采用Modbus协议规范进行通信设计。采用Verilog HDL语言对Modbus RTU协议各个模块进行编程和功能仿真,并提供了有关模块的仿真结果。实践证明,采用FPGA来设计Modbus协议与传统的单片机设计相比,其传输速度更快、可扩展性更强,并具有一定的可行性。

[1] 肖长来,梁秀娟.水环境监测与评价[M].北京:清华大学出版社,2008.

[2] 桂婧.基于FPGA的超声波探伤仪信号处理系统分析与设计[D].广州:华南理工大学,2010.

[3] 张明龙,陈锋,许涛涛.嵌入式水质监测系统节点间MODBUS的协议设计[J].仪表技术,2013(10):1-4.

[4] 王振明.SCADA(监控与数据采集)软件系统设计与开发[M].北京:机械工业出版社,2008.

[5] 潘悦.Modbus协议研究及其实验系统的设计[D].哈尔滨:哈尔滨工业大学,2007.

[6] 陆晶,薛伟.基于MODBUS协议的温度采集系统的设计[J].电子测量技术,2009,32(12):25-27.

[7] 张飞,张云,韩彦岭,等.基于Modbus远程监控的水质在线监测系统的设计与实现[J].电子设计工程,2014(2):1-4.

[8] 王伶俐,周学功,王颖.系统级FPGA设计与应用[M].北京:清华大学出版社,2012.

[9] 杨大柱.基于FPGA的UART电路设计与仿真[J].微计算机信息,2007,23(5):200,212-213.

[10] 张增波,陈仲林,肖刘.基于FPGA的内置并行CRC校验的UART[J].自动化与仪表,2013,28(2):30-32,40.

Design of the Modbus Communication Protocol for Water Station Monitoring System

In order to solve the problems of poor extensibility and high cost in water station monitoring systems, the FPGA technology is applied in the system. The overall structural design of water station monitoring system is achieved, in the system, the communication between controller and analytical instrument is using Modbus protocol. Through analyzing this protocol in detail, by adopting FPGA modular design method, the protocol is divided into baud rate generator module, receiving module, sending module and CRC checking module; the design and functional simulation of each module are conducted with Verilog HDL language. The results of experimental simulation indicate that the design satisfies the communication requirements of Modbus protocol, and possesses certain practical value in industrial communication field.

FPGA Modbus Communication protocol Water station monitoring Verilog HDL

国家863计划基金资助项目(编号:2013AA040302);

陈佳晖(1990-),男,现为南昌大学测试计量技术及仪器专业在读硕士研究生;主要从事嵌入式系统开发及信号监测技术的研究。

TP336

A

10.16086/j.cnki.issn1000-0380.201509013

江西省科技厅科技成果重点推广指导项目(编号:2011ZBBI90006)。

修改稿收到日期:2015-04-03。