增强芯片可靠性的方法研究

张聪 陈守迎 汤德勇

【摘要】 研究了肖特基芯片势垒结构与参数性能的原理,结果表明利用扩散势垒和多层金属化结构设计工艺,使得肖特基势垒界面横向结构十分稳定,器件高温反向特性、低温正向特性得到提高,反向耐压与抗浪涌冲击能力大大增强。多层金属化结构利用几种金属各自的优点相互取长补短,提高了器件的抗热疲劳性能。在电极金属和硅化物层之间形成的扩散势垒可以有效阻止肖特基势垒高度ФB值及理想因子n值发生变化。

【关键词】 扩散势垒 多层金属化 反向耐压 高温性能 可靠性

目前国内肖特基1A-3A产品由于芯片稳定性问题,多用于民品封装。经过实验验证过去民品生产的肖特基芯片无法满足军工对高可靠性的要求,应用于军工及航空航天工程的1A-3A玻封肖特基芯片尚属空白,急需填补,因此需要重新设计满足高可靠性要求的芯片。

一、肖特基基本原理和主要性能

肖特基工作的基本原理是在金属(例如铅)和半导体(N型硅片)的接触面上,用已形成的肖特基来阻挡反向电压。

肖特基器件具有开关特性好、反向恢复时间短等特点,主要应用于开关电源、PWM脉宽调制器、变频器等电子电路中,作为高频整流二极管、续流二极管或阻尼二极管使用。由它制作的电子线路可广泛应用于计算机、雷达、通讯发射机、航天飞行器、仪器仪表等方面。

金属与半导体接触时,费米能级的匹配要求,导致了金属与半导体之间电荷转移的势垒,通常叫作肖特基势垒,它是由于金属和半导体功函数不同而产生的[1]。

肖特基二极管的正向特性如下面(1)式所示,反向特性由(2)式表示,△ФB是由于电场效应和镜像力的作用而引起的势垒高度的降低。

IF =IS{exp[q〔VF-IFR〕/nkT]-1} (1)

IR =ISexp(q△ФB/kT) (2)

IS =SA*T2exp(-qФB/kT) (3)

△ФB=(qE/4πεS)1/2+αE (4)

E =[2qND(VR+VD) εS ]1/2 (5)

式中

IF— 正向电流 VF— 正向压降

IR— 反向电流 VR— 反向电压

S — 二极管面积 A* — 理查逊常数

q — 电子电荷 k — 玻尔兹曼常数

T — 绝对温度 n — 理想因子

εS — 半导体的介电常数 ND — 杂质浓度

VD — 扩散电位 ФB— 势垒高度

α — 经验参数

以上几个公式是设计的基本依据。由公式可知,器件的正反向参数与肖特基势垒高度ФB、理想因子n及外延层参数有很密切的关系。

二、工艺创新设计

2.1扩散势垒的创新设计

近年来,金属硅化物在肖特基二极管中得到了广泛的应用,但是上层电极与硅化物层的兼容问题仍是一个值得注意的重要问题。硅化物的用途不仅提供一个合适的肖特基势垒,而且还能防止电极金属和硅之间的反应,但是由于电极金属也和硅化物起反应,电极金属与硅化物的接触在一定1000526489144的温度下是不稳定的,它们容易形成金属化合物,在器件的电学特性上表现为肖特基势垒高度ФB值及理想因子n值发生变化。为了防止以上情况的发生,通常可以在电极金属和硅化物层之间形成一层扩散势垒。

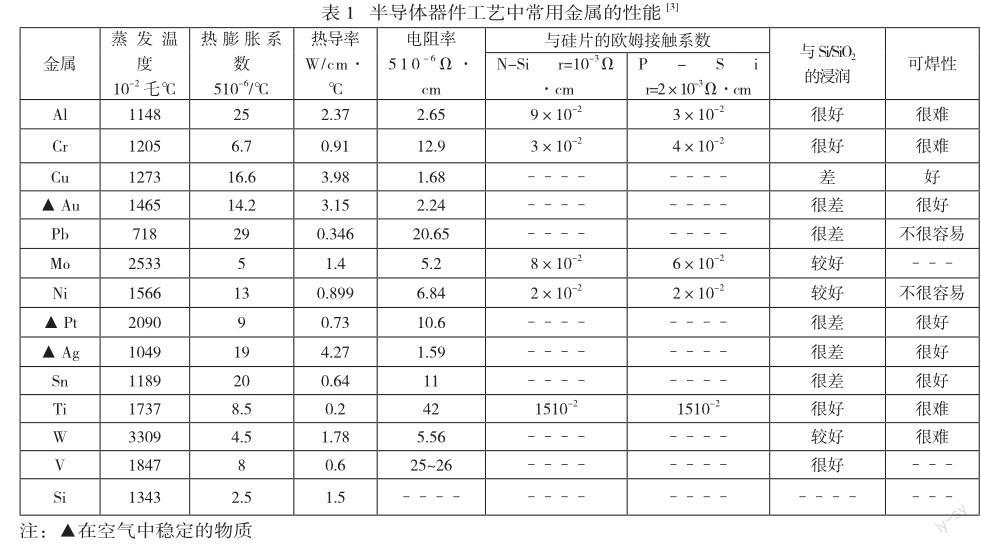

选择扩散势垒材料的最重要参数是再结晶温度Tc、电阻率及原子扩散系数。目前用作扩散势垒的材料有:Ta、W、Ti、Mo、Cr和V等难熔金属。硅化物也可用作扩散势垒。从原子扩散系数来说,单晶层是最有效的扩散势垒,但是目前还未能制备出来。非晶金属合金是较好的扩散势垒材料(TC超过700℃是可能的),非晶与多晶相比较,其扩散系数低一个数量级,因为多晶中有一个沿晶粒边界扩散的问题。非晶金属合金的缺点是电阻率较大(典型值为100μΩ·cm ),而难熔金属作为扩散势垒时其电阻率要低得多。

根据以上所述及我们的设备条件,决定采用难熔金属Ti作为本器件的扩散势垒。我们的实验结果表明:当温度在420℃以下,将器件的芯片退火20分钟,其势垒的电特性较稳定,势垒高度φB值和理想因子n值基本不变,在此温度以上退火,势垒开始失效。我们也同样做了在没有Ti层作为扩散势垒时的实验,将芯片在380℃以下退火20分钟,肖特基势垒的电特性较稳定,在此温度以上退火,势垒开始失效。这就说明Ti作为肖特基二极管的扩散势垒,对阻挡电极金属与势垒金属之间的扩散反应,效果是显著的。

2.2多层金属化结构的设计

在一般器件的制造中,如电流密度较小、结温较低的器件,铝是单独作为电极使用的好材料,但是对电流密度大、结温高以及可靠性、稳定性要求较高的器件,用单一的金属层作为电极不太合适,通常采用性能更好的多层金属化系统。多层金属结构是利用几种金属各自的优点相互取长补短[2]。

本器件为芯片面积较大的功率器件,要求电流密度较大,结温较高,除了芯片正面采用多层金属结构外,背面也采用多层金属层。下面讨论本器件多层金属化系统的设计。

多层金属之间的接触应该是稳定的、紧密的和粘附良好的,在硅化物的形成及多层金属的淀积过程中,形成氧化物是一个相当普遍的现象,因此,在多层金属化的工艺流程中,应严格操作规程,并注意层与层之间的清洁,避免氧化现象,同时也应包括清除氧化物的工艺步骤。

粘附层直接与Si/SiO2接触,要求与Si/SiO2粘附良好,性能稳定,它本身不与上下两层金属形成高阻化合物,还要求能阻挡导电层、过渡层与势垒金属形成高阻化合物,并阻止导电层、过渡层与Si形成化合物。

过渡层要求这层金属与上下两层金属都不产生高阻化合物,而且接触电阻小、针孔少,常用金属有Pt、Pd、W、Mo、Ni以及NiCr。本器件选用Ni为过渡层。下面将要提到导电层的常用金属为Au、Ag等。但是不能将Au、Ag 膜直接与粘附层Cr 、Ti 、V等接触,因为Au、Ag 膜很易熔于Pb、Sn等焊料,造成焊料直接与Cr 、Ti 、V等金属膜接触,而这些金属都是难焊金属,影响了器件上下电极的焊接性能,所以在Au、Ag导电层与Cr、Ti、V粘附层之间需要设置过渡层。

导电层是多层金属结构的最外层,要求电阻率低,抗电迁移能力强,性能稳定,不易氧化,易与过渡层粘接且导热性能良好,通常采用Au或Ag。由于Au价格昂贵,Ag还能改善焊料的流散性,因此,本器件选用Ag为导电层。此层厚度较厚,一般要求在0.9~1.8μm,以利于上下电极的焊接,并能充分保护过渡层不被氧化。

三、试验结果

用这两种工艺改良后的芯片制作的玻封产品能夠满足GJB33A-1997《半导体分立器件总规范》中的相关要求。最大结温TjM=150℃,存储温度Tstg在-55~150℃之间,稳定的通过了热冲击、引出端强度、耐湿、扫频震动、恒定加速度和盐雾试验。

用此工艺制作的系列芯片制作成的功率玻封肖特基器件获得国家科学技术部名为“高可靠功率玻封肖特基器件封装技术研究”的科技成果。

四、致谢

感谢济南市半导体元件实验所芯片生产线的同事们对本次试验所提供的帮助。

参 考 文 献

[1]杨碧梧.肖特基二极管保护环结构的研究[J].山东电子,1997,1,:39-40.

[2]陈明华,成巨华.肖特基二极管结构解剖与分析[J]微电子技术,1999,27(4):35-37.

[3]<德>H.-G.翁格,W.哈特,《高频半导体电子学》.