edBoard开发板在片上系统(SoC)设计课程中的应用

肖昊 张华娟

【摘要】 Zedboard是基于Xilinx ZYNQ系列全可编程SoC系统的FPGA开发板。它以ARM Cortex-A9处理器为核心,集成了一块可编程FPGA、存储器控制器和外设。配合Xilinx的开发软件,ZYNQ FPGA提供了一个方便、便捷的SoC开发平台,使用者可以快速的建立一个初始的SoC系统,并在此基础上进一步扩张相应的功能。这为高校SoC实验课程提供了很好的平台。本文将基于Zedboard开发板,以培养学生对基本SoC的组成结构、设计流程、设计方法的深入理解为目标,探索一种内容合适,易于理解的SoC设计实验教学方法。

【关键词】 Zedboard Xilinx ZYNQ SoC FPGA

一、SoC的研究背景

集成电路是当今信息技术产业高速发展的基础和源动力,已经高度渗透与融合到国民经济和社会发展的每个领域,其技术水平和发展规模已成为衡量一个国家产业竞争力和综合国力的重要标志之一。经过多年的快速发展,我国信息技术产业规模多年位居世界第一。国家出台了一系列政策鼓励和发展集成电路产业,其中加强集成电路专业人才的培养,是重要的举措之一。高校是我国集成电路人才培养的重要基地。目前,国内不少高校都开设了集成电路相关的课程。其中,片上系统(System-on-Chip, SoC)是集成电路的主流发展方向,相关的课程是集成电路设计类的主要课程之一,主要传授数字片上系统(SoC)及混合信号SoC的基本设计方法和技术,为从事集成电路设计和研发提供必要的基础知识。目前,国内高校的SoC设计课程主要以概念性理论教学为主,这与集成电路设计实践性强的特点极不相符合。导致众多学生难以真正理解SoC的理论和设计方法,更不具备参与SoC设计的能力,使教学与就业、科研需求严重脱节。但由于SoC设计的特点 :一是硬件规模庞大,通常基于IP设计模式;二是软件比重大,需要进行软硬件协同设计。因此,开设SoC的实验类课程对高校的硬件条件和任课教师的科研基础都提出了很大的挑战。得益于FPGA技术的发展,目前已有的集成电路设计环节主要集中于在计算机上进行集成电路的版图设计。因此,这为高校进行集成电路设计的培训提供了便利,同样给SoC教学课程提供了机遇。本文基于Xilinx Zynq-7000全可编程SoC系列器件,以提高学生实践能力为目标,探索一种内容合适,难度适中的SoC设计实验教学方法。

二、SoC的结构与设计方法

2.1 Zynq-7000 SoC芯片简介

Zynq-7000 SoC芯片的硬件部分实现了一个高性能、双核 ARM Cortex-A9 处理器子系统(PS)和一个丰富的内存、配置和互联接口。在 FPGA 逻辑部分保留了灵活性以及其他传统 FPGA 具备的所有优势,FPGA 则通过多口高性能接口连接到 PS 端,实现 PS 与 FPGA 间的高带宽通信。ZedBoard 通过提供一个专门为这类独一无二并且功能强大的器件推广到广大应用和用户的定制平台将定制SOC 的 概念带到了下一步。作为全球最大的可编程逻辑平台供应商,Xilinx 已经将可编程逻辑技术带领到了全可编程的时代,Xilinx 推出的 Zynq-7000 All Programmable SOC 集成了 ARM Cortex-A9 双核(PS)以及最多可达相当于 500 多万个逻辑门的可编程逻辑单元(PL),不仅解决了芯片工艺实现上的难点,更解决了片内高性能处理器与高性能可编程逻辑数据交互协议的难点。

2.2 SoC的结构

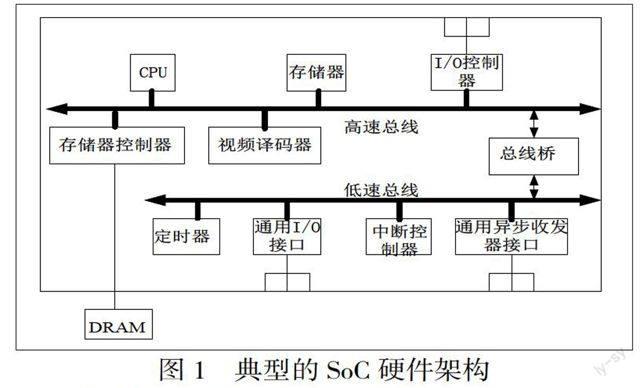

图1 典型的SoC硬件架构

图1所示为一个典型的SoC硬件结构。片上模块包括以下几种。(1) CPU:如ARM、MIPS等。(2)存储器:如SRAM、Flash、ROM、DRAM等。(3)存储器控制器:控制外部存储器。(4)片上互连:总线,提供各IP间的数据通路。(5)专用加速器:如MPEG、AES等ASIC技术设计的可重用专用模块。(6)I/O控制器:如PCI、PCI-X、以太网、USB、AD/DA等。(7)外围设备:如通用I/O接口、通用异步收发器、定时器、中断控制器等。

2.3 SoC的设计

SoC设计是自顶向下和自底向上相结合的过程,主要流程如图2所示。(1)系统级设计主要有系统说明、行为建模和软/硬件划分。(2)硬件设计包括RTL设计、综合,布局布线、功能验证和流片制造。(3)软件设计主要是对软件的开发。从上文可知,SoC设计主要有以下特点:(1)采用深亚微米、超深亚微米CMOS工艺技术。(2)SoC是针对不同应用市场开发的产品。(3)软/硬件协同设计。(4)低功耗技术要求。因此,目前高校教学中只进行书面介绍或图片展示很难让学生充分理解SoC设计的内涵。所以,基于Xilinx Zynq-7000全可编程SoC系列器件设计一个难度适当的SoC设计实验势在必行。

图2 SoC设计流程

三、SoC设计课程实验介绍

本文将先介绍HDMI的传输原理,然后介绍基于Zedboard的HDMI现实系统架构,最后介绍SoC的实验步骤。

3.1 HDMI传输原理介绍

信源(Source)和信宿(Sink)组成HDMI系统的架构。HDMI接口包括3个TMDS数据信道、1个TMDS时钟信道和一个DDC通道。信源读取信宿的E-EDID,是为了解信宿的当前配置和能力。HDMI传输的数据包括视频数据、控制数據和数据包(数据包中包含音频数据和附加信息数据,例如纠错码等)。TMDS每个信道的传输数据包括2位的控制数据、8位的视频数据或4位的数据包。这些数据先传给HDMI发送器,然后经10位编码器编码,最后串行输出。串行输出的10位编码经HDMI接收器串行接收,再进行解码得到原数据。在时钟信道的一个时钟周期内完成所有操作。每个时钟信道的一个时钟周期对应一个像素点数据的传输,这个时钟频率一般在25MHz~165MHz之间。

3.2 HDMI顯示系统架构

图3所示为基于Zedboard的HDMI显示系统SoC系统。VDMA 和 ADV7511 视频接口组成系统的视频输出接口。VDMA 的功能是将图像帧数据传输到视频接口模块。DMA 和 spdif 音频接口组成系统的音频输出接口。Zynq 作为整个系统的控制核心,提供 HDMI 的显示数据,来及时读写显存的控制,以及 DDC 的数据产生。PL 部分主要是 ADV7511 的控制,还有将 24bit 的RGB 数据转换为16bit 的 YCBCR422 的数据发送给 ADV7511。ZedBoard 的 HDMI 接口使用了 ADV7511 芯片,这是 ADI 公司生产的一款 225MHz 的 HDMI 发送器,它全面支持 HDMI1.4 协议、同时包括 HDMI 以太网络通道 HEAC 和 3D Video,它支持全部的高清制式。

图3 Zynq 系统框图

3.3 HDMI显示系统实验步骤

实验基于Xilinx Vivado集成开发环境,软硬件协同,分为硬件设置和软件设置,步骤分别如下:(1)创建工程,添加工程文件、目录和库目录,设置软件环境和FPGA器件;(2)添加设计中使用的IP。(3)初步综合,以明确网标中时钟信号的名字,检查是否存在语法错误。(4)添加约束,时钟约束,管脚约束等。(5)综合实现(Synthesis and Implementation),生成二进制比特流。以上硬件步骤可以Tcl脚本的形式实现,实验中学生只需要载入脚本。Xilinx的软件开发是基于Vivado的SDK开发环境,步骤分别如下:(1)新建软件工程;(2)添加C代码源文件至工程目录;(3)设置软件环境变量,添加库目录等;(4)编译软件,生成可执行文件。

完成以上软硬件设计后,将Zedboard开发板与电脑主机相连,并将HDMI接口与显示器相连,打开FPGA开关,下载FPGA比特流和可执行文件即可在显示器上显示出图像。

四、 总结

本文基于Xilinx Zedboard开发板的HDMI功能,设计了一个SoC设计的课程实验。经教学实践证明,Xilinx Zedboard开发板提供了一个完整的SoC开发设计平台,其开发软件Vivado提供了简单易用的图形开发界面,整套流程简单易学,便于学生掌握和理解,为高校的SoC实验教学提供了很好的软硬件环境。

联系方式:肖昊 南京市御道街29号A12号楼 210016 xiaohao@nuaa.edu.cn

参 考 文 献

[1] James Lucero and Bob Slous. Designing High-Performance Video Systems with the Zynq-7000 All Programmable SoC Using IP Integrator[technical report]. www.xilinx.com. March 28, 2014.

[2] Zynq-7000 All Programmable SoC Overview[technical report]. www.xilinx.com. October 8, 2014.

[3] ADV7511 PROGRAMMING GUIDE[technical report]. www.xilinx.com.March 2012.

[4] LogiCORE IP AXI Video Direct Memory Access v6.2[technical report]. www.xilinx.com. PG020 April 2, 2014.