高速并行处理模式下同步时序研究

(海装装备采购中心, 北京 100097)

引言

在高速实时处理系统中,对数据吞吐量,CPU处理能力等要求越来越高,因此经常会使用到各种各样的高速时钟电路,如SDRAM接口,DDR接口,高速的CPU数据接口以及芯片之间的并行互连接口等。这些高速的数据接口基本工作在100 MHz频率以上,每个时钟周期小于10 ns(10-9s)。在这么高的速度下,数据线上每一个时钟周期内要求数据被正确地读出和写入,保证这一过程需要对数据传输时序的理解和精确的计算。如果发生时序错误,会导致不可预测的灾难性后果[1]。因此,为使数据正确地进行传输,数据输出芯片必须满足数据输入芯片对数据建立时间和数据保持时间的要求。

1 计算裕量涉及的概念及计算方法

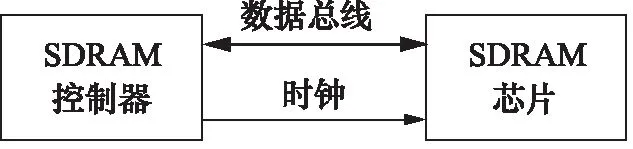

SDRAM是典型的高速并行总线结构。图1所示为SDRAM的源同步工作方式,在这种方式下,由SDRAM控制器产生时钟,并将这个时钟经过PCB上的走线分配给各个SDRAM芯片。因此也可称作SDRAM控制器分配时钟工作方式。通过对SDRAM在这种方式下的时序分析,我们可以理解相关的一些时序参数的具体含义。比如Tco、建立时间、保持时间、建立时间裕量、保持时间裕量、传输时延、时钟抖动、时钟偏移等。

图1 SDRAM控制器源同步工作方式

Tco是指时钟触发开始到输出有效数据的器件内部所有延时的总和。总线时序如图2所示,由图2可以看出,当SDRAM控制器输出数据时,在时钟上升沿之后发出数据,上升沿到数据在数据总线上有效的时间称为时钟到数据的延时,即Tco。SDRAM在下一个时钟的上升沿去锁存数据总线上的数据。假设此数据需要的最大值为Tcomax及最小值为Tcomin。

图2 总线时序图

信号经过数据线到达接收端后,就牵涉到建立时间和保持时间这两个时序参数,他们是接收器件本身的特性[2]。所谓建立时间(Tsu)就是指芯片作为输入时,数据所需的建立时间(时钟上升沿前数据维持的时间),建立时间的满足永远以最小值来计算。而保持时间(Th)指的是芯片作为输入时,数据所需的保持时间(时钟上升沿后维持的时间),保持时间的满足也永远以最小值来计算。一般来说,时钟信号来的时候,要求数据必须已经存在一段时间,这就是器件需要的建立时间。时钟边沿触发之后,数据还必须要继续保持一段时间,以便能稳定的读取,这就是器件需要的保持时间[3]。如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。

因此,通过以上分析可知,SDRAM控制器的输出必须满足SDRAM的输入条件。

从输入的Tsu考虑:Tsu=Tclk-Tcomax;为了满足Tsu的条件,Tsu必须:Tclk-Tcomax>Tsu=>Tclk>Tsu+Tcomax

从上面式子,我们还可以推算出,在给定的时钟频率下,输入的建立时间的时序裕量:

Setup Time Margin=Tclk-Tsu-Tcomax

(1)

从输入的Th考虑:Tcomin>Th;从上面的式子我们可以推算出输入保持时间的时序裕量:

Hold Time Margin=Tcomin-Th

(2)

在实际应用中,由于系统时钟频率很高,在计算时序裕量时还要考虑数据和时钟在PCB上的传输延时以及信号完整性对时序的影响。下面介绍另外一些时序参数:

Tflight: 这个参数定义数据信号在PCB传输线上到达输入点所需的时间,就是平时所说的传输时延或飞行时间。

Tskew: 这个参数定义时钟信号到达发送IC和接收IC时钟引脚的时间差异。在源同步工作方式下,即为时钟从SDRAM控制器到SDRAM的延时。

Tcrosstalk:由于串扰引起的数据沿变化,导致数据到达时间发生轻微的摇摆。

Tjitter:由于时钟抖动引起的时钟周期的变化。

考虑这些因素后,建立时间和保持时间的裕量就会相应的发生变化,如下公式所示:

Setup Margin=Tclk-Tcomax-Tsu-

Tflight+Tskew-Tjitter-Tcrosstalk

(3)

Hold Margin=Tcomin-Th+Tflight-Tskew-Tcrosstalk

(4)

由于输入的建立时间裕量和保持时间裕量必须大于零,所以:

Tclk-Tcomax-Tsu-Tflight+Tskew-Tjitter-Tcrosstalk>0

Tcomin-Th+Tflight-Tskew-Tcrosstalk>0

从上面的式子,就可以得出数据总线所能走的最大距离和最小距离的定量公式:

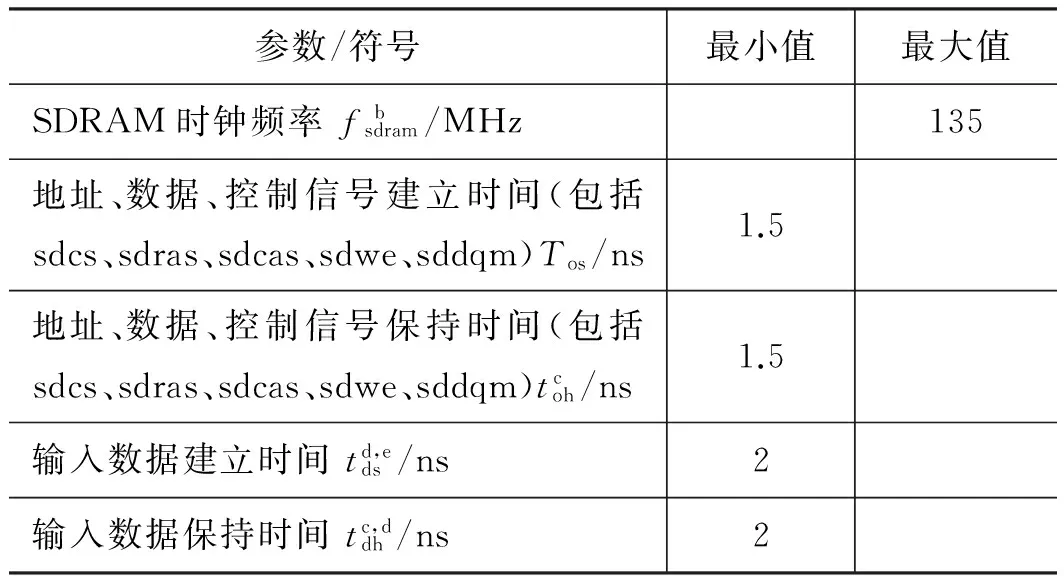

Tflight (5) Tflight>Th-Tcomin+Tskew+Tcrosstalk (6) 这两个公式考虑了Tskew,Tjitter,Tcrosstalk对时序裕量的影响,为PCB的布线计算提供了理论依据[4]。但这些信号在很多情况下设计者无法预测是带来正的影响还是负的影响,因此要遵循以下的原则来使时序计算达到最严格的指标。 (1) 在计算公式(5)中,也就是计算最长布线时,这些指标所取的正负号应该使布线长度值达到最小; (2) 在计算公式(6)中,也就是计算最短布线时,这些指标所取的正负号应该使布线长度值达到最大。 下面以实际使用中出现问题的SDRAM总线为例说明总线时序裕量计算方法及原则。和上面介绍的基本原理稍有不同,SDRAM总线是双向总线,还应该考虑读SDRAM数据的情况,即读数据的时序要满足SDRAM控制器的输入要求,才能确定时序裕量[5]。 图3、 图4是SDRAM控制器读写数据时的时序图,表1、表2分别是SDRAM,SDRAM控制器的时序指标,我们以这些时序指标为依据进行SDRAM在源同步工作方式下时序裕量计算。 图3 SDRAM控制器写时序图 图4 SDRAM控制器读时序图 表1 SDRAM控制器时序指标 表2 SDRAM时序指标 在这种情况下,SDRAM控制器出来的时钟,经过PCB后到达SDRAM芯片所需的时间为Tdelay。可知这个Tdelay肯定是正的,并且在PCB上走了约2.8 inch,则: Tdelay=2.8×0.18 ns≈0.5 ns 其中,单位inch的时延由PCB材质所决定,在本例中为0.18 ns/inch。 SDRAM控制器输出数据的同时也输出时钟,此时: Tskew=Tdelay=0.5 ns 根据表1时序指标得出其他参数: Tclk=7.52 ns,Tcomin=Toh=1.5 ns, Tcomax=Tclk-Tos=6.02 ns,Tos=1.5 ns, Tjitter=±0.1 ns,Tcrosstalk=±0.1 ns, Tsu=1.5 ns,Th=0.8 ns 故根据式(5)、式(6): Tflight =Tclk-Tcomax-Tsu+Tdelay-Tjitter-Tcrosstalk =Tos-Tsu+Tdelay-Tjitter-Tcrosstalk =0.3 ns Tflight>Th-Tcomin+Tskew+Tcrosstalk =Th-Tcomin+Tdelay+Tcrosstalk =0 ns 飞行时间肯定是大于零的,因此没有最小时延限制。 综合上两式得出:Tflight<0.3 ns,Data Trace Length<1.67 inch,明显这对于PCB板布线是很苛刻的要求。 当SDRAM输出数据,而SDRAM控制器作为输入时,由于始终依然是从SDRAM控制器输出到达SDRAM,然后SDRAM根据这个时钟送出数据,所以时钟到SDRAM比时钟到SDRAM控制器落后了Tdelay,因此: Tskew=-Tdelay=-0.5 ns 根据表2时序指标得出其他参数: Tclk=7.52 ns,Tcomin=2.7 ns,Tcomax=5.4 ns, Tjitter=±0.1 ns,Tcrosstalk=±0.1 ns, Tsu=2 ns,Th=2 ns 故同样根据式(5)、式(6): Tflight =Tclk-Tcomax-Tsu-Tdelay-Tjitter-Tcrosstalk =-0.58 ns Tflight>Th-Tcomin+Tskew+Tcrosstalk =Th-Tcomin-Tdelay+Tcrosstalk =-1.1 ns 综合约束条件可以看出,PCB板布线已经无法满足要求。因为飞行时间不可能小于零。 通过对以上读写时序的计算分析,以这种时钟方案工作的SDRAM控制器芯片,其速度很难达到133 MHz,一般只能宣称工作在100 MHz或更低。如果工作在100 MHz,则Tclk变为10 ns。相应给输入建立时间,增加了近2.5 ns的裕量,也就是增加了近13.8 inch的布线余量。 通过以上计算对于原理和案例的分析,可以得到以下的结论:保持时间裕量是和时钟频率无关的[6]。在源同步方式下的写操作,时钟是滞后到达SDRAM,因此延长了建立时间裕量。而从SDRAM读操作的时序裕量会更小,因为读操作时,时钟到SDRAM控制器比到SDRAM更超前,因此缩短了SDRAM控制器的建立时间[7]。这样PCB布线就受到了时钟线绝对长度(时延)的限制。只要时钟线的绝对长度超过一定的数值,在某种频率下,布线就不可能实现。因为在读SDRAM时,Tdelay这个指标可以把所有建立时间消耗完,导致最大布线长度小于零,也就是不可能实现的布线方式。因此,在源同步方式下,最优化的布线方案的前提就是使时钟线的长度尽可能的短。 参考文献: [1]吕霆,祝亮.高速时钟电路的信号完整性设计[J].电子工艺技术,2004,25(1):39-41. [2]王晓东,杨功立,刘春红.高速时钟电路设计[J].应用科技,2003,30(12):5-6. [3]张艳丽,安琪,王砚方.基于PCB仿真的高速时钟电路设计研究[J].计算机仿真,2004,21(9):175-178. [4]Howard Johnson.High-Speed Digital Design[M].北京:电子工业出版社,2004. [5]谢力华,苏彦民.正弦波逆变电源的数字控制技术[J].电力电子技术,2001,35(6):51-55. [6]游志青,陈宏,胡育文.UPS逆变单元的币复控制器参数的仿真分析[J].电源技术应用,2002,5(4):10-13. [7]郭卫农,陈坚.电压型逆变单元输出波形控制技术[J].通信电源技术,2001,(3):5-9.2 源同步方式下的案例

2.1 SDRAM控制器及SDRAM的时序指标

2.2 从写路径考虑

2.3 从读路径考虑

3 结论