基于EMC静电放电的整改方案与设计

孙浩

摘 要:文章阐述了静电放电的原理和危害,以及原因分析和基本对策。通过具体的整改方案和典型电路,掌握了静电放电抗扰度的整改和设计。

关键词:静电放电;ESD整改方案及实例;防静电设计

1 静电放电原理及其危害

静电放电是一种自然现象,当两种不同介电强度的材料相互摩擦时,就会产生静电电荷,当其中一种材料上的静电荷积累到一定程度,在与另外一个物体接触时,就会通过这个物体到大地的阻抗而进行放电。静电放电对电子设备(产品)就是一种主要的干扰源。

静电放电对产品两种危害:(1)当人体接触到半导体的时候,通过静电放电,可以导致数层半导体材料击穿,导致损坏设备(产品)、瘫痪系统等,造成不可挽回的损失。(2)静电放电形成的骚扰电流和电磁波会被产品吸收,造成产品的误操作、误显示。

2 静电放电的危害分析及防护措施

2.1 静电放电对产品危害分析

静电放电对产品的非破坏性影响,是由于静电放电形成的骚扰电流或电磁波被PCB板上的线路和元器件吸收,从而转换成为对产品的电子系统造成传导干扰和辐射干扰。常见的现象有:死机、复位、数据丢失、显示异常(蓝屏、花屏、数码管乱显示)、产品失效等。

静电放电对产品的破坏性影响,是由于静电放电的热效应和强电磁效应造成的。静电放电的热效应是因为静电电流大、电压高、放电时间短,形成破坏性热击穿,导致电路损坏。静电放电的强电场效应是因为MOS器件的栅极氧化膜厚度为1*10-7m量级,100V的静电电压在栅极氧化膜上可以产生1*106kV/m的强场,而MOS管的氧化膜的击穿强度仅为0.8*106-1*106kV/m。因此静电电压容易导致MOS场效应管的栅极氧化膜被击穿,使MOS管器件失效。

2.2 常用静电放电的防护措施

2.2.1 静电放电经常容易出现问题的部位

静电放电容易产生的部位:接口连接处、面板按钮处和结构缝隙。

2.2.2 接口連接处的静电放电处理措施

(1)保证连接器的金属外壳和设备的金属外壳良好接触,使静电电流直接从设备外壳泄放到大地上。使用材料:导电胶布、弹簧等。(2)设计时尽量避免复位电路(线)、片选信号、控制信号等敏感线路靠近接口连接器。(3)还可以采用抗静电较强的接口芯片,或者采用TVS管对地进行静电抑制,或者在信号线上串接电阻。

2.2.3 面板按键的静电放电处理措施

(1)指示灯、按键等在面板上的开孔尽量小。(2)指示灯和按键的PCB板尽量远离面板。(3)在面板上增加一层高绝缘材料来隔离。(4)用TVS管或者电容对按键电路进行处理。(5)改变面板信号线的走线方式。(6)对信号线加磁环处理。

2.2.4 缝隙处的静电放电处理措施

(1)对在缝隙处可以看到PCB裸露的金属部分贴绝缘膜。(2)改变缝隙结构,设计成倒挂槽结构。(3)在缝隙中增加绝缘材料,使静电无法通过。(4)将缝隙用铜箔贴住,用尽量短的导线连接到大地。

3 案例分析

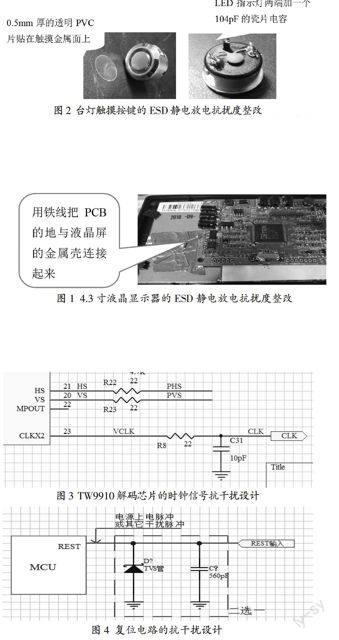

案例一:4.3寸液晶显示器的ESD整改现象:对4.3寸液晶显示器的液晶屏与面壳边框缝隙打8kV的空气静电放电,液晶屏显示画面异常:有时出现复位,有时图像发白。

原因分析:检查发现塑料面壳与4.3寸液晶屏的金属边框缝隙太大,施加8kV的空气静电放电,放电电流会流经液晶屏的金属壳,由于金属外壳是孤立的,没有接地,静电电流会继续对液晶屏内部电路和PCB放电。于是出现液晶屏画面异常。

整改方案:屏蔽和接地法。图1是4.3寸液晶屏PCB的安装示意图,用铁线将PCB的地网与4.3寸液晶屏的金属壳连起来,这样把静电放电的能量直接流入PCB的地。验证:再对4.3寸显示器的塑料面壳内边框与液晶屏的金属边框缝隙施加8kV的空气放电,液晶屏图像未出现异常,整改OK。

案例二:LED台灯触摸按键的ESD整改

现象:图2是调光LED台灯的金属触摸按键,由于金属触摸按键裸露在外壳的外面,优先选择4kV的接触放电。测试结果:静电放电过程中台灯灯光亮度明暗变化,LED指示灯坏,ESD测试Fail。

图2 台灯触摸按键的ESD静电放电抗扰度整改

原因分析:由于金属触摸按键开关是一个压电感应开关,如果直接打4kV静电接触放电,肯定影响或者损坏与触摸金属按键相连的元器件,同时LED指示灯离触摸按键金属部分太近,而且存在缝隙,LED灯珠会因静电放电而被击穿损坏。

整改方案:加绝缘片,介质隔离。用一个0.5mm厚的透明PVC片贴在触摸开关金属面上,经绝缘片隔离后,按标准选择8kV的空气静电放电测试。测试结果,台灯亮度无明暗变化,整改Ok,但LED指示灯仍然烧坏,估计是通过按键间的缝隙静电放电引起。在LED指示灯两端加一个104pF的瓷片电容。重复8kV的空气静电放电测试,LED 指示灯正常,整改Ok。

4 静电放电之抗干扰电路设计(电磁辐射引起的)

4.1 芯片的电源滤波电路设计

总线驱动、接收芯片的电源必须要有良好的滤波电路。如CPU、Flash、SDRAM等。尤其是MCU,必须采用储能电容和高频电容配合滤波。

4.2 时钟信号的抗干扰设计

时钟输出端通过接RC电路,延缓输出脉冲的上升沿,从而减少时钟的高频谐波分量在频带上的宽度和防止产生振铃现象。图3是TW9910解码芯片的时钟处理电路。R选取范围是20欧-100欧。

图3 TW9910解码芯片的时钟信号抗干扰设计

4.3 复位电路的抗干扰设计

对复位电路的脉冲干扰抑制,可以采用TVS管(双向瞬态抑制二极管,结电容要小,最好在1000pF以下);也可以用高频滤波电容,典型值是560pF,也可以用102代替,有时用103、104高频电容。对于手动的复位电路,还可以在电路中增加一个小阻值的限流电阻。复位电路设计见图4。

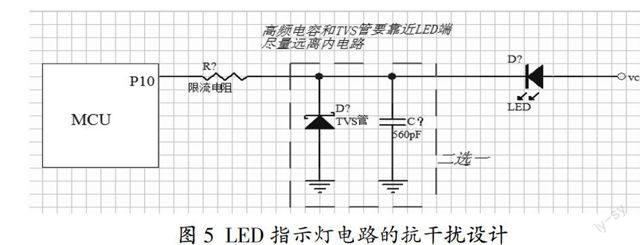

4.4 LED指示灯电路的抗干扰设计

对于LED指示灯的防静电设计,可以用高频滤波电容或者双向TVS管来搭建静电泄放回路。电容的值为101-104pF。电路设计见图5。

5 结束语

设计产品时,为了防止静电放电的发生,首先考虑要有足够的距离和绝缘强度。如果无法避免静电放电,再通过屏蔽和接地的方式,给静电电流提供一个阻抗足够小的泄放途径。其次,静电放电产生的电磁辐射会对PCB的铜皮走线和元器件产生电磁场干扰影响,所以PCB设计尽量防止大的电流环路,防止感应磁场;对于高阻抗布线,走线要尽量短,防止感应电场。对于PCB走线较长的电源线、信号线、复位线、时钟、片选、控制线、数据线等,在必要时,必须做抗干扰处理。

参考文献

[1]中华人民共和国国家质量监督检验检疫总局,中国国家标准化管理委员会[S].GB-T_17626.2-2006.电磁兼容-试验和测量技术-静电放电抗扰度试验,2006.

[2]钱振宇,等.开关电源的电磁性兼容设计、测试和典型案例[M].电子工业出版社,2011.