适用于802.11a的低噪声放大器设计

井 凯,庄奕琪,李振荣,吕育泽

(1.西安电子科技大学 微电子学院,陕西 西安710071;2重庆西南集成电路设计有限责任公司,重庆401332)

超外差接收机自Armstrong发明以来,以其高性能、高集成度、组合形式多样和易实现的特点被广泛应用于现代无线通讯设备.接收机一般可以分为镜像抑制型和零中频型.虽然零中频型接收机避免了镜像干扰,但是由于其较大的直流失调和1/f噪声,其性能不及镜频抑制型.镜频抑制型接收机射频前端主要由低噪声放大器(low noise amplifier,LNA)、镜像滤波器和混频器构成,其中镜像滤波器可以大幅抑制镜像信号.例如,泛欧的数字无线电话系 统 (digital enhanced cordless telecommunications,DECT)需要采用镜像抑制比达80~100 dB的滤波器以保证接收性能.目前有多种方法可以实现该滤波功能.例如声表面滤波器(surface acoustic wave,SAW)或陶瓷滤波器.但是由于该类滤波器均为片外实现,大大增加了集成难度,无法实现单片系统集成.相比之下,片内陷波滤波器则无此限制.虽然无源滤波器可以实现零功耗的优点[1-2],但是片上滤波器具有低品质因子,使得该结构性能并不理想,这主要是由片上电感的品质因子较低造成.虽然Kang等[3-4]提出利用晶体管负阻特性改善电感寄生以提高网络整体Q值的方法可以提高决滤波性能,但是仍未继续对功耗和尺寸进行进一步的分析和优化.

针对上述滤波器的优点与不足,本文提出一种新型低功耗有源陷波滤波器:基于滤波器品质因子和镜像频率可调的前提,对电感进行优化,维持谐振点不变的同时减小镜频输入阻抗,优化功耗,并设计出一款适用于802.11a协议的低噪声放大器.

1 陷波滤波LNA的分析与设计

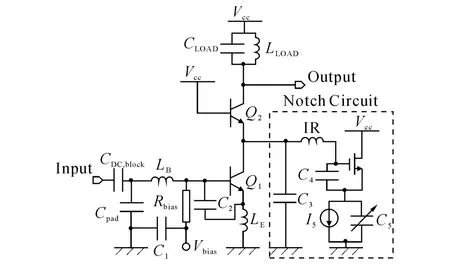

本文提出的镜像抑制型SiGe HBT LNA如图1所示,电路采用单级cascode结构以确保高增益、低噪声及输入输出高隔离度的优点[5].其中CDC,block为隔直电容,Cpad为pad的等效电容,Input与Output为电路的输入输出端口,电感LB、LE及电容C2、晶体管Q1构成源简并结构以实现噪声优化和阻抗匹配.电阻Rbias,电容C1和电压Vbias用于电路直流偏置,负载CLOAD和LLOAD组成LC谐振回路以实现高输出增益,同时削减镜像信号的输出幅值,节省电压裕度.陷波滤波器连接在Q1集电极以实现镜像频率下输入低阻抗和工作频率下高阻抗这一特性,抑制镜像频率.

图1 陷波滤波LNA完整电路图Fig.1 Complete schematic of image rejection LNA

1.1 LNA输入匹配设计

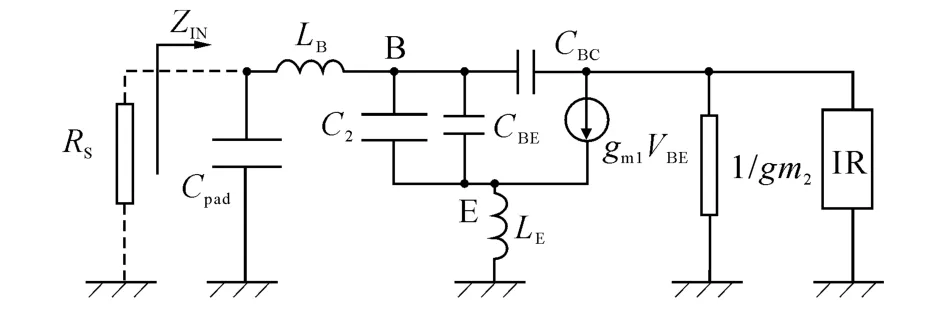

源简并LNA小信号输入匹配采用串联RLC结构[6],图2为输入小信号图,图2中省略CDC,block和偏置部分,RS为天线等效阻抗(50Ω),B和E分别为Q1的基极和发射极,CBE和CBC为晶体管电容,gm1VBE为跨导电流,1/gm2为从Q2发射极看入的等效阻抗,方框IR(image rejection)为上述陷波电路.若不考虑CBC馈通影响,电路的输入阻抗[7]可表示为

式中:Cpad为pad寄生电容,LB和LE分别为基极和发射极所加电感,C2为CBE所加的补偿电容.

图2 LNA输入匹配电路图Fig.2 LNA input match circuit

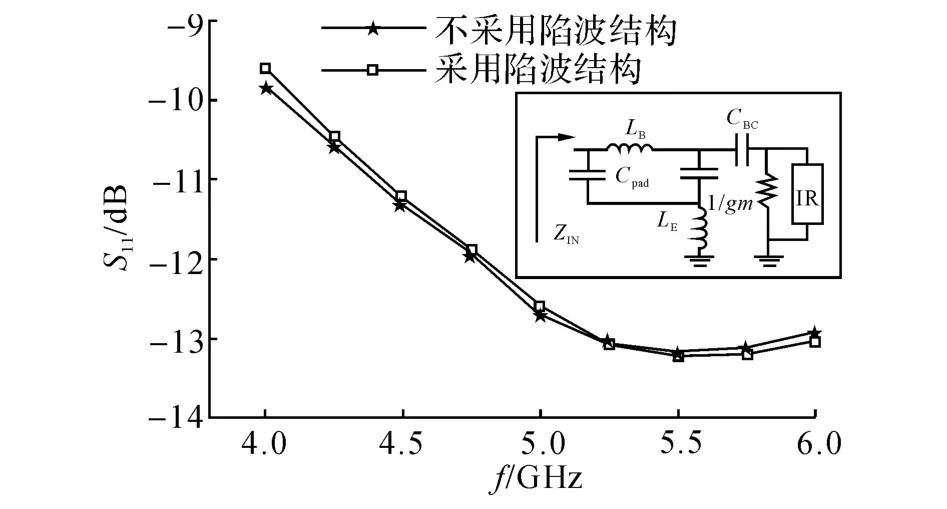

CBC使得1/gm与IR馈通至输入端,并且由于陷波滤波器含有电感使得输入阻抗表现出非单一的容性或感性,增大了匹配难度.为解决这一问题,可偏置Q2基极为电源电压,通过提高Q2发射极直流电压以增大Q1BC端反偏电压,减小CBC,增强IR与Q1基极隔离度,弱化后级对输入的影响[8].这样引起的问题是:Q2BC pn结易正偏.为避免这一情况电路采用LC并联负载,不仅可以提高谐振点功率增益,也可以避免额外的电压裕度,使得Q2BC结零偏以避免增益降低.图3为LNA在3.8~6.2 GHz下引入与不引入陷波滤波器的输入回波损耗S11结果,可见Q1的高隔离使陷波滤波器不会引入过大失配,与上述分析吻合.

1.2 有源陷波滤波器的尺寸优化

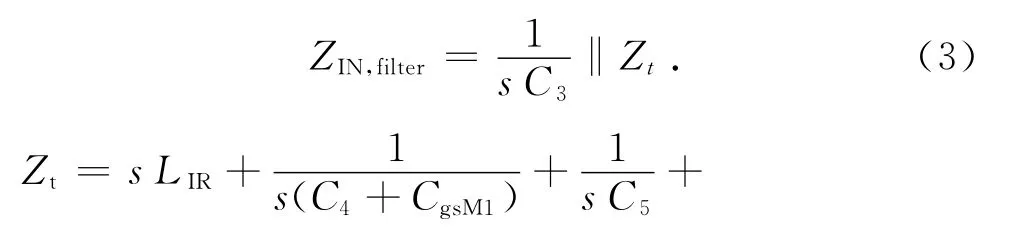

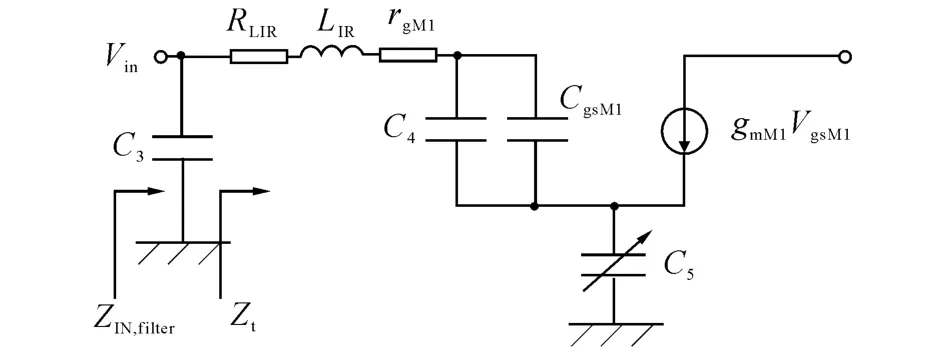

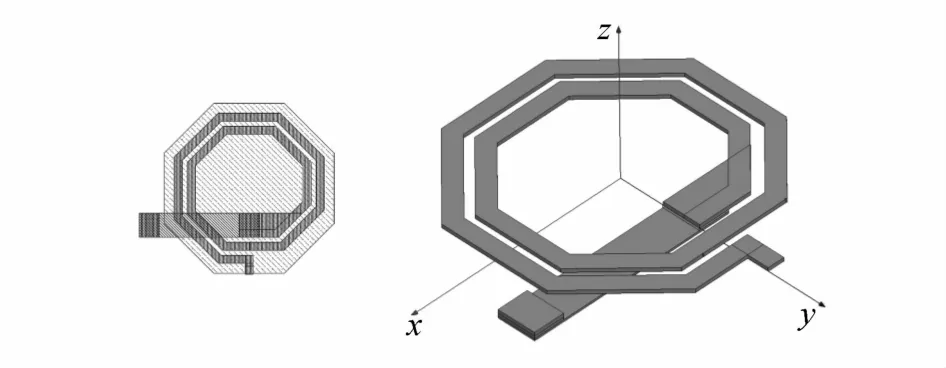

有源陷波滤波器小信号等效图如图4所示,其中RLIR为电感LIR的寄生电阻,rgM1为晶体管M1的栅极寄生电阻,C5为可变电容.由小信号分析滤波器的输入阻抗ZIN,filter为[9]

寄生电容Cpad略微影响输入匹配.另一支路由电感、电容和等效电阻ωTLE组成,ωT为Q1截止频率.令ωTLE为50Ω,并使电感与电容在工作点进行谐振,可得谐振频率为

图3 LNA输入回波损耗仿真结果Fig.3 Simulation results of input reflection loss in LNA

图4 陷波滤波器小信号电路图Fig.4 Small-signal circuit of notch filter

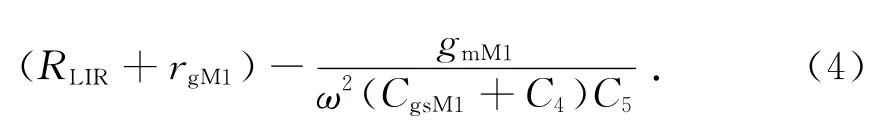

式(4)中电阻RLIR与rgM1是引起陷波网络低性能的原因.不难看出,减小这两项即可大大提高网络品质因子,而式(4)最后一项可以实现该功能:通过调节I5改变gmM1,进而改变负阻以抵消正项,提高网络Q值.由于该负项与频率ω有关,为得到某一频率下的最低阻值,需要通过调整可变电容C5来调节阻抗抵消频点.

虽然Kang等[3-4,8]也采用了有源滤波结构,但均未对尺寸进行优化.本文提出新型优化思路:对电感尺寸优化降低RLIR,进一步减小MOS跨导,降低功耗.首先采用Jenei公式[10]计算电感值LS:

式中:Lself为自感,M+与M—为正负互感,n为线圈圈数,w为线宽,s为线距,N i为常数,din为电感内径,l为线圈总长,t为金属厚度,μ0为真空磁导率.已知电感的品质因子与寄生电阻呈反比,因此,求解镜像频率下最小RLIR可转化为求解该频点下的最大Q值.采用克隆算法[11]实现这一过程:首先对电感模型参数附加约束条件,并设定工艺参数和镜像频率,然后将线宽、线间距、圈数和螺旋线圈内径作为优化变量,将max(Q)设为最终优化的目标函数,并结合L=C这一约束条件,求得

式中:λ为极大正数,在进行算法优化时,附加更多的约束条件可以使搜索空间减小,加快收敛速度.图5为优化后电感平面图与HFSS设计的3D结构图.电感的尺寸被优化到75μm×75μm,电阻阻值也得以优化.在镜像频率下,电感的阻值从3.47Ω优化到3.02Ω,品质因子从3.19提高到3.64.

图5 优化电感的平面图与三维图Fig.5 3D structure and plan view of optimized inductor

1.3 有源陷波滤波器的功率与设计优化

对滤波器功耗加以优化.相较文献[3]中的结构,本电路额外引入C4,电感优化使得式(4)中RLIR减小,虽然较小的gmM1即可实现式(4)的实部抵消,但是在镜像频率下负阻大于正值仍然会恶化网络品质因子,而引入C4则可以调整负阻,确保实部抵消.另外,若采用文献[3]中的结构,为维持镜像频点不变,减小电感值的同时必须增大CgsM1.这会增加功耗,与低功耗目标背离,而C4可兼顾频点与电阻抵消,增加设计灵活性.对此可令

联立式(3)、(4)和(9),忽略pad的影响,令式(4)实部为0,可得阻抗Zin,filter及镜像频点fim、工作频点fop的表达式如下:

相比SAW滤波器,片内滤波器的性能略低,可增大镜像频率与工作频率间隔以弱化对滤波网络的性能要求,令镜像频率为3.5 GHz,式(12)除以式

(11),可得:

将式(13)代入式(12),进一步简化可得:

若电路满足式(13),式(12)就可简化使镜像频率和工作频率仅与LIR和Ctotal有关.而Ctotal与3个电容有关,在设计方面仍有困难,因此必须从功耗角度进行优化:采用尺寸和宽长比小的M1降低功耗,减小CgsM1,令C4远大于该值(6倍以上),则式(9)可简化为

由于C4、C5必须同时确定镜像频点和实部调谐,应仔细确定.已知Ctotal不变的情况下两电容若有一值过于接近Ctotal,则另一电容值足够大以满足式(15),因此两者不亦相差太远;又知C5以实现镜像频率的调谐功能,因而应弱化其对负阻调整的贡献.令C4=0.57 p F,C5=2.1 p F,实现滤波器频率和功耗的同时可调要求.

2 版图和仿真结果

基于Jazz 0.18-μm SiGe BiCMOS 工 艺,对LNA版图进行提参仿真,如图6所示.电路在提取寄生电阻R,电容C以及耦合电容CC的同时,采用sonnet仿真对互感、传输线效应进行估计,确保芯片仿真结果与实际结果最大程度上相符.芯片不带pad面积为525μm×579μm,滤波器的尺寸约为170μm×200μm.所有元件均为片上实现,其中电容CDC,block=2 p F,C1=0.5 p F,C2=0.73 p F,C3=0.1 p F,C4=0.57 p F,C5=2.1 p F,Cload=1.8 p F,电

感LB=1.7 n H,LE=0.46 n H,LIR=1.96 n H,Lload=0.43 n H.晶体管Q1、Q2尺寸相同,均为10 μm/0.15μm,MOS管 M1为4×40μm/0.18μm.电路电压为1.8V,总功耗为13 m W,基于功耗优化,有源滤波器的功耗仅为0.57 m W.

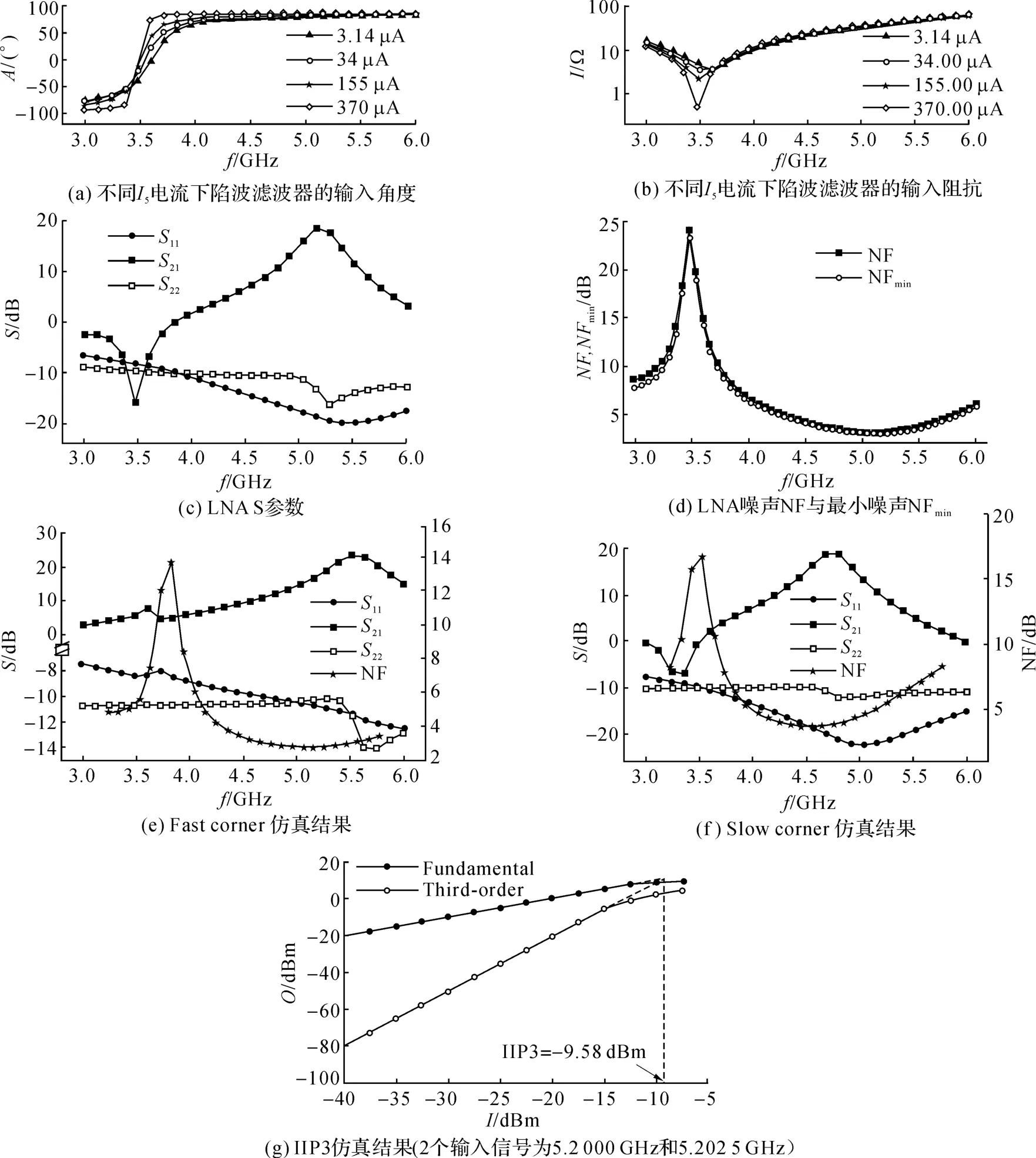

图7为电路各项仿真结果,其中图7(a)和图7(b)为陷波滤波器在不同电流I5下随频率变化的输入角度值和阻抗幅.可以看出,不同电流下角度值变化不大,而为实现镜像频率下最优阻抗,采用较大电流可以保证阻抗相消,当I5=370μA时性能最优.图7(c)为LNA的各项S参数,其中输入和输出反射系数均小于-10 dB,满足电路要求,增益方面镜像频率处出现较大的增益衰减,达到 -15.23 dB,而在工作频段(5.2 G附近)可达18.52 dB.图7(d)为LNA的噪声仿真结果,由于噪声与系统灵敏度密切相关,并且在宽频带系统下LNA的噪声一般要小于4 d B,需要所设计LNA在工作频率下具有较小的噪声系数.由图7(d)可知在镜像频率下,由于输入信号的大幅衰减电路呈现较大的噪声,而在工作频段下噪声为3.1~3.4dB,符合系统要求.电路的整体镜像抑制比高达33 dB,实现了滤波器片内集成下的优良性能.图7(d)~(f)分别为LNA在fast和slow工艺角下的仿真结果,其中fast工艺角下电路的性能并没有出现恶化,而增益甚至出现了提升;在slow工艺角下,电路的整体性能降低,表现为增益的降低和噪声的增加,然而输入和输出匹配仍在整个频段下小于-10 dB,满足设计要求.图7(g)为电路的线性性能仿真结果,可见电路在加入IR滤波器后仍能实现较好的线性性能,输入3阶交调点为-9.58 dBm.表1为近年来IR LNA与本电路的性能参数结果.

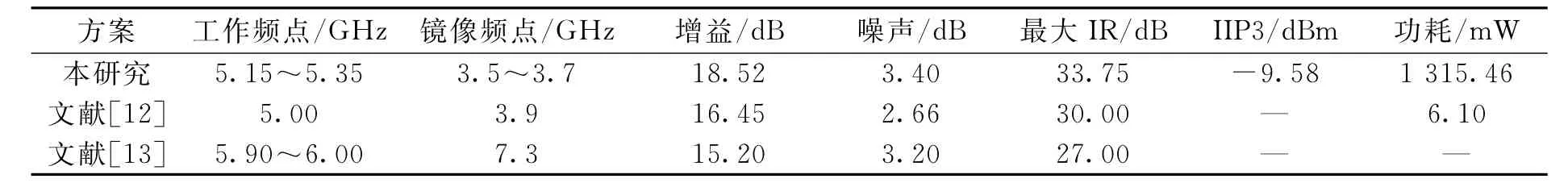

表1 IR LNA性能参数比较Tab.1 Performance comparisons of IR LNA

图7 LNA仿真结果Fig.7 Simulation results of LNA

3 结 语

本文基于SiGe工艺设计了一款802.11a具有镜像抑制功能的低噪声放大器.该放大器满足工作信号低噪声放大的同时实现了可观的镜频抑制.本文提出片内滤波网络的尺寸和功耗优化,进行了相应的理论分析和验证,未来的进一步设计将集中在可自偏置的低温漂型低噪声放大器设计.结果表明:该设计方法在确保输入输出匹配的前提下实现优良性能,对未来的超外差型射频接收机提供结构创新和设计参考,具有很强的应用价值.

(

):

[1]GOLMAKANI A,MAFINEJAD K,KOUZANI A.Design and optimization of LNA topologies with image rejection filters[J].International Journal of RF and Microwave Computer:Aided Engineering,2010,20(3):286- 297.

[2]MASUDA T,SHIRAMIZU N,NAKAMURA T,et al.SiGe HBT amplifiers with high image rejection for quasi-millimeter-wave frequency range[C]∥10th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems(SiRF2010).New Orleans:IEEE,2010:132- 135.

[3]KANG H Y,NGUYEN T K,PYO C S,et al.Imagerejection receiver using on-chip active notch filters for 2.4-GHz band wireless communication applications[J].Analog Integrated Circuits and Signal Processing,2013,74(3):577- 584.

[4]BAKI K A,EL-GAMAL M N.A 1 V 0.8 mW multi-GHz CMOS differential tunable image reject notch filter[C]∥48th Midwest Symposium on Circuits and Systems.Covington:MWSCAS,2005:802- 805.

[5]CHANG J F,LIN Y S.DC-10.5 GHz complimentary metal oxide semiconductor distributed amplifier with RC gate terminal network for ultra-wideband pulse radio systems[J].IET Microwaves,Antennas and Propagation,2012,6(2):127- 134.

[6]CHEN H K,LIN Y S,LU S S.Analysis and design of a 1.6-28 GHz gompact wideband LNA in 90-nm CMOS using aπ-match input network [J].Microwave Theory and Techniques,2010,58(8):2092- 2104.

[7]LIN Y T,CHEN H C,WANG T,et al.3-10 GHz ultra-wideband low-noise amplifier utilizing miller effect and inductive shunt-shunt feedback technique [J].Microwave Theory and Techniques,2007,55(9):1832-1843.

[8]RAZAVI B.RF microelectronics[M].2nd ed.New Jersey:Prentice Hall,2011:266- 305.

[9]MACEDO J A,COPELAND M A.A 1.9-GHz silicon receiver with monolithic image filtering[J].Journal of Solid-State Circuits,1998,33(3):378- 386.

[10]JENEI S,NAUWELAERS B K J C,DECOUTERE S.Physics-based closed-form inductance expression for compact modeling of integrated spiral inductors [J].Journal of Solid-State Circuits,2002,37(1):77- 80.

[11]ULUTAS B H,ISLIER A A.A clonal selection algorithm for dynamic facility layout problems[J].Manufacturing Systems,2010,28(4):123- 131.

[12]LEE L C,ABU K B A,ALBERT V K.A 5 GHz CMOS tunable image-rejection low-noise amplifier[C]∥2006 International RF and Microwave Conference Proceedings.Putrajaya:RFM,2006:152- 156.

[13]WEI L S,WU H I,JOU C F.Design of low-voltage CMOS low-noise amplifier with image-rejection function.[J].Electronics Letters,2008,44(16):1- 2.