基于FPGA的智能函数发生器设计

孙晓昕,陈凡非,吴鹏飞,曲 伟

(黑龙江大学 电子工程学院,哈尔滨 150080)

基于FPGA的智能函数发生器设计

孙晓昕,陈凡非,吴鹏飞,曲 伟*

(黑龙江大学 电子工程学院,哈尔滨 150080)

针对传统函数发生器设计的缺点,提出了一种智能函数发生器设计方法。该方法采用Qt设计上位机程序与USART串行通信技术相结合,实现对下位机的实时控制,兼顾了系统的灵敏度和鲁棒性。利用该方法设计了智能函数发生器模数转换模块、外部调制电路模块和滤波电路模块,并基于EP4CE6F17C8型FPGA芯片实现频率调制、幅度调制、偏置调制、波形调制以及占空比调制等功能。测试结果表明:该函数发生器能产生正弦波、方波、三角波、锯齿波等4种函数波形,其调频范围为1 Hz~1 MHz,调幅范围为-10 V~+10 V。

现场可编程门阵列;直接数字频率合成;智能仪表;串行通信

0 引 言

函数发生器是一种历史悠久的测量仪器,它是一种具有频率、幅度、偏置等调制功能的多波形信号源,可以产生特定波形信号用于测试、校准、甚至为其他电路提供能源等工作。随着现代通信技术的不断发展,人们对函数发生器的性能提出了更高的要求,不仅能产生任意波形,且要求操作方便快捷,输出波形稳定度好,频率精确度高。为了适应现代通信电子技术的发展和市场的需求,研究函数发生器具有非常重要的理论意义和应用价值。

随着现场可编程门阵列(FPGA)技术的发展以及直接数字频率合成(DDS)技术的日渐成熟,为函数信号发生器提供了理论依据和技术支持,极大地提高函数信号发生器的性能,降低了成本。

在电子领域,函数发生器可用于生产测试、仪器维修、科研实验等。从电子角度讲,函数发生器主要用作包括激励源、基准信号源、波形模拟器等[1]。在非电子领域,函数发生器通常结合该领域的设备一同工作,如结合医疗设备检测患者心率,结合工业自动化设备实现各流程时间监控,函数发生器已经融入各行各业,某些专用函数发生器更是如此[2]。

1 系统方案设计

函数发生器的主要性能指标包括:频率、幅度、相位、偏置、波形等,在一些特殊场合,还需要考虑诸如输出阻抗、输出准确度、输出稳定性等因素[3]。

目前函数发生器的实现方法主要有:采用分立元件搭建的函数发生器,采用专用DDS芯片搭建的函数发生器,以及使用FPGA配合Verilog程序设计搭建的函数发生器等。

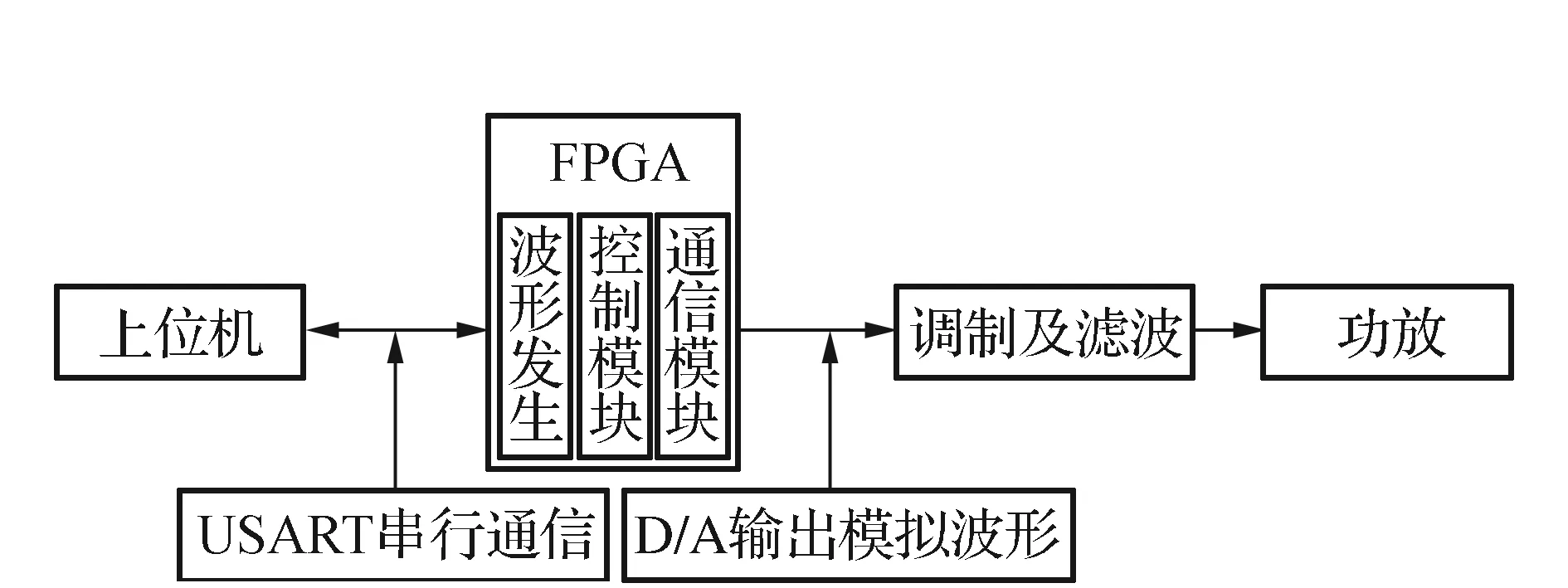

1.1 基于FPGA 的智能函数发生器设计方案

针对传统函数发生器设计当中的不足,本文提出了一种智能函数发生器设计方法。该方案上位机部分使用Qt编写控制软件;FPGA部分构建波形发生模块、控制和通信模块等;滤波及调制部分用以对信号进行降噪和波形变换以达到所需要的标准;功放部分提高输出功率、降低输出阻抗。基于FPGA 的智能函数发生器整体方案见图1。

图1 本设计中函数发生器结构框图Fig.1 Block diagram of the function generator

1.2 函数发生器频率调制

FPGA波形发生模块中调频部分使用DDS技术实现,其工作原理见图2。图2表示半径为1的单位圆,半径与横轴的夹角即相位角。则当半径绕圆旋转时,其在纵轴投影也将有一系列数值,范围在+1到-1之间。此投影即为正弦幅值,见图3。

图2 单位圆表示的正弦函数Fig.2 Sine function presented by unit circle

图3 根据相位线性特性产生的正弦波Fig.3 Sine wave produced according to phase linearity

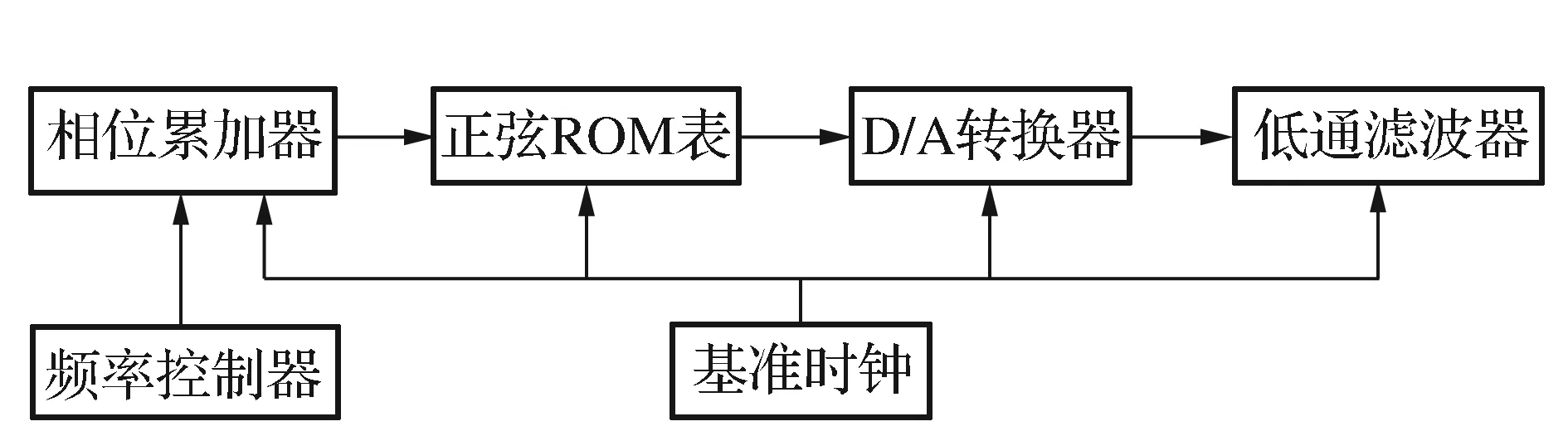

本设计中DDS原理图见图4。由以下几部分组成:相位累加器、正弦ROM表(用于相位-幅度变换)、D/A转换器、低通滤波器[4]。

图4 典型DDS原理图Fig.4 DDS schematics

相位累加器在每个时钟到来时对频率控制器的控制字进行一次累加,数值溢出后继续进行累加运算。相位累加器实质上输出了一个阶跃的锯齿波信号,符合正弦ROM表所需的线性的相位输入量。

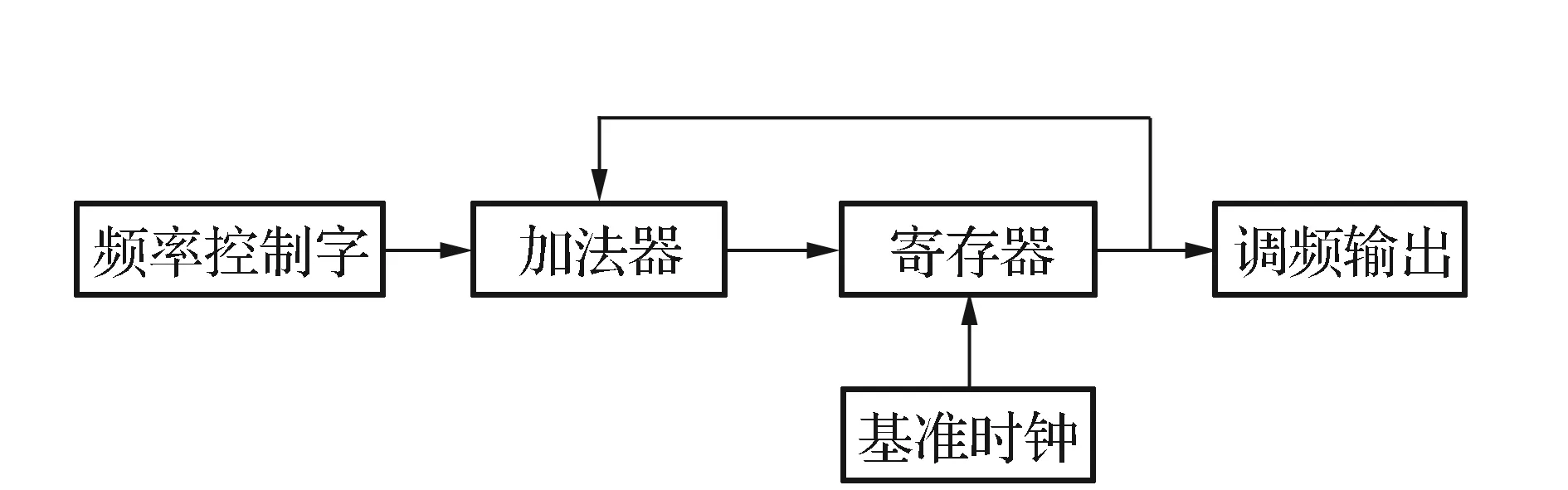

DDS中相位累加器可由一组加法器和寄存器构成,原理图见图5。

图5 相位累加器构成Fig.5 Structure of phase accumulator

1.3 函数发生器幅度调制

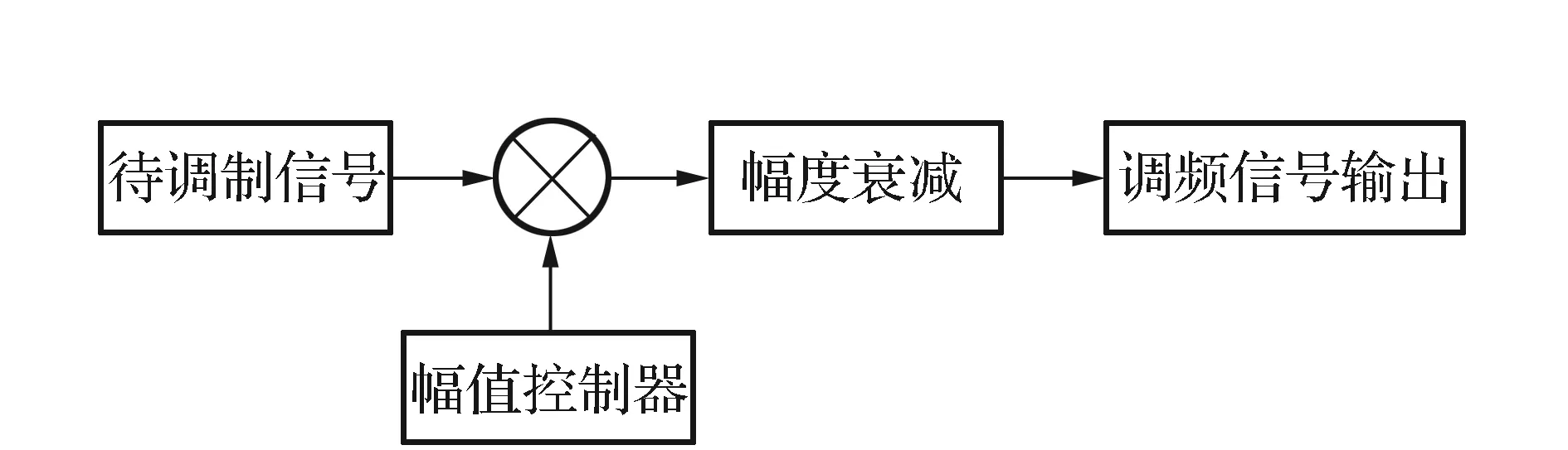

函数发生器幅值调制使用乘法器建立,将输入信号及幅值调制控制字相乘,可得到与输入信号波形相同,幅值与控制字成正比的输出信号。函数发生器幅度调制部分见图6。

图6 使用乘法器进行幅度调制Fig.6 Using multiplier to conduct AM

2 系统硬件设计

2.1 FPGA

采用Altera公司Cyclone IV系列的EP4CE6F17C8芯片作为主控芯片。芯片使用BGA封装,包含256个引脚,其中输入输出引脚179个。芯片内核电压1.2 V,片载6 272个逻辑单元,392个乘法器。根据ALTERA官方的数据,CYCLONE IV相对CYCLONE III来说,功耗减少25%。

FPGA部分外部电路包括50 MHz晶振,EPCS16配置芯片,板载3.3、2.5、1.2 V电源,JETG接口和AS接口,及扩展I/O口等。

2.2 D/A数模转换

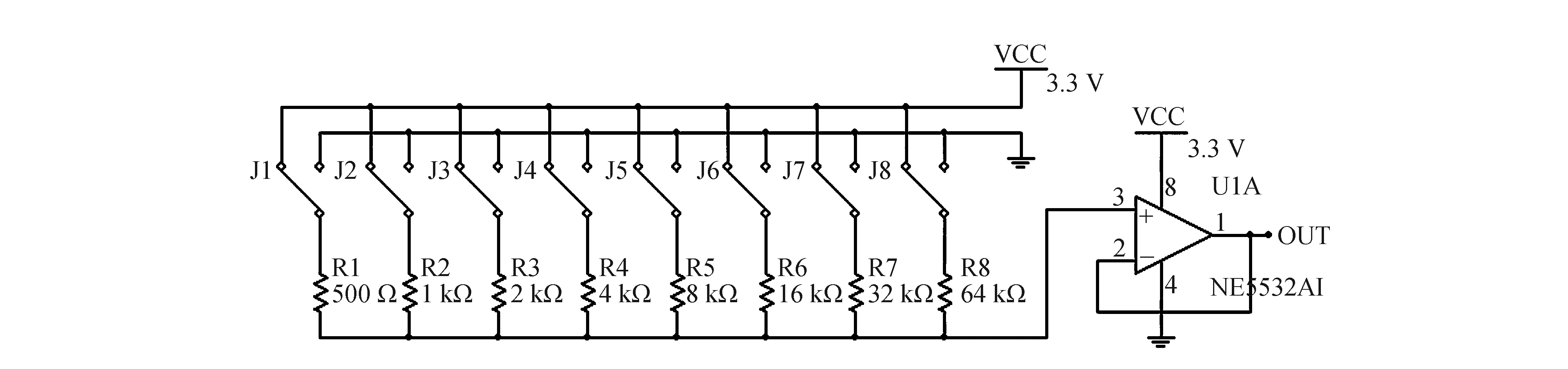

D/A数模转换采用权电阻网络D/A转换,电路见图7[5]。电路中采用非常多数值的电阻,且电阻阻值成2N倍数关系,故得名权电阻网络。切换电阻接入电平,可改变电阻网络的分压结构,改变输出电压。

2.3 输出信号调制与滤波

D/A转换器经FPGA后输出电压值为0~3.3 V,而函数发生器的输出范围-10~+10 V,故外部需要偏置电路和放大电路。由于DDS技术是纯数字频率合成技术,工作时会引入很大的信号杂散,需设计输出滤波电路,以消除信号杂散。

图7 权电阻网络D/A转换器Fig.7 Right resistor network D/A converter

输出调制及滤波电路见图8。U1A为D/A的输出跟随器,用于扩大D/A输出电流,R13电位器用于手动调节偏置电压,U1B跟随器用于匹配U2A减法器输入阻抗。而信号经过U2A放大6.1倍后,变为-10~+10 V输出信号。C1、C2、R15、R16共同组成二阶低通滤波器电路,截至频率约为30 MHz,可将接近系统时钟频率杂散信号滤除。

3 系统软件设计

3.1 DDS模块正弦波发生

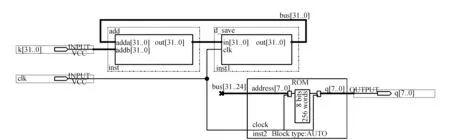

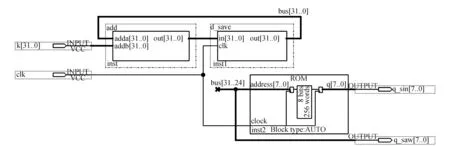

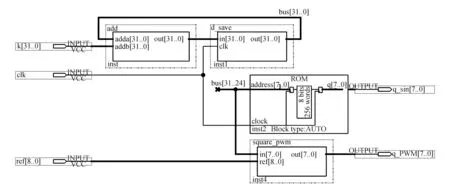

使用Quartus II软件实现的DDS正弦发生模块见图9,主要包括相位累加器、正弦数值表、系统时钟。

图9 DDS正弦发生模块原理图Fig.9 DDS sine generator module schematics

图10 DDS锯齿发生模块原理图Fig.10 DDS sawtooth generator module schematics

3.2 DDS模块锯齿波发生

使用Quartus II软件实现的DDS锯齿发生模块见图10。在正弦模块基础上,将ROM表地址端直接引出,即可输出锯齿波。

3.3 DDS模块三角波发生

三角波发生需要采用特定的运算。将锯齿波信号前半周期数值翻倍,后半周期数值翻转后再翻倍,运算过程用见下式:

(1)

式中x为锯齿波输入;y为三角波输出。使用Quartus II软件搭建的DDS三角发生模块原理图[6]见图11。

3.4 DDS模块方波发生

DDS模块的方波发生仅需比对正弦输入数值与基准数值控制字的大小,将比对结果量化为高低两种状态并输出[7]。为DDS方波模块添加PWM脉宽调制功能,则需将基准数值端引出为输入引脚[8]。由此可见,方波变换部分仅需构建8位数值比较器即可实现。图12为使用Quartus II软件搭建的DDS带PWM功能方波发生模块原理图。

图12 DDS带PWM功能方波发生模块原理图Fig.12 DDS with PWM square generator module schematics

3.5 幅度及偏置调制

采用乘法器实现幅度调制,将8位并行输出端与8位幅度控制字相乘,可得16位乘积。相比之下,使用16位数据总线供D/A转换受益不大,故此处使用除法器将16位总线换算为8位总线,以节约系统资源[9-10]。

偏置部分使用加减运算实现。对信号函数式的整体加减可以实现信号沿幅度轴的上下平移。故采用带有参数的加法器即可实现信号的偏置调节功能。

3.6 上位机软件设计

上位机软件使用Qt编写,软件使用滚动条和数值设置共同调节相应数据。软件中可任意操控下位机的幅值、偏置、频率、占空比和波形等参数。软件界面见图13。

图13 上位机软件界面Fig.13 PC software interface

4 输出性能测试

4.1 频率测试

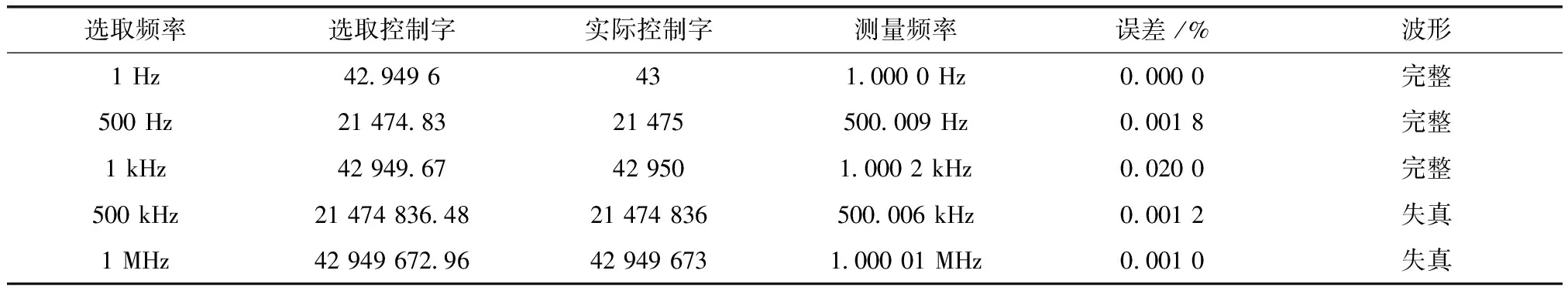

进行频率测试时,分散选取5个测试频率点,计算各自控制字。使用RIGOL公司生产的DS2102数字示波器进行测试,测试数据见表1。

4.2 幅度测试

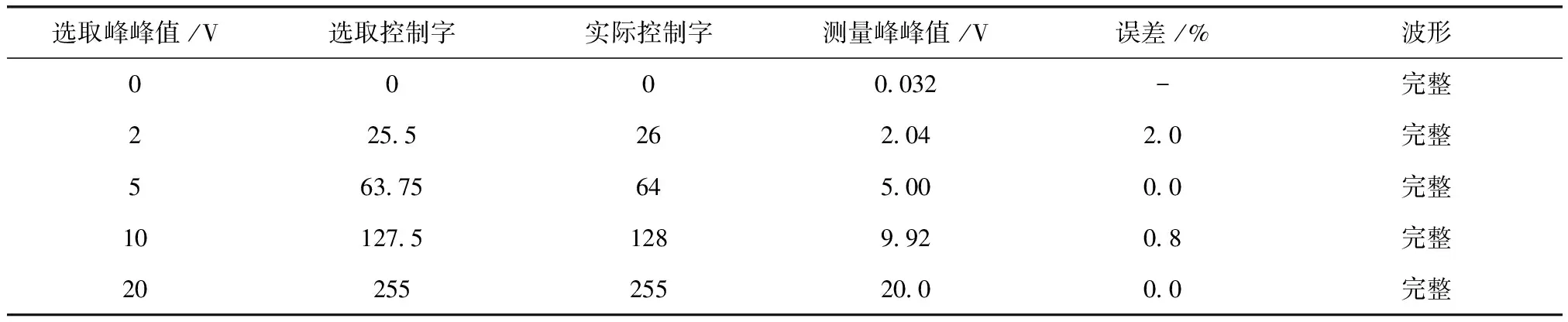

进行幅度测试时,分散选取5个测试峰峰值点,计算各自控制字。测试数据见表2。

由测试数据可见,在幅值较大情况下,误差很小,在控制字量化时产生的误差影响也不大。但当幅值较小时,误差很大。其原因是电阻网络D/A分辨率不足,无法在数值极低情况下提供较好的步进量。

表1 频率测试数据整理

表2 幅度测试数据整理

5 结 论

本文提出了一种智能函数发生器硬件设计方案,该方案克服了传统函数发生器设计的缺陷,采用Qt编写上位机控制程序与USART串行通信技术,实现了实时操作函数发生器输出参数等功能;基于FPGA芯片构建波形发生模块、控制和通信模块等,完成智能函数发生器实物制作,实现了包括正弦波、方波、三角波、锯齿波等波形发生功能。同时,系统的滤波及调制模块用以对信号进行降噪和波形变换以达到所需要的标准。功放模块提高了系统的输出功率,降低输出阻抗。

经测试,该函数发生器的输出频率为1 Hz~1 MHz,频率步进值1 Hz,输出幅度-10~+10 V,幅度步进值0.1 V,方波占空比步进值1%。

[1]马骏然,张春熹.基于FPGA的直接数字频率合成波形发生器[J].电子测量技术,2006,4(3):78-79.

[2]Yu X,Wang J L,Gu H D.Design of microwave signal generator based on embedded linux[J]. Chinese Journal of Electron Devices,2008,31(3):941-944.

[3]赵茂泰.电子测量仪器设计[M].武汉:华中科技大学出版社,2010:114-147.

[4]曲尧丽,杨景常,刘光明.可程控智能函数发生器的实现[J].中国仪器仪表,2006,3(2):62-64.

[5]Geng X, Dai F F, Irwin J D.24-bit 5.0 GHz girect digital synthesizer RFIC with direct digital modulations in 0.13 us [J]. Solid-State Circuits, IEEE Journal of.2010,45(5): 944-954.

[6]杨 蕊.基于DDS技术的实用信号源设计[D].武汉:华中师范大学,2012:15-18.

[7]王 丹,李 平,文玉梅.采用DDS频率合成的虚拟信号发生器研究[J] .传感技术学报, 2007,9(3):586- 591.

[8]李海松,张奇荣,权海洋.DDS的相位截断及相应的杂散信号分析[J].微电子学与计算机,2006,23(2): 141-143.

[9]Wang C C, Teng Y, She H C. A 13-bit resolution ROM-less direct digital frequency synthesizer based on a trigonometric quadruple angle formula [J]. IEEE Trans, 2004,12(9): 895-900.

[10]胡鸿豪,李世红,蔡志端,等.基于单片机和DDS的信号发生器设计[J].电子元器件应用,2006,8(12):47-49.

Design of smart function generator based on FPGA

SUN Xiao-Xin, CHEN Fan-Fei, WU Peng-Fei, QU Wei*

(School of Electronic Engineering, Heilongjiang University, Harbin 150080, China)

A intelligent function generator design method was proposed according to the shortcomings of traditional function generator. The method used Qt to design upper computer program and used USART serial communication come true the real-time control to the lower computer. The sensitivity and robustness of the system were taken into account. The analog-digital converter modular, the external modulation circuit modular and the filter circuit modular were designed by this method, and functions of frequency modulation, amplitude modulation, offset modulation, waveform modulation, duty cycle modulation and so on were realized based on FPGA chip (EP4CE6F17C8). From the experimental results: this function generator can produce sine wave, square wave, triangular wave and sawtooth wave. The frequency range was 1Hz to 1MHz and the amplitude modulation range was -10 V to +10 V.

FPGA; DDS; intelligent instruments; serial communications

10.13524/j.2095-008x.2015.01.016

2014-08-20

http://www.cnki.net/kcms/detail/23.1566.T.20150119.1618.005.html

2012年黑龙江省研究生创新科研项目(YJSCX2012-317HLJ);2014年黑龙江大学研究生创新科研项目(YJSCX2014-074HLJU)

孙晓昕(1988-),女,山东郓城人,硕士研究生,研究方向:电路分析与测试,E-mail: sxxszcb@126.com;*通讯作者:曲 伟(1970-),女,黑龙江哈尔滨人,教授,硕士研究生导师,研究方向:电路分析与测试,E-mail: quwei70@163.com。

TP212.6

A

2095-008X(2015)01-0080-07