高速数据采集传输系统的设计与实现

高新平

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

高速数据采集传输系统的设计与实现

高新平

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

摘要为了应付电子战复杂电磁环境,具有宽的输入带宽是数字侦察接收机应当满足的必备条件之一。输入带宽越宽,则采样速率和输出的数据率也越高。围绕宽带数字侦察接收机的2个主要环节即高速ADC采集和数据传输,提出并实现了基于高速采样器、大规模 FPGA和万兆以太网的高速数据采集传输方案。该方案有效地解决了采样率高达5 Gsps的A/D采样和高流量采样数据实时传输问题。在远程监控终端的控制下,系统完成高速数据采集和传输,具有高度的灵活性和可扩展空间。

关键词高速采样器;FPGA IP核;万兆以太网;高速数据采集传输

0引言

为了适应电子战日益复杂的电磁信号环境,对数字侦察接收机的输入带宽要求越来越宽。这是由于侦察接收是非协作侦收,侦收之前并不确定辐射源的频率﹑带宽及持续时间等信息。宽开输入可以降低系统的响应时间﹑增大截获概率﹑提高对复杂信号的接收处理能力[1]。而根据奈奎斯特采样定理和带通信号采样理论[2],采样速率至少是信号带宽的2倍,所以宽带侦察接收机对采样速率的要求也越来越高。

根据宽带侦察接收机的需要,提出了一种基于高速采样器和大规模FPGA实现的高速数据采集传输系统设计方案,实现了采样率高达5 Gsps、采样位宽10 bit的A/D采样并保证高流量采样数据实时可靠传输。

1高速数据采集传输系统总体方案

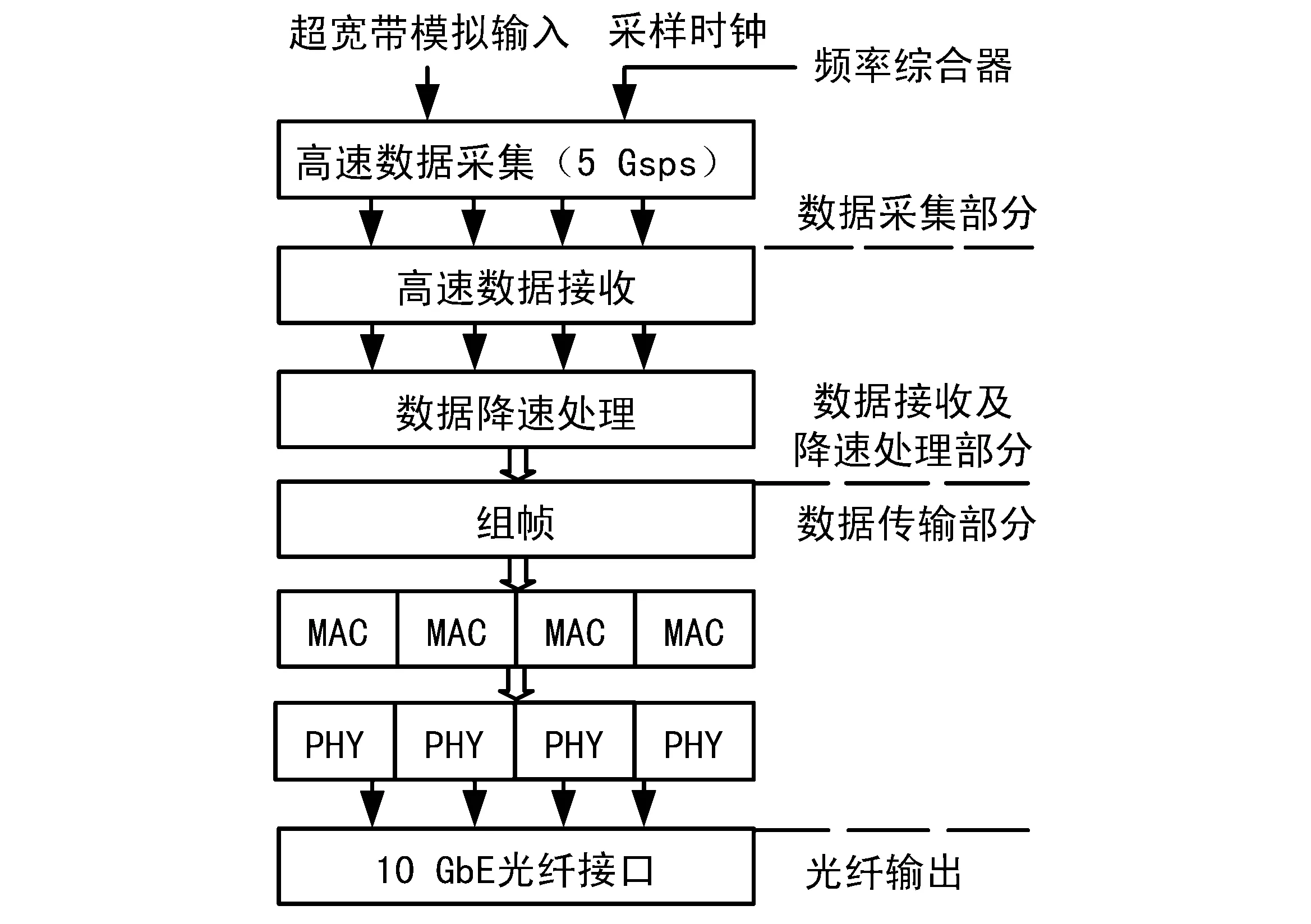

本设计基于高速采样器EV10AQ190、大规模FPGA XC6VSX315T和万兆以太网,主要实现了采样速率为5 Gsps的高速数据采集、数据接收、降速处理及数据的实时传输等功能。

高速数据采集:数据采集以高速采样器EV10AQ190为核心,采用精确的时钟相位控制技术,实现单通道5 Gsps,转换位数10 bit的高速采样,能够完成输入带宽达3.2 GHz的模数变换。

数据接收及降速处理:数据接收及降速处理以大规模FPGA XC6VSX315T为核心,利用输入串并转换逻辑资源和输入延迟单元,实现采样数据的可靠接受和降速处理。

数据传输:数据传输是以万兆以太网为核心,将降速后的数据组帧和打包处理后通过万兆以太网实时输出。

高速数据采集传输系统原理如图1所示。

图1 高速数据采集传输系统原理

2高速数据采集传输系统设计

高速数据采集传输系统设计主要分为高速数据采集设计、时钟设计、万兆以太网设计、电源设计及FPGA软件设计。

2.1 高速数据采集设计

ADC选用EV10AQ190,可支持四通道最高采样率1.25 Gsps或二通道最高采样率2.5 Gsps或单通道最高采样率5 Gsps的数据采集。本设计采用单通道5 Gsps模式。采样结果分别由A、B、C及D四个端口共同输出,每个端口10 bit数据输出,速率为1.25 Gsps。4路高速数据送入FPGA后,进行进一步降速处理,高速数据采集部分硬件图如图2所示。

设计中利用FPGA产生SPI总线控制ADC,通过控制增益、偏移和相位等优化采样性能,同时控制FPGA的工作模式和带宽以适应不同工作场合的需要,运用非常灵活[3]。

在高速数据采集模块设计中,由于采样器工作的频率非常高,所以对PCB走线中部分关键信号进行了信号完整性仿真。仿真软件用的是HYPERLYNX8.0。仿真中通过对叠层分布﹑线宽和线间距的控制进行信号完整性分析,最后按照最优仿真结果对PCB设计。

2.2 时钟设计

采样时钟由频率综合器提供,系统控制器通过SPI总线对频率综合器进行配置,以实现对不同采样率的要求。频率综合器可以提供25~30 00 MHz的时钟频率。

其他所用时钟由2片AD9523来提供,其中需要为FPGA提供6路频率为156.25 MHz的参考时钟,为BCM8725提供6路156.25 MHz的参考时钟,为千兆PHY芯片提供25 MHz时钟等。

2.3 万兆以太网设计

10 GbE以太网采用MAC加PHY加光纤模块的结构进行设计。MAC用FPGA的IP核实现。PHY采用专用芯片(BCM8725),完成万兆以太网物理层的各项功能。BCM8725和FPGA之间有2组互相独立的XAUI接口,每个XAUI接口包含4个lanes差分通道,每个通道的速率为3.125 Gbps[4]。在本设计中PHY芯片使用LAN PHY模式,数据有效传输速率为10 Gbps;一共有6组XAUI接口和FPGA相连,能够实现6路万兆以太网同时传输,有效数据传输速率最高达60 Gbps。

2.4 电源设计

设备使用220 V交流电供电,通过电源模块产生+12 V直流电源给板卡直接供电,板卡内部生成所需各种电源,同时在电源设计中加了滤波和去耦等。

2.5 FPGA软件设计

FPGA是实现高速数据采集和传输的核心部分,主要完成AD采样时序校正及数据降速预处理、采样数据组帧处理和万兆以太网MAC层接口实现等功能。

2.5.1AD采样时序校正及数据降速处理

采样器EV10AQ190采用双沿采样模式,并且同步时钟工作在DDR模式,所以当采样率为5 Gsps时,采样器内部首先将采样数据分成4路输出,每路数据速率为1.25 Gbps,这样进入FPGA的随路时钟就高达625 MHz,就FPGA而言,625 MHz对时序要求近乎苛刻,所以为了有效的进行数据处理,必须进行降速,从而使时钟能够满足FPGA时序电路要求。

数据的降速处理主要通过ISERDES模块完成,它是专用的串并转换器,具有专门用来帮助实现高速源同步应用的特定时钟控制和逻辑功能。

一个ISERDES模块最多可以支持6个数据位,即1∶6解串,构建大于1∶6的串并转换器需要用2个ISERDES模块。每个I/O模块中有一主一从2个ISERDES模块。通过将主ISERDES的SHIFTOUT端口连接到从ISERDES的SHIFTIN端口,可以将串并转换器最大扩展到1∶10(DDR)[5]。在ISERDES模块中需要用到2个时钟[6]:一个是高速输入时钟(CLK),用来对输入串行数据流进行时钟控制;另外一个是分频时钟输入(CLKDIV),用来驱动串并转换器,其通常是CLK的一个分频版本。在本设计中,使用串并转换器将数据扩展到1∶8,高速输入时钟为625 MHz,输入的串行数据速率为1.25 Gbps,经过降速后将1路串行数据分成8路,每路的数据速率和时钟速率都为156.25 MHz。

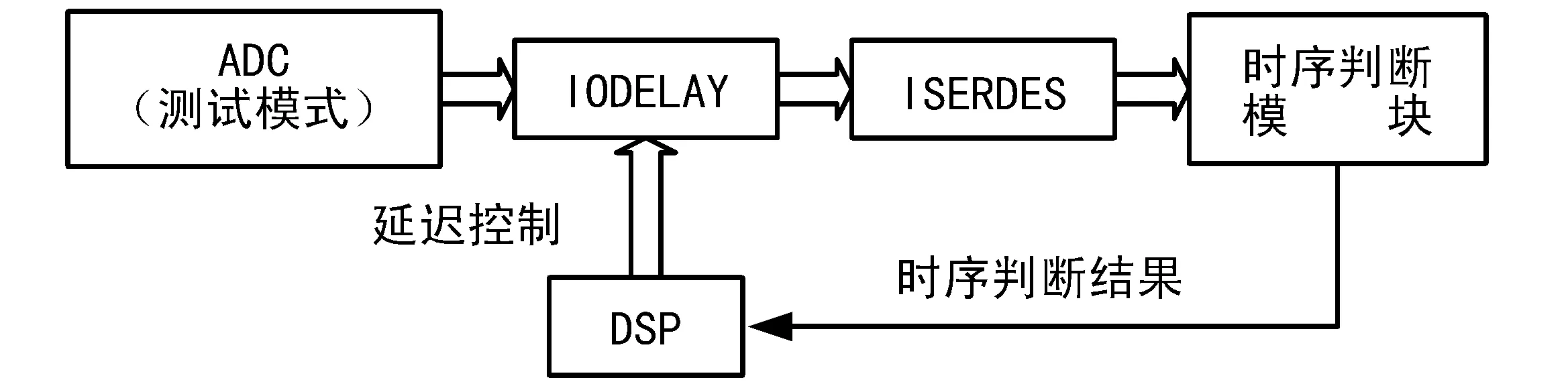

由于进入FPGA的数据速率非常高,所以很有可能时序不稳定,经过FPGA后得到的采样数据会出现毛刺,在实际的调试过程中也的确存在这个问题。在本设计中是通过采样时序校正来解决这个问题。采样时序校正处理如图3所示。

图3 采样时序校正处理

采样器设置为测试模式,使其不断的发送固定循环数据,DSP对IODELAY的延迟进行控制,将最后得到的采样数据和正确数据进行比对,并将结果返回给DSP,最后DSP挑出满足时序的配置对IODELAY进行配置。

2.5.2采样数据组帧处理

采样数据降速处理之后,需要将采样数据按照MAC层要求的输入格式组帧,一帧数据包括目地地址、源地址、数据类型、采样数据[7]和时标;在FPGA中的实现流程为:将采样数据缓存到FIFO中,当数据量达到所设定的值时将数据读出,并在采样数据之前加上目的地址、源地址、数据类型和时标。加上时标之后解决了多路数据间的同步问题,为接收端还原采样数据提供依据。数据输出的同时产生一帧数据相对应的起始标志,数据结束标志和数据有效标志。

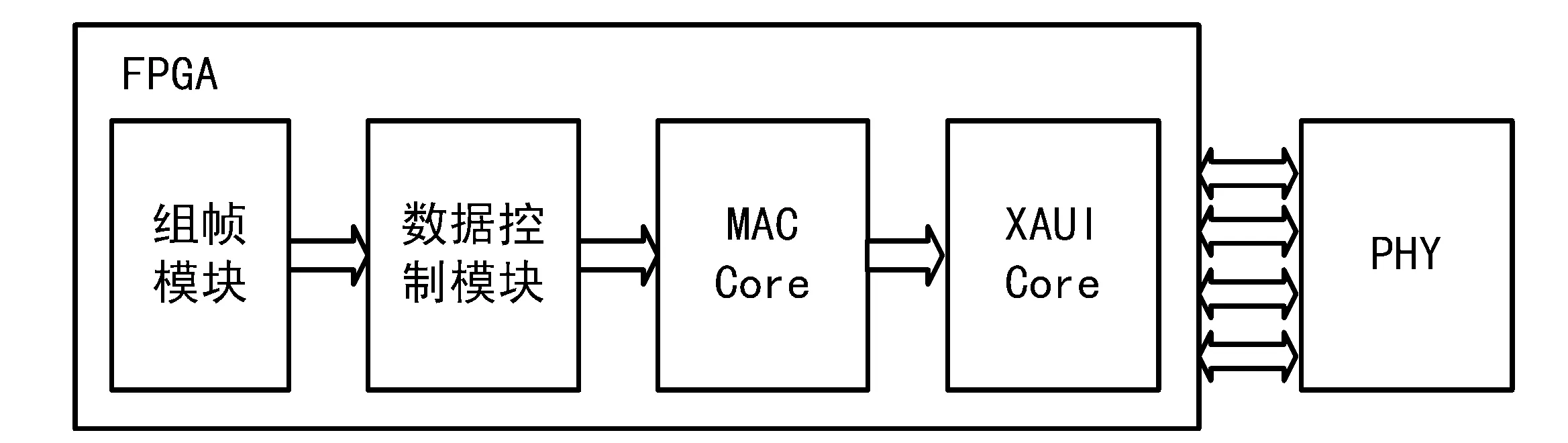

2.5.3万兆以太网MAC层接口设计

设计中万兆以太网整个MAC层以及相对应的输入输出接口都是在FPGA中实现[8],实现框图如图4所示。数据的处理流程为:将组帧数据送入数据控制模块进行流量的控制,数据流量控制模块主要是对输入帧数据流进行缓存,并对帧速率进行控制,即当输入数据速率大于以太网接收的速率它就会进行丢帧处理[9],以确保以太网数据发送正常;再将数据送入MAC核进行帧的封装、解封、地址匹配、保证最小最大的长度、CRC校验[10]等;最后通过XAUI核进行MAC核接口和PHY接口的转换,将数据送入PHY模块。

图4 10GbE MAC层接口设计

3系统测试

在本系统中主要测试了万兆以太网传输的误码率和采样器的无杂散动态范围这两项性能。

万兆以太网传输误码率测试的方法是通过万兆以太网不断循环发送一组已知数据,在接收端对接收数据进行分析测试,测试结果:在传输数据速率小于8.4 Gbps时,没有发现丢数据帧的现象,数据的误码率为0,满足系统要求。

采样器的无杂散动态范围测试的方法是在采样率为5 Gsps、输入分别为620 MHz和1 200 MHz单音信号(按照采样器数据手册中的说明选择的输入频点)时进行测试。最后经过高速数据采集与传输系统输出的采样数据频域图如图5所示。

图5 输出采样数据频域

从采样数据频域图可知,当采样率为5 Gsps、输入单音信号为620 MHz时,SFDR达到54.58 dBc,满足系统大于53 dBc的要求; 当采样率为5 Gsps、输入单音信号为1 200 MHz时,SFDR达到50.23 dBc,满足系统大于50 dBc的要求。

综合以上2项测试,高速数据采集传输系统能够满足系统指标要求。

4结束语

高速数据采集传输系统的高达5 Gsps的采样率为大宽带采样甚至射频直采奠定了基础,同时系统采用了万兆以太网进行数据传输,使得传输速率快、传输距离远、传输可靠性高,具有较大的应用价值。系统仅包括高速数据采集传输板、频率综合器和电源模块3个部分,整个系统关键技术都集中在大规模FPGA中实现,这样不仅降低了设计难度,而且减少其他芯片的数量,使得设计成本和整个系统的功耗都大为降低,为以后工程应用打下了良好的基础。

参考文献

[1]TSUI J.宽带数字接收机[M].北京:电子工业出版社,2002.

[2]杨小牛,楼才义.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[3]刘丽格,李天保,石鑫刚.一种板间高速传输系统的设计与实现[J].无线电通信技术,2011,37(4):53-55.

[4]苗澎,王志功. 万兆以太网物理层技术[J].电路与系统学报,2010,11(2):12-13.

[5]黄擘.多通道高速串行LVDS信号解串器设计[J].信息技术,2012(8):161-163.

[6]屈超.多通道ADC的高速接口设计[J].无线电通信技术,2013,39(3):76-78.

[7]刘冀川,李冬梅. 万兆以太网技术的研究与实现[J].无线电工程,2012,42(12):7-9.

[8]马腾飞,吴志勇,李增. 基于XAUI协议的10Gb/s光纤通信系统[J].计算机工程,2010,36(17):264-265.

[9]刘昭,苏厉,金德鹏. 10G以太网系统中的并行CRC编解码器的设计[J].电子技术应用,2004(4):47-50.

[10]张友亮,刘志军,马成海. 万兆以太网MAC层控制器的FPGA设计与实现[J].计算机工程与应用,2012,48(6):77-79.

高新平女,(1985—),工程师。主要研究方向:数字信号处理、高速电路设计。

Design and Implementation of High Speed Data

Acquisition and Transfer System

GAO Xin-ping

(The54thResearchInstituteofCETC,ShijiazhuangHebei050081,China)

AbstractTo be adapted to the complicated electromagnetic environment of electronic warfare,digital reconnaissance receivers must have wide bandwidth.The wider the bandwidth is,the higher sampling rate and output rate are required[1].On the two topics of wideband digital reconnaissance receiver,that is,high rate sampling and high speed data transfer,the paper proposes and implements a high speed data acquisition and transfer system based on high speed ADC,FPGA and 10Gb Ethernet.The system solves the problem of high rate sampling and high speed data transfer effectively.Finally,under the control of a remote monitoring terminal,the system completes high speed data acquisition and transfer successfully,which shows its good extensibility and flexibility.

Key wordshigh speed ADC; FPGA IP Core; 10Gb Ethernet; high speed data acquisition and transfer

作者简介

基金项目:国家部委基金资助项目。

收稿日期:2015-03-06

中图分类号TN919.3

文献标识码A

文章编号1003-3106(2015)06-0041-03

doi:10.3969/j.issn.1003-3106.2015.06.12

引用格式:高新平.高速数据采集传输系统的设计与实现[J].无线电工程,2015,45(6):41-43,54.