基于Avalon-MM突发传输的PCI从接口设计

李晓晗,张 航,倪光华

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

基于Avalon-MM突发传输的PCI从接口设计

李晓晗,张航,倪光华

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

摘要PCI总线协议使用广泛,但协议内容较复杂,利用Altera公司提出的Avalon总线结构,实现方法简单,性能较好。设计一种基于Avalon-MM突发模式的PCI从接口结构,对Avalon-MM突发模式的读、写传输时序进行了简要介绍。根据Avalon-MM总线的时序要求,实现一种符合时序规范的RAM控制器,通过该控制器,PCI从接口可与RAM进行高速数据交换,通过PCI从接口,实现了PCI主外设与FPGA内部RAM的高速数据交换。经FPGA验证PCI从接口满足Avalon总线规范的时序要求,达到了预定的目标。

关键词Avalon-MM;突发传输;PCI从接口;SOPC Builder

0引言

PCI总线[1-3]是Intel 公司于20世纪90 年代初提出的一种独立于处理器的总线标准,由于其具有高性能、突发传输、兼容性强及性价比高等优点,PCI 总线得以在业界迅速流行,成为微型计算机事实上的总线标准。但PCI 总线规范本身比较复杂,其接口实现比ISA和EISA 较复杂。目前开发PCI 接口大体有以下2种方案[4]:

①用PCI 专用芯片组,以实现完整的PCI 主控模块和目标模块的功能,将复杂的PCI 总线接口转换为相对简单的用户接口,用户只需设计转换后的总线接口。但该方案系统结构受接口芯片限制,不能灵活地设计目标系统,且成本较高。另外,ASIC 芯片及其所需的非易失性存储器等,占用了一定的板卡面积。

②用FPGA中的专用IP 核[5-7]来实现PCI 接口功能,设计者需知道IP函数的功能以及如何使用,也需了解PCI规范的具体内容。

本文主要介绍了利用PCI接口实现高速数据传输。为节省板卡面积、简化设计方案,采用了第2种方案,将PCI接口部分集成至FPGA内部,利用FPGA设计的IP核,实现PCI接口功能。

1Avalon总线

Avalon总线[8]是Altera 公司专门为SOPC系统指定的一套总线标准,它定义了主从接口对之间通信的信号类型和时序关系,在结构上不同于传统的共享式总线。它在需要连接的每一个主从接口对之间都有点到点的连接,不同的主从接口对之间可以同时进行通信,所以大大提高了系统的性能。Avalon 总线标准包含Avalon-MM接口规范和Avalon-ST 接口规范。Avalon-MM接口是一套互联式总线接口,主要用于多节点的互联,而Avalon-ST接口是一种单向点对点的接口,主要用于单向高速数据流的传输。为方便节点互联和数据的双向高速传输,本设计采用Avalon-MM接口规范。

Avalon-MM工作模式主要有4种:基本读写传输、具有固定等待周期的读写传输、流模式传输和突发模式传输。基本读写传输是所有传输的基础,读传输可在一个时钟周期内完成,写传输通常需要一个工作周期完成一个地址的写操作,吞吐量较低。具有固定等待周期的读写传输与外设属性有关,如大多数常用的片外异步外设,在发出读信号之前,需要地址等信号先稳定一段时间。流模式传输每个数据都需要一个地址,与突发模式下传输方式一个突发传输地址对应多个数据阶段相比,传输效率和总线占用时间等性能不如后者,因此本设计选用Avalon-MM突发模式传输。

SOPC Builder[9,10]是Altera开发的一款系统生成和集成工具。SOPC Builder所产生的片上电路系统模块包括Avalon总线、主外设和从外设。Avalon总线在SOPC Builder中添加外设之后会自动生成,并且会随着外设的添加和删减而自动调整,最终的Avalon总线结构是针对外设配置而生成的一个最佳结构。

2PCI从接口总体设计

本设计的主要目的是PCI主外设通过PCI总线对FPGA上的片上RAM进行数据交换,PCI从接口集成在FPGA内部。若直接使用IP核来实现PCI从接口,需熟悉复杂的PCI总线协议才可设计实现RAM控制器。若采用.SOPC的开发方法,使用IP核来实现PCI从接口,复杂的PCI总线协议就可忽略,仅通过简单的Avalon总线协议就可实现RAM控制器,降低了设计的复杂性,增加系统稳定度。

PCI主接口通过PCI总线与PCI从接口进行数据交换,PCI从接口通过Avalon总线与内部RAM进行数据交换。PCI从接口和内部RAM采用SOPC Builder内部IP核自动生成,PCI从接口工作于32 bit、66 MHz的高速传输状态,理论吞吐量可达264 Mb/s,内部RAM是一个位宽32 bit、深度为2 048的同步RAM。RAM控制器根据Avalon总线状态对RAM进行读写控制。PCI从接口总体设计如图1所示。

图1 PCI从接口总体设计

3Avalon-MM模式突发传输从接口时序

对于Avalon从接口,突发传输主要比基本传输多影响beginbursttransfer、burstcount和readdatavalid 3个信号。在传输开始时,Avalon总线发出一个时钟周期的beginbursttransfer信号表示突发传输开始,并在address上发出有效的首地址,在burstcount上发出突发传输的长度。对address为A、burstcount值为B的突发传输,从接口从地址A开始,执行B个连续的传输,在从接口处理完第B个数据单元之后结束。

Avalon-MM每一次突发传输,从接口只捕获一次地址。突发传输从这个捕获的地址开始,RAM控制器推断出突发传输中所有剩余传输的地址。推断出的地址与从接口是动态地址对齐的,每传输一个数据单元从接口地址增加1。例如,address为0x1000、burstcount值为0x04的写传输,会向从接口地址0x1000、0x1001、0x1002和0x1003传输4个数据单元。

3.1 突发写传输

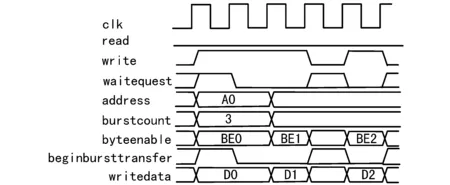

突发写传输在address为A0、burstcount为3时,表示从接口从首地址A0开始,要连续进行3个地址的写传输。写传输在从接口处理完第3个数据单元之后结束。在传输开始时,Avalon总线发出一个时钟周期的beginbursttransfer,在address上发出有效的地址A0,在burstcount上发出突发传输的长度3,在writedata上发出要传输的数据D0、D1和D2,其对应的byteenable为BE0、BE1和BE2。若从外设没准备好可设置waitrequest信号为高,总线会保持write、address、burstcount、beginbursttransfer和writedata不变。突发写传输时序如图2所示。

图2 突发写传输时序

3.2 突发读传输

突发读传输在address为A0、burstcount 为3时,表示从接口从首地址A0开始,要连续进行3个地址的读传输。读传输在从接口处理完第3个数据单元之后结束。在传输开始时,Avalon总线发出一个时钟周期的beginbursttransfer,在address上发出有效的地址A0,在burstcount上发出突发传输的长度3。从外设处理后输出读数据readdata和读有效信号readdatavalid。突发读传输时序如图3所示。

图3 突发读传输时序

4RAM控制器

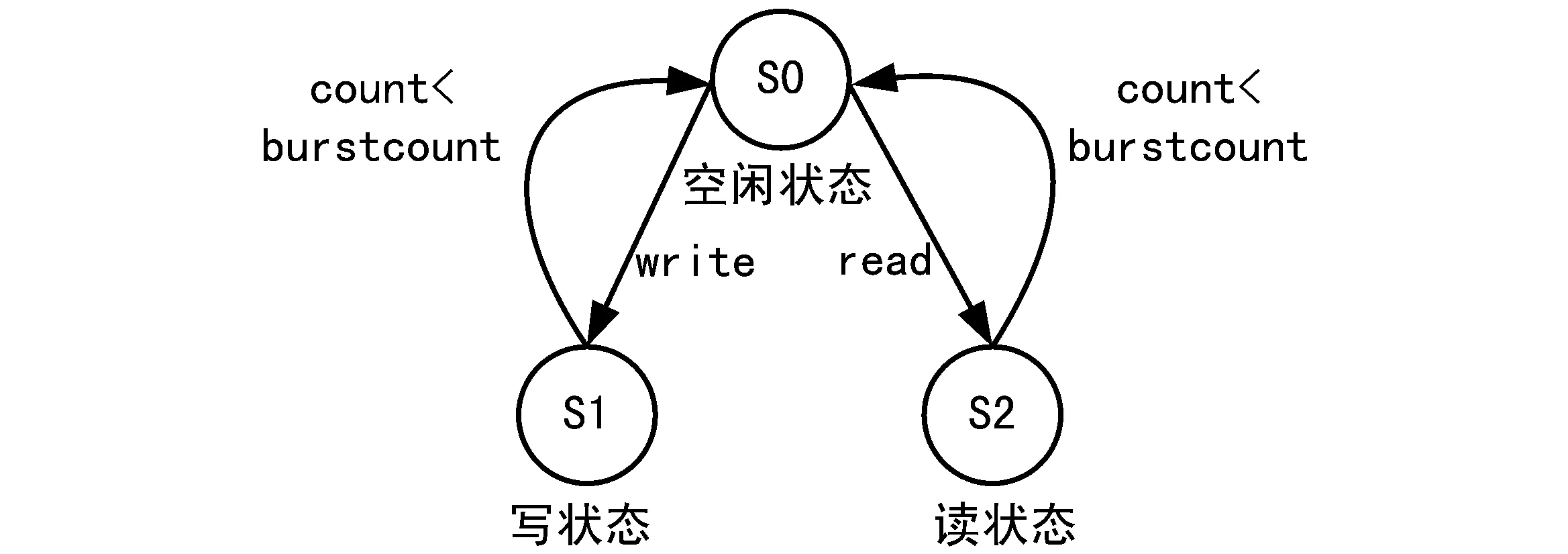

RAM控制器的作用是根据Avalon总线的时序计算出RAM的读写地址,对RAM进行读写控制,辅助完成PCI从接口与内部RAM的数据交换。RAM控制器状态机如图4所示。

图4 RAM控制器状态机

内部RAM可分为S0、S1和S2 3种状态。

S0:空闲状态,等待读写传输的开始。当beginbursttransfer到来后,锁存突发长度burstcount,将首地址address锁存至RAM地址寄存器addresss_a。若write为高,则转入写状态S1;若read为高,则转入读状态S2。

S1:写状态,计算写地址,将数据写入RAM。对写状态进行计数,当count小于burstcount时,write为高,RAM地址addresss_a加1,write为低,addresss保持不变。当count等于burstcount时,转入空闲状态S0。

S2:读状态,计算读地址,将数据从RAM中读出。对读状态进行计数,当count小于burstcount时,RAM地址addresss_a加1,readdatavalid置高。当count等于burstcount时,readdatavalid置低,转入空闲状态S0。

5仿真验证

利用Quartrs II 9.1[11]和SOPC Buider[12]开发工具,将PCI-IP核和RAM控制器综合到FPGA的SOPC系统中。PCI主外设对FPGA上的片内RAM进行读写时,用Signal Tap II对RAM控制器的内部信号进行监测,验证系统的正确性。

PCI主外设写RAM的时序图如图5所示,PCI主外设从首地址0开始将数据35353535h连续写入16个地址,每次的burstcount为8。第1次写时,RAM地址addresss_a从首地址0开始累加,写入0~7地址,写完后转入S0。第2次从8开始累加,写入8~15地址。

图5 PCI主外设写RAM

图6为PCI主外设读RAM的时序图,PCI主外设从首地址0开始顺序读出后续15个地址。一次读写过程即一次Avalon工作周期,就可以读写8个地址的内容,提高了传输效率。

图6 PCI主外设读RAM

2次传输过程之间的空闲时间长短是由外设的特性决定的,改进外设的工作方式可以进一步提高系统的工作效率。

6结束语

设计采用SOPC Buider的方式,基于Avalon-MM突发传输规范,实现了FPGA内的PCI从接口设计,进而实现了PCI主外设与FPGA片上RAM的高速数据交换。通过仿真表明,该设计符合Avalon-MM的突发传输规范,系统传输效率高,性能良好。同时,由于设计具有较高的复用性,后续可将PCI的IP核替换成PCIe、RapidIO等其他接口协议的IP核,无需详细熟悉协议内容即可快速实现其他接口协议,能够有效地减少开发时间并降低开发成本。

参考文献

[1]PCI Local Bus Specification Revision 3.0.PCI Special Interest Group[S],2004.

[2]滑伟.一种PCI总线接口的数据接收卡设计[J].无线电通信技术,2013,39(4):53-55,92.

[3]贺迎芳.基于PCI 总线的高速数据传输技术的设计与实现[D].北京:国防科技大学,2002.

[4]闫福鑫,许志宏.PCI总线从接口的设计与验证[J].计算机技术与发展,2012,22(8):233-236.

[5]PCI Compiler User Guide,Version 9.1[M].ALTERA Corporation,2009.

[6]张丽君.基于IP核的PCI接口FPGA设计实现[J].无线电通信技术,2013,39(1):91-93.

[7]张伟栋,王国庆,崔红利.一种基于IP 内核的PCI 总线接口设计方法研究[J].航空计算技术,2008,38(5):115-118.

[8]杨鑫,徐伟俊.Avalon总线最新接口标准综述[J].中国集成电路,2007,102(11):24-29.

[9]徐宁仪,周祖成.Avalon总线与SOPC系统架构实例[J].半导体技术,2003,28(2):17-20.

[10]孟芳,于立佳,张文志.基于Nios II的SOPC系统设计分析[J].无线电通信技术,2012,38(1):73-76.

[11]罗力凡,常春藤.基于VHDL 的FPGA 开发快速入门·技巧·实例[M].北京:人民邮电出版社,2009.

[12]杨春玲,张辉.现代可编程逻辑器件及SOPC 应用设计[M].哈尔滨:哈尔滨工业大学出版社,2005.

李晓晗女,(1983—),硕士,工程师。主要研究方向:数字通信。

张航男,(1983—),硕士,工程师。主要研究方向:数字通信。

Design of PCI Slave Interface Based on

Avalon-MM Burst Transfer

LI Xiao-han,ZHANG Hang,NI Guang-hua

(The54thResearchInstituteofCETC,ShijiazhuangHebei050081,China)

AbstractThe PCI bus protocol is widely used but complicated,while the Avalon bus specification proposed by Altera can be easily implemented with high performance.A structure of PCI slave interface based on Avalon-MM burst mode is proposed,and the sequences of writing and reading based on Avalon-MM burst transfer are introduced.According to the sequences of Avalon-MM,a RAM controller conforming to sequential specification is implemented,by which the PCI slave interface can achieve high-speed data exchange with RAM.By the PCI slave interface,high-speed data transmission is achieved between the PCI master peripheral equipment and RAM in FPGA.The FPGA verification result shows that the proposed PCI slave interface scheme can satisfy the requirement of Avalon bus specification.

Key wordsAvalon-MM;burst transfer;PCI slave interface;SOPC Builder

作者简介

收稿日期:2015-03-12

中图分类号TP273

文献标识码A

文章编号1003-3106(2015)06-0038-03

doi:10.3969/j.issn.1003-3106.2015.06.11

引用格式:李晓晗,张航,倪光华.基于Avalon-MM突发传输的PCI从接口设计[J].无线电工程,2015,45(6):38-40,48.