一种小体积低功耗的多通道AD模块设计

蔡侃侃(第七一五研究所,杭州,310023)

一种小体积低功耗的多通道AD模块设计

蔡侃侃

(第七一五研究所,杭州,310023)

摘要研究了一种基于可编程逻辑阵列(FPGA)的模数转换方案,在该设计方案中,运用ACTEL公司的小体积FPGA控制AD芯片对信号的采集与传输。该方案具有体积小,功耗低的特点。

关键词FPGA;小体积;低功耗;模数转换

随着模数转换运用的普及,人们对AD转换模块的功耗、精度、同步性能等指标提出了越来越高的要求。其中一种AD转换的电路是运用MCU(微控制器)对AD芯片进行控制[1],但在需要多个AD通道同步采样的应用中,单个MCU对多通道、多片AD芯片做同步数据采集所需处理的信息量较大,存在一定难度。如果增加MCU的数量,则会增加模块的功耗与体积。若用CPLD控制多通道AD数据采集,则采集后的数据整合、暂存、打包等环节所占用的资源需要加入其他硬件才能得以满足[2],增加了电路的复杂程度。FPGA拥有优良的信号并行传输特性与丰富的片上资源,因此在多AD通道同步采集系统中能够表现出良好的性能[3,4]。

1 电路结构与实现方案

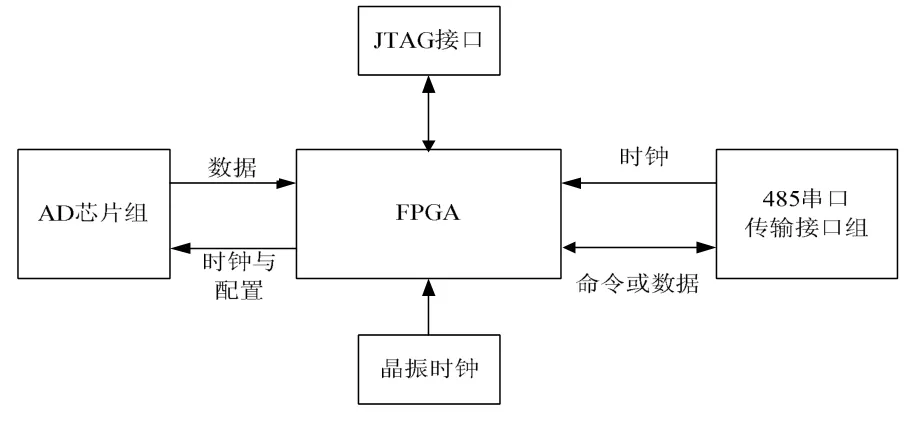

本文所给出的AD模块电路结构图如图1所示。模拟信号通过两片AD芯片做多通道的模数转换,在FPGA的控制下,AD芯片将采集的数据传给FPGA,并在FPGA内部做存储转发,在接收到转发命令之后,FPGA将采集数据通过485传输接口转发出去。

图1 电路结构框图

出于降低功耗和使用面积方面考虑,本方案选用ACTEL厂商的IGLOO系列AGLN125芯片作为该模块的FPGA[5]。它与ALTERA公司的EP3C5以及XILINX的XC3S400A性能对比如表1所示。可以看出,AGLN125芯片在功耗和使用面积方面具有明显的优势。需要指出的是,随着芯片周围环境温度的升高,AGLN125芯片在功耗方面的优势会更为突出。在不要求模块持续工作的场合,AGLN125芯片的睡眠功能可以进一步降低FPGA的功耗,当开启睡眠模式时,FPGA功耗仅为2 μW。此外,本方案选用的FPGA采用FLASH架构,避免了在FPGA外部添加PROM存储芯片,不仅有效减小了该模块的占用面积,而且上电即行,省去了上电时PROM对FPGA的配置过程。

表1 多种FPGA的性能对比

本方案选用的adau1978芯片作为AD转换芯片,采用Σ-Δ架构,可简化前端抗混叠滤波模块[6],单个芯片有4路24位AD转换通道,其与同类型的TI公司模数转换芯片ADS1278以及凌特公司的模数转换芯片LTC2442对比情况如表2所示,ADS1278虽然功耗较低,但是其占用面积太大,在小体积AD转换模块中优势不如ADAU1978,LTC2442不具备数据的同步采集功能,在对同步要求严格的多通道采集系统中不宜使用。

表2 多种模数转换芯片的对比

为将方案的体积与功耗进一步降低,选用SG-310系列32 MHz芯片作为晶振,其占用面积仅为3.2 mm×2.5 mm。当不需要该模块做AD数据采集时,可通过RS-485传输接口传送睡眠命令,则FPGA通过配置各个AD芯片内部寄存器让AD芯片进入睡眠状态以降低模块功耗。整个电路板大小如图2所示,板子长度为60 mm,板宽仅为11 mm。

图2 电路板尺寸示意图

本方案AD芯片的采样频率为10 kHz,上位机运用两路RS-485串口与FPGA进行通信,一路RS-485串口传送时钟,另一路RS-485串口下发命令或上传数据。各个AD转换通道拥有同频同相位的时钟,在接收到AD模块检测采集命令之后的下一个本地时钟上升沿时,使能各路AD通道的同步信号,即可实现各个采集通道的同步。AD采集得到的数据在FPGA内做并串转换,每个通道数据只保留16位,则两片AD的8通道数据一共128位。将这128位数据存入FPGA的片上FIFO中,加上帧头和时标后通过RS-485接口上传。时序图见图3。

图3 本同步采集方案的时序图

2 验证方法

本方案的验证平台结构如图4所示,验证平台按照AD模块的工作流程与传输协议发送命令与时钟,并接收AD模块发送来的数据,将AD采集的数据提取出来通过网口送入PC机,之后数据通过PC机显控软件可直接观测信号波形、幅度、相位等信息。让AD模块各个通道对同一模拟信号进行采集,以某一通道输出数据为基准,若其他各通道输出数据与它具有一致性,则说明该模块工作正常。

图4 验证平台简化结构图

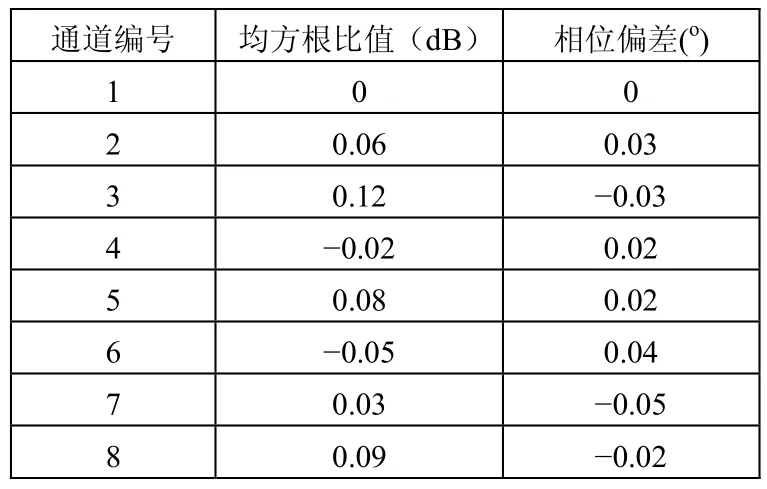

给AD模块的各个通道输入端加入100 Hz的单频正弦波,以第一通道为基准,通过验证平台后各路输出信号信息如表3所示。经测量,当8路AD同时工作时,该模块的需求电流仅为43 mA。

表3 各通道输出信号对比图

3 结论

本文给出多通道AD采集模块设计方案的在验证结果中表现出优良的幅度特性与相位特性,在体积、功耗有特殊要求的场合中拥有良好的运用前景。若改变AD芯片的选型则可衍生出采样率更高或采样精度更好的模数转换设计方案。

参考文献:

[1] 杨剑. 模数转换芯片AD7734与DSP芯片的接口[J]. 测控技术,2005,24(2)71-72.

[2] 祁煜,李启炎,翁良科,等. 基于CPLD和FIFO的多通道高速数据采集系统的研究[J]. 电子工程师,2003,(2): 44-47.

[3] 徐健. 基于DSP的惯性导航系统设计与实现[D].大连理工大学,2006.

[4] 应怀樵. 变幅基多核24位A/D通过FPGA实现高精度、超量程模数转换及数采仪[J].现代振动与噪声技术,2005(6): 52-59.

[5] Microsemi Incorporated. IGLOO nano FPGA Fabric User's Guide [Z]. 2012.

[6] 金旭东. Σ-Δ模数转换在风粉测量中的应用[J]. 微计算机信息,2003,19(9):77-78.