CMOS射频功率放大器高效率和高线性度研究进展

林俊明,郑耀华,张志浩,章国豪

(广东工业大学 信息工程学院,广东 广州 510006)

CMOS射频功率放大器高效率和高线性度研究进展

林俊明,郑耀华,张志浩,章国豪

(广东工业大学 信息工程学院,广东 广州 510006)

CMOS工艺价格低廉且兼容基带工艺,是单片集成电路的理想材料。根据现代无线通信系统所采用的调制方式对功率放大器的性能要求,重点介绍了功率放大器的效率和线性增强技术,比较了相应技术间的优点和缺点,最后阐述包络放大器的发展趋势及其在LTE(4G)的应用。

功率放大器;效率;线性度;LTE;CMOS;包络跟综

0 引言

目前,全球应用于智能手机等便携性移动设备的移动网络急速发展和扩张,且多功能智能手机应用愈加广泛,为满足用户实时通信的用户体验,应用于智能手机的通信系统应该能够更加有效地处理文字、声音和视频数据并实现全球漫游。为了提供高数据速率的大数据传输,现代通信系统(WCDMA/3G/4G/LTE)采用了更加复杂的高频谱效率的调制方式,如OFDM或QPSK和QAM等相移键控和幅移键控相结合的调制方式。为满足不同用户的使用需求,智能手机一般都支持两种或者两种以上网络制式,而随着手机的工作制式不同,其有效的频率带宽不同,因此,作为通信模组之一的功率放大器(PA)应具备多频多模(Multi-band and Multi-mode)的能力。

作为 3GPP(3rd Generation Partnership Project)的演进路线中的主流技术,LTE-Advanced将是 2015年的主流通信方式。LTE的关键技术有多载波和多天线技术,其中多载波技术采用正交频分复用(OFDM)的调制方式,使各个子载波重叠排列,大大提高频谱效率的同时保持了载波之间的正交性,以避免载波之间的干扰。不过,LTE信号在给定的受限的带宽内,有着非常高的峰均比(PAPR),这使 PA常工作在功率回退区,造成 PA的实际效率低下的现象。另外,为了线性放大LTE这类非常包络信号(non-constant envelope signal),要求 PA有着较高的线性度(Linearity),因此,应用于新一代通信系统的功率放大器,必须有着较高的功率效率和线性度,且有着较宽的工作带宽或者是满足多频多模的通信要求。

随着便携设备的功能模块越来越复杂,将各个模块单片集成起来,将大大缩短设备制造商的加工时间,因此,如何减小芯片的有效面积和用廉价的工艺在单一芯片上实现整个射频模组将是未来的研究主流。现代比较流行的集成电路工艺主要有六种:硅 CMOS、BICMOS、Bipolar、GaAs、HBT和 SiGe,但由于硅工艺是最为成熟的,也是成本最低、集成度高和应用最广泛的集成工艺,另外,大多数无线收发机的基带处理部分都使用硅工艺,因此,硅CMOS工艺是单片实现各个模块集成的理想解决方案。不过CMOS工艺自身存在着物理缺陷,如低截止电压(breakdown voltage)、较差的电流能动能力、片上无源器件的Q值小、较大的寄生电容、地衬底电阻率较低、没有较为精确的RF模型和较差的线性度等,这些缺陷都大大限制了CMOS在RFIC领域的应用,而且通信系统对高效率、高线性度和可实现性有着很高的要求,所以目前PA制造商还是常使用价格比较昂贵的 III-V类混合硅半导体工艺器件(Compound Semiconductor Device)[1-4],这些器件通过TWV(Through-Wafer-via)技术提供一个具有良好散热效率的理想环境,常用于Bluetooth、WLAN和GSM/GPRS等应用[5]。不过,CMOS工艺的物理缺陷可以通过一系列技术来缓解,在高供电电压的情况下,可以选择HV CMOS和BCD(Bipolar-CMOS-DMOS)工艺[6]。采用下行键合线(Down-bonding Wires)可以实现在给定的负载下得到较高的输出功率,这种方法的缺点是会减小电压摆幅,不过可以通过引入差分结构克服这个缺点。解决CMOS工艺低截止电压的一个很好的技术是引入共源共栅的 Cascode结构,不过这种结构会使等效的knee电压增加,所以也会在一定程度上减小电压摆幅。CMOS的寄生电容和衬底较低的电阻率,使得在晶体管引脚间的信号存在着耦合,不过这种耦合影响也不全是消极的,通过利用在 Cascode结构中的共栅(CG)晶体管的 RF泄露信号(Leakage signals)提供一个负反馈,不仅可以增强线性度,而且可以减小栅极和漏极间的电压耦合,这种方法最大的一个优点就是不需要额外的器件和芯片面积,而且容易实现。由于CMOS的跨导较低,其电流驱动能力较其他 III-V类半导体低,需要通过级联结构来实现(Cascaded-stage)较大的功率增益,所以,多级级联(multistage cascade topology)是CMOS PA中最常见的一种电路拓扑。虽然采用 Cascode结构和栅氧厚度较厚的晶体管可以减轻CMOS的热载流体效应和低栅氧厚度的低击穿电压的问题,但这并不是最理想的办法。根据最新的研究报告,应用于3G/4G的手持设备的硅工艺PAs的性能已经可以和 III-V类 PAs相比拟[7],另外,类似于III-V类工艺的TWV技术,在SiGe BiCMOS工艺中,TSV(Through-Silicon-Via)技术同样可以为 SiGe BiCMOS工艺提供一个理想的回流地环境和热释放条件,因此,采用TSV技术的 SiGe CMOS工艺将会是PA设计的一个首选方案[8]。

1 PA效率增强技术的关键研究进展

功率放大器是手持移动设备中耗能最大的模块之一,因此为了延长电池的使用寿命和迎合新一代通信(4G/LTE)的要求,高效率是 PA设计的一个很重要而且颇有挑战性的指标。由于传统的PA供电电压是固定的,而且它的最优负载仅仅是当PA输出最大功率时的最优阻抗,对于LTE这种有着高PAPR的调制方式,PA常工作在功率回退区,因此PA的实际工作效率非常低。

提高这类PA效率的关键技术主要有两类:通过一定方法调制负载,使每个功率回退点都对应于一个最优阻抗[9]和通过输出的瞬时功率调制供电电压,从而减小功率回退时的静态功耗。第一种通过调制负载的方法常用于手机等移动设备,第二种方法常常直接通过利用调制信号的包络直接去调制PA的工作电压,从而减小功耗[10]。

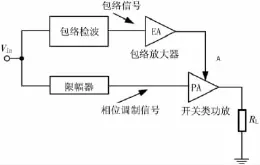

通过直接调制PA的工作电压而达到增强PA效率的技术主要有PM(Polar Modulation)、EER(Envelope Elimination and Restoration)和ET(Envelope Tracking),如图 1所示。PM利用数字信号处理技术(DSP)来产生相位和幅度调制信号[11,12],不过这种方法受限于 DC-DC转换器自身的效率、带宽和面积,并且DC-DC转换模块通常需要使用片外的电感和开关实现,这大大限制了PM在RFIC中的应用。EER和ET是目前PA效率增强的主流技术。EER通过包络检波器和限幅器将输入信号分解成幅度信号和相位信号,因此可以用非线性PA来放大相位信号,而PA的电压则由幅度信号调制,从而可以达到较大的效率,如图2所示,但EER内部固有的非线性导致幅度调制路径和相位调制路径间存在延时[13,14]。

图1 PM调制系统

图2 包络消除与恢复(EER)

与EER不同的是,ET使用线性的PA,如图3所示。因此,ET的最大的一个好处就是没有类似于EER的这种延时失配现象[15],从而使 ET技术可以在增强效率的基础上通过其他技术来取得线性度和效率之间的折中,并可以应用于宽带信号[16]。ET主要目标是为了当输入高PARP信号时,同时在最大输出功率和在功率回退区域获得最大工作效率,且满足高线性度的要求,如EVM和ACLR等。另外,ET技术的效率和线性度依赖于电源调制器(Supply Modulator),如果电源调制效率低下,则ET整体的效率就非常低,因此必须增强电源调制器的线性度,文献[17]通过双开关和前馈信号来增强电源调制器的效率。为了精确跟踪宽带信号并不产生明显失真,需要提高电源调制器的工作带宽[18]。

图3 包络跟踪RFPA系统

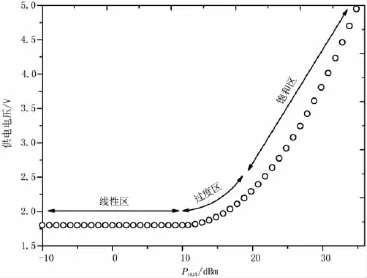

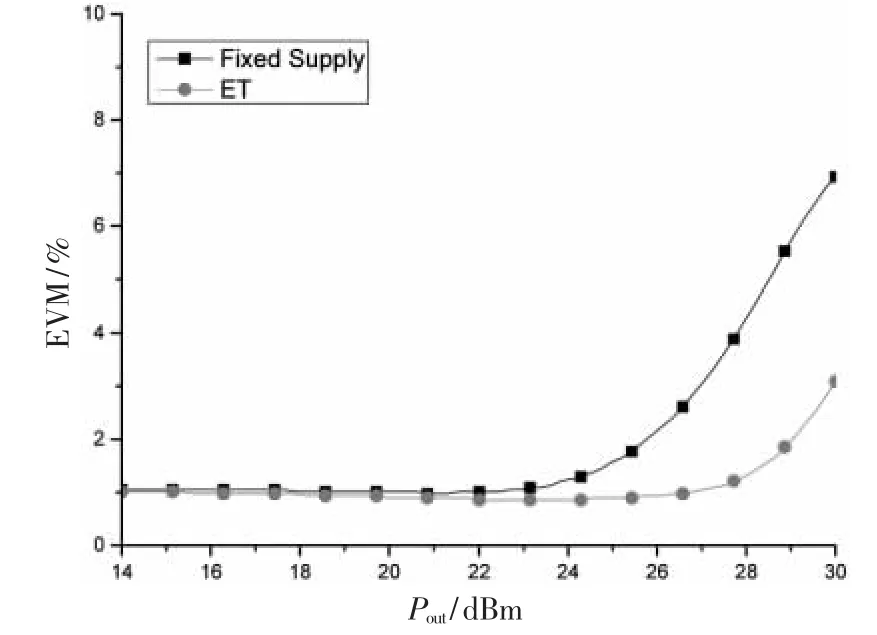

使用ET技术可以大幅度提高功率回退时的效率,如图4所示,为了减小复杂性和提高跟踪精度,电源调制器可以通过开关实现在线性区使PA工作电压保持一个较小的恒定值,而在过渡区和压缩区则通过调制信号的包络来调制PA的工作电压,如图5所示。采用这种方式的ET技术有一个缺点,那就是增益会有所降低,如图6所示,但这种方式较固定电压的方式有着较低的ACLR和EVM,特别是在高输出功率的情况下,如图7和图8所示。

图4 包络跟踪功率放大器的效率示意图

图5 通过开关实现的电压调制示意图

图6 ET方式下输出功率和增益示意图

图7 ET和固定电压下输出功率和ACLR

图8 ET和固定电压方式下输出功率和EVM

ET技术的一个优点是相位调制和幅度调制环路间没有延迟失配,故可以在效率、线性度和带宽间进行折中设计,这些技术都可以归纳为ET的优化技术,其中较为重要的是改善线性度,而包络整形(Envelope-shaping)是改善线性度的一个有效方法[1],其结果可以通过跟踪扫描的点来表示出来[19]。这种方法可以改善工作于 ET方式下的PA性能,包括效率和线性度[20],通过结合其他电路拓扑结构,可以更进一步改善ET PA的效率。文献[21]通过采用伪差分的拓扑结构,结合 SiGe BICMOS的TSV技术实现了一个高效率的ET-PA系统。

改善ET的效率的另一个有效的方法是像传统开关PA一样引入工作在饱和区的功率放大器(Saturated Power Amplifier),这样不仅可以提高 ET PA的输出功率,还可以最大化效率。

为了同时改善PA的动态范围、线性度和效率,可以采用动态反馈控制(Dynamic feedback control)和共源共栅Cascode结构的电路拓扑[22],这种结构中的 CG级采用了自偏置技术,从而改善了线性度和效率。不过这种结构也存在着自身的缺陷,因为CG级的晶体管的非线性会使整体的线性度下降,而且漏-栅间的击穿电压问题将是这种结构的一个瓶颈。这是因为工作于ET PA的CG级在ET PA工作于功率回退区时,由于电源调制器的作用,PA的工作电压会很小,而且Cascode结构的饱和电压相对较高(如 knee电压),使晶体管工作在线性区,从而使ET PA在峰值功率和回退时的功率增益会有着很大的偏差,这就使PA的线性度和动态范围性能下降了[23]。这个问题存在的根本原因是因为 CG级的偏置电压是固定的,因此,可以通过栅极自适应动态偏置技术和 Cascode反馈偏置(Cascode Feedback Bias Technique)技术进行折中设计,反馈偏置技术利用在CMOS工艺下CG晶体管的泄露信号通过负反馈环路反馈到偏置电路,从而改善 CMOS PA的线性度[24],采用共源共栅 Cascode结构的另外一个需要仔细考虑的问题是关于CG级和CS级的尺寸比例,这在一定程度上会影响PA整体的效率[22]。对于 ET技术在多频多模情况下的应用,简单而高效的方法是通过并联一个开关电容从而实现两个模式间的切换,文献[1]通过结合升压电源调制器(Boosted supply modulator)和开关电容实现了一个双模多频带的高效率ET功率放大器,使 ET PA不仅可以工作在高功率模式,还可以工作于低功率模式。

由于多数移动设备可以在多个网络制式间相互切换,因此,对于工作于类似于GSM/EDGE网络制式下的PA,可以采用其他技术来增强效率。如采用反相结构(outphasing architecture)的PA,这种结构最大的优点是可以使用非线性PA,且不需要额外的电源调制器就可以获得较大的效率并不会引起输出电压摆幅下降,最大的缺点就是输出端的求和电路不可避免会存在着功率损耗,因此求和的两条路径间的匹配会影响到整体电路的效率[25]。Doherty PA也是一种能够有效提高功率回退区效率的增强技术,最大的理论效率可以达到79%,并扩展大概 6 dB的线性范围[26],不过,这种技术由于需要采用1/4波长传输线,不仅增加了损耗,还需要占据较大的芯片面积,从而大大限制了其在RFIC的应用。

高电压应用下的效率增强,可以采用传统的开关功率放大器,其中关键问题是片上电源的耦合和反弹[27],一个可行的解决方案是采用两个较宽的开关PA并联代替原来的开关PA,从而避免了开关PA的感性反馈,从而减小了电源耦合[6]。另外,通过采用压电器件(Piezoelectric Device),可以使PA输出几十瓦的功率并且有着很高的集成度,这种压电器件有着很好的噪声控制[28],又因压电反应可以等效为一个压电电容,因此并不会增加电路分析的复杂度。

2 高线性PA的关键技术研究进展

当PA工作于高效率区时,PA将会因本身的非线性而出现功率压缩,从而减小了PA的功率增益,而当PA工作于功率回退区时,PA的实际工作效率非常低,这将会消耗大部分电能,因此,PA的线性化目的是改善PA的整体线性度,且使整体的效率比功率回退时的效率高。PA的线性体现为两个方面:AM-AM和AM-PM失真。而衡量PA的线性度和偏离程度的指标,应该根据系统的要求和调制方式来决定。PA常用的线性度指标有ACPR、EVM、1 dB压缩输出功率和三阶交调点,在工程上常用单音(single tone)和双音信号(two tone)对 PA分别进行谐波和交调失真等非线性测量与分析。此时,ACPR代表频谱带外的失真,而EVM代表带内失真。由于双音信号会对相邻信道造成干扰,所以对于某一信道,都有一个频谱限制(spectral mask)。

改善PA的线性度的一个常用方法是通过反相的非线性补偿电路来抵消原来电路的非线性[29-31],这些电路通过补偿AM-AM或者是AM-PM失真来达到优化线性度的目的,然而,2-D电路综合技术(2DCST),利用电流-电压转换器和可调的压控电容(Voltage Characteristic Capacitor)实现同时补偿AM-AM和AM-PM失真,且不需要反相电路[32]。虽然这些技术可以比较有效地改善PA的线性度,不过这些技术需要额外的控制单元,如电流-电压转换器等,从而限制了其在RFIC方面的广泛应用。

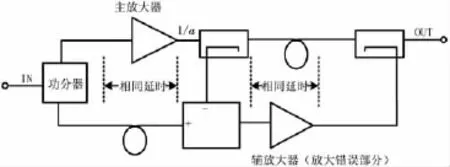

反馈是改善PA线性度的另外一种有效的方法,而且可以改善带宽,不过前提是牺牲了增益。前馈技术(Feed Forward)广泛应用于高稳定性要求的 PA设计中,主要通过前馈错误环路获得原始信号的错误信号,然后将放大后的信号与错误信号相减,从而得到线性的信号,如图9所示。如果其内部的两级PA是稳定的,则整体的PA就是非常稳定的,然而前馈技术的如下几个缺陷使其在RFIC中的应用极其有限:

(1)如果延时单元由无源器件组成,则会增大PA整体的损耗,如果由有源器件组成,则会因为无源器件的非线性造成失真;

(2)输出级的减法器间的损耗,大大降低了 PA的整体效率;

(3)整PA线性度的改善决定于每个减法器的信号的增益和相位匹配。

图9 前馈技术示意图

采用 Cartesian负反馈技术(Cartesian Feedback)[33]可以克服前馈技术的以上缺点,因为Cartesian Feedback不需要使用减法器,如图10所示,并且对环路间的失配不敏感,与Cartesian Feedback技术相似的还有极化环路反馈技术(Polar Loop Feedback)[34],这两种技术有着相反的特性,不过都对负载和PVT的变化不敏感,而较大的缺点就是环路的带宽受限,文献[33]通过牺牲较大的输出功率而实现带宽超过10 MHz的PA。与改善效率的方法一样,同样可以通过在Cascode结构中结合反馈和自适应偏置技术来改善线性度[35]。

将RF输出信号直接反馈到输入端,虽然可以获得较大的带宽,但在RF频率上容易造成PA不稳定,从而产生振荡,虽然文献[36]通过结合偏置技术改善了这种情况,但其所采用的方法仅仅适用于驱动级。为了克服直接负反馈在 RF频率下不稳定的缺点,文献[37]通过直接检测输入和输出端的信号相位和幅度,采用双路闭环负反馈结构。这种方法又称功率反馈(Power Feedback),这种结构通过消除AM-AM失真的方法来实现输出较大的功率而没有群延时失真[38],不过这种方法得益于III-V类工艺的优点,因此并不适用于CMOS工艺,因为CMOS工艺本身的线性度较差,且其非线性的栅极电容会造成较大的AM-AM和AM-PM失真。

采用预失真技术(Pre-distortion)也是一种比较可行的线性PA结构,不过这种结构得益于预先可估计的失真模型,从而构建与之相反的模型电路来达到失真补偿的目的。如果PA的非线性特性随工艺、温度和负载阻抗变化时,预失真技术并不是理想的解决方案,因为很难去同时构建一个全方面的失真模型。

图 10 Cartesian反馈示意图

3 总结

随着移动设备的功能越来越复杂,集成度越来越高,单片实现RF前端模组有着重要的研究意义,又因为RF的基带处理单元基本都使用硅工艺,与之兼容的硅CMOS工艺是很好的解决方案。虽然CMOS工艺因为物理缺陷在性能上比不上 III-V类工艺,但是随着研究的深入,通过结合其他优化技术,使用CMOS实现RF的一些重要模块已经成为可能。

随着新一代网络(4G/LTE)的应用和逐渐普及,移动通信的数据空前增长,移动设备对电池续航时间的要求也大大提升。LTE上行链路信号采用SC-FDMA调制方式,均峰比明显高于W-CDMA。PA作为移动终端中耗能最大的模块之一,LTE上行链路信号的功率电平大部分时间都保持在较低值,极少达到峰值功率,因此,PA大部分时间工作在功率回退区,从而消耗电池电能,进而影响设备的散热设计功耗(TDP)。

包络跟踪(ET)技术根据PA的输入信号的包络动态调整PA的工作电压,使PA在回退时也有着较高的效率,且 ET内部有着固有的线性特性,使 ET PA很容易在线性度、效率和带宽之间的进行折中设计,所以ET是应用于LTE环境的一个较好的解决方案。

非线性是PA处理类似于LTE这些高PAPR信号的另外一个问题,因为随着输入信号功率的加大,PA会因为内部的非线性而出现功率增益压缩,从而无法线性放大输入信号而出现失真,最终导致ACLR和EVM超标。PA的线性度的改善可以采用反馈和数字预失真的方法,不过采用预失真的方法需要提供一个比较完善的失真模型,而反馈则会使增益下降。随着DSP技术的成熟,数字预失真技术也逐渐成为ET PA的主流线性优化技术。

[1]YUNSUNG C,DAEHYUN K,JOOSEUNG K,et al.A dual power-mode multi-band power amplifier with envelope tracking for handset applications[J].IEEE Transactions on Microwave Theory and Techniques,2013,61(4):1608-1619.

[2]KANG D,DAEKYU Y,KYOUNGJOON M,et al.A highly efficient and linear class-AB/F power amplifier for multimode operation[J].IEEE Transactions on Microwave Theory and Techniques,2008,56(1):77-87.

[3]YU Z,METZGER A G,ZAMPARDI P J,et al.Linearity improvement of HBT-based Doherty power amplifiers based on a simple analytical model[J].IEEE Transactions on Microwave Theory and Techniques,2006,54(12):4479-4488.

[4]YOUNGOO Y,CHOI K,WELLER K P.DC boosting effect of active bias circuits and its optimization for class-AB InGaP-GaAs HBT power amplifiers[J].IEEE Transactions on Microwave Theory and Techniques,2004,52(5):1455-1463.

[5]CHOWDHURY D,HULL C D,DEGANI O B,et al.A fully integrated dual-mode highly linear 2.4 GHz CMOS power amplifier for 4G WiMax applications[J].IEEE Journal of Solid-State Circuits,2009,44(12):3393-3402.

[6]Haifeng M,van der Zee R,Nauta B.Design and analysis of a high-efficiency high-voltage class-D power output stage[J]. IEEE Journal of Solid-State Circuits,2014,49(7):1514-1524.

[7]KRISHNAMURTHY V,HERSHBERGER K,EPLETT B,et al.SiGe power amplifier ICs for 4G(WIMAX and LTE) mobile and nomadic applications[C].Radio Frequency Integrated Circuits Symposium(RFIC),2010 IEEE;2010 23-25 May 2010.

[8]RUILI W,LOPEZ J,YAN L,et al.A highly efficient 1-Watt broadband class-J SiGe power amplifier at 700 MHz[C]. Silicon Monolithic Integrated Circuits in RF Systems(SiRF),2012 IEEE 12th Topical Meeting on;2012 16-18 Jan. 2012.

[9]JOONGJIN N,JIN-HO S,KIM B.A handset power amplifier with high efficiency at a low level using load-modulation technique[J].IEEE Transactions on Microwave Theory and Techniques,2005,53(8):2639-2644.

[10]YAN L,LOPEZ J,PO-HSING W,et al.A SiGe envelopetracking power amplifier with an integrated CMOS envelope modulator for mobile WiMAX/3GPP LTE transmitters[J]. IEEE Transactions on Microwave Theory and Techniques,2011,59(10):2525-2536.

[11]NAKATANI T,RODE J,KIMBALL D F,et al.Digitallycontrolled polar transmitter using a Watt-Class currentmode class-D CMOS power amplifier and guanella reverse balun for handset applications[J].IEEE Journal of Solid-State Circuits,2012,47(5):1104-1112.

[12]KAHN L R.Single-sideband transmission by envelope elimination and restoration[J].Proceedings of the IRE,1952,40(7):803-806.

[13]REYNAERT P,STEYAERT M S J.A 1.75-GHz polar modulated CMOS RF power amplifier for GSM-EDGE[J]. IEEE Journal of Solid-State Circuits,2005,40(12):2598-2608.

[14]WALLING J S,TAYLOR S S,ALLSTOT D J.A class-G supply modulator and class-E PA in 130 nm CMOS[J]. IEEE Journal of Solid-State Circuits,2009,44(9):2339-2347.

[15]WING-YEE C,BAKKALOGLU B,KIAEI S.A 10 MHz bandwidth,2 mV ripple PA regulator for CDMA transmitters[J].IEEE Journal of Solid-State Circuits,2008,43 (12):2809-2819.

[16]LOPEZ J,YAN L,POPP J D,et al.Design of highly efficient wideband RF polar transmitters using the envelopetracking technique[J].IEEE Journal of Solid-State Circuits,2009,44(9):2276-2294.

[17]CHIN H,ANDING Z,YAN J J,et al.Digitally assisted dual-switch high-efficiency envelope amplifier for envelope-tracking base-station power amplifiers[J].IEEE Transactions on Microwave Theory and Techniques,2011,59(11):2943-2952.

[18]YAN J J,CHIN H,KIMBALL D F,et al.Design of a 4-W envelope tracking power amplifier with more than one octave carrier bandwidth[J].IEEE Journal of Solid-State Circuits,2012,47(10):2298-2308.

[19]DONGSU K,KANG D,JINSUNG C,et al.Optimization for envelope shaped operation of envelope tracking power amplifier[J].IEEE Transactions on Microwave Theory and Techniques,2011,59(7):1787-1795.

[20]HASSAN M,LARSON L E,LEUNG V W,et al.A wideband CMOS/GaAs HBT envelope tracking power amplifier for 4G LTE mobile terminal applications[J].IEEE Transactions on Microwave Theory and Techniques,2012,60 (5):1321-1330.

[21]Ruili W,Yen-Ting L,Lopez J,et al.High-efficiency silicon-based envelope-tracking power amplifier design with envelope shaping for broadband wireless applications[J]. IEEE Journal of Solid-State Circuits,2013,48(9):2030-2040.

[22]SANGSU J,KYUNGHOON M,BYUNGJOON P,et al. CMOS saturated power amplifier with dynamic auxiliary circuits for optimized envelope tracking[J].IEEE Transactions on Microwave Theory and Techniques,2014,62(12):3425-3435.

[23]SANGSU J,KYUNGHOON M,BYUNGJOON P,et al. Dynamic feedback and biasing for a linear CMOS power amplifier with envelope tracking[C].Microwave Symposium (IMS),2014 IEEE MTT-S International;2014 1-6 June 2014.

[24]Hamhee J,Kun-Seok L,Ockgoo L,et al.A cascode feedback bias technique for linear CMOS power amplifiers in a multistage cascode topology[J].IEEE Transactions on Microwave Theory and Techniques,2013,61(2):890-901.

[25]HONGTAO X,PALASKAS Y,RAVI A,et al.A flip-chippackaged 25.3 dBm Class-D outphasing power amplifier in 32 nm CMOS for WLAN application[J].IEEE Journal of Solid-State Circuits,2011,46(7):1596-1605.

[26]RAZAVI B.RF Microelectronics[M].USA:Hall PTR,1998.

[27]TOMBAK A,BAETEN R J,JORGENSON J D,et al.Integration of a cellular handset power amplifier and a DC/DC converter in a Silicon-On-Insulator(SOI)technology[C]. Radio Frequency Integrated Circuits Symposium,2008.

[28]WALLENHAUER C,GOTTLIEB B,ZEICHFUSL R,et al. Efficiency-improved high-voltage analog power amplifier for driving piezoelectric actuators[J].IEEE Transactions on Circuits and Systems I:Regular Papers,2010,57(1):291-298.

[29]BARRIE G.The multi-tanh principle:a tutorial overview[J]. IEEE Journal of Solid-State Circuits,1998,33(1):2-17.

[30]KIMURA K.The ultra-multi-tanh technique for bipolar linear transconductance amplifiers[J].IEEE Transactions on Circuits and Systems I:Fundamental Theory and Applications,1997,44(4):288-302.

[31]WEBSTER D R,HAIGH D G,PARKER A E,et al.Novel circuit synthesis technique using short channel GaAs FETs giving reduced intermodulation distortion[C].Circuits and Systems,1995 ISCAS′95,1995.

[32]MIAOFU D,GARD K G,STEER M B.A highly linear and efficient CMOS RF power amplifier with a 2-D circuitsynthesis technique[J].IEEE Transactions on Microwave Theory and Techniques,2012,60(9):2851-2862.

[33]ISHIHARA H,HOSOYA M,OTAKA S,et al.A 10 MHz signal bandwidth cartesian-loop transmitter capable of offchip PA linearization[C].Solid-State Circuits Conference Digest of Technical Papers(ISSCC),2010.

[34]PULLELA R,TADJPOUR S,ROZENBLIT D,et al.An integrated closed-loop polar transmitter with saturation prevention and low-IF receiver for quad-band GPRS/ EDGE[C].Solid-State Circuits Conference-Digest of Technical Papers,2009.

[35]SANGSU J,BYUNGJOON P,KYUNGHOON M,et al. Linearization of CMOS cascode power amplifiers through adaptive bias control[J].IEEE Transactions on Microwave Theory and Techniques,2013,61(12):4534-4543.

[36]HAMHEE J,Kun-Seok L,OCKGOO L,et al.A 40% PAE linear CMOS power amplifier with feedback bias technique for WCDMA applications[C].Radio Frequency Integrated Circuits Symposium(RFIC),2010.

[37]KOUSAI S,ONIZUKA K,YAMAGUCHI T,et al.A 28.3 mW PA-Closed loop for linearity and efficiency improvement integrated in a+27.1 dBm WCDMA CMOS power amplifier[J].IEEE Journal of Solid-State Circuits,2012,47 (12):2964-2973.

[38]BO S,SUNDSTRO X M L.Design and implementation of a CMOS power feedback linearization IC for RF power amplifiers[C].Circuits and Systems,1999 ISCAS′99 Proceedings of the 1999 IEEE International Symposium on,1999.

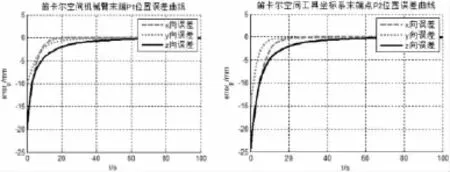

图5 三维笛卡尔空间的机械臂运动轨迹

图6 笛卡尔空间机械臂位置误差曲线

5 结论

本文采用仿人智能控制理论解决了无标定视觉伺服控制的问题,采用了多模态视觉控制器来进行运动空间的定位,并且通过仿真平台验证了该理论的正确性。

但本文的视觉伺服控制器只对机械臂在像平面上的运动进行了规划,并未考虑到笛卡尔空间的运动轨迹,存在机械臂笛卡尔空间的运动不是最优路径的问题,仍需做进一步改进。

参考文献

[1]蔡自兴.机器人学[M].北京:清华大学出版社,2000:46-54.

[2]张何栋.面向机器人的视觉伺服控制器设计[D].杭州:浙江工业大学,2014.

[3]丁建华.机器人视觉伺服控制方法的设计与研究[D].杭州:浙江工业大学,2013,3

[4]刘鹏玉.服务机器人手眼协调仿生控制研究[D].上海:上海大学,2012.

[5]陈众.基于仿人智能控制理论的 UPFC智能控制器结构设计研究[D].重庆:重庆大学,2003.

[6]邓萌.自主机器人全局定位系统的研究与应用[D].重庆:重庆大学,2007.

[7]CUPERTINO F,GIORDANO V,MININNO E,et al.A neural visual servoing in uncalibrated environments for robotic manipulators[C].Systems,Man and Cybernetics,2004 IEEE International Conference on.IEEE,2004,6:5362-5367.

(收稿日期:2015-08-23)

作者简介:

龚飞(1989-),男,硕士研究生,主要研究方向:机器视觉。

谢明(1963-),男,硕士生导师,主要研究方向:智能汽车,智能机器人,机器人视觉,人工智能。

王梦佳(1990-),女,硕士研究生,主要研究方向:嵌入式。

Survey of high efficiency and linearity of CMOS power amplifiers

Lin Junming,Zheng Yaohua,Zhang Zhihao,Zhang Guohao

(School of Information Engineering,Guangdong University of Technology,Guangzhou 510006,China)

CMOS process is the ideal solution for monolithic integrated circuit in terms of low cost and compatibility for baseband circuitries.Based upon the requirements applied for specific modulation scheme of modern communication systems,the purpose of this paper is to present the state of the art of the techniques of which the benefits and drawbacks are compared,to enhance the efficiency and linearity of power amplifiers(PAs).In addition,the developing trend of enveloping tracking power amplifiers(ET PAs) applied for LTE applications is presented.

power amplifier;efficiency;linearity;LTE;CMOS;envelope tracking

TN722.7+5;TN323+.4

A

10.16157/j.issn.0258-7998.2015.11.005

林俊明,郑耀华,张志浩,等.CMOS射频功率放大器高效率和高线性度研究进展[J].电子技术应用,2015,41 (11):17-23.

英文引用格式:Lin Junming,Zheng Yaohua,Zhang Zhihao,et al.Survey of high efficiency and linearity of CMOS power amplifiers[J]. Application of Electronic Technique,2015,41(11):17-23.

2015-06-03)

林俊明(1991-),男,硕士研究生,主要研究方向:射频、微波及毫米波单片集成电路及组件等方面的产品研究。

郑耀华(1988-),男,硕士研究生,主要研究方向:微波理论、现代微波天线的关键技术以及射频功率放大器射频的产品研究。

张志浩(1989-),男,博士研究生,主要研究方向:SOI CMOS射频功率放大器与仿真以及超高频射频开关技术。