基于PXI架构的高速数据采集系统设计

黄 宇 ,柏正尧 ,董 亮 ,2,侯观庆 ,陆 宗

(1.云南大学 信息学院,昆明 650091;2.中国科学院云南天文台,昆明 650011)

传统数据采集系统的硬件设计长期存在以下难以避及的问题:庞大的硬件设计工作量但仅有很少的一部分与实际应用相关;更换核心芯片后需要对部分外围电路进行重新设计所体现出较差的系统扩展性;长期存在于ADC采样率、主控FPGA处理能力以及主板总线数据传输率之间的兼容性以及硬件驱动的编写等。为解决上述问题,NI公司在模块化仪器的基础之上提出了一种将虚拟仪器技术与Xilinx FPGA技术相结合的技术方案。值得一提的是,该技术方案为数据采集系统提供了一种快速的图形化设计方法,大大提升了开发效率。考虑到较高的数据生成率,本文所设计的数据采集系统采用时间交替采样算法并利用具有较高数据传输率的PXI架构进行硬件搭建以及通过读取FIFO待写入元素数量进行数据拥塞的相关控制。所设计的高速数据采集系统可以实现频率在0~900 MHz、功率在-70~0 dBm范围内信号的高精度测量以及频率在0.9~1.5 GHz、功率在-40~0 dBm范围内信号相对有限精度下的工程测量。

1 系统硬件结构设计

本文所设计的高速数据采集系统是基于PXI所构建的,主要实现射频前端高速的同步数据采集、数据上传以及PC端相应的信号处理等功能。该系统硬件平台主要包括下位机和上位机2个部分,其中下位机以NI PXI机箱为主构架,主要完成高速ADC同步采样模块、与之相匹配的FPGA主控模块等NI FlexRIO设备的控制、协调以及同PC的数据交互工作[1];上位机由PC承担,主要完成采集信号的存储以及相应的高速信号处理工作。该系统硬件结构如图1所示。

图1 高速数据采集系统硬件结构框图Fig.1 Block diagram of the data acquisition system hardware structure

2 系统软件程序设计

系统软件设计在LabVIEW环境下使用图形化编程语言进行,主要分为下位机和上位机2个部分。下位机的功能由PXI架构的NI FlexRIO设备承担,对主控FPGA模块进行编程来配置高速信号同步采集及匹配速率上传;上位机的功能由PC承担,主要完成采集信号的存储及相应的信号处理工作。

2.1 下位机FPGA主控模块程序设计

FPGA模块的主要功能是通过对高速ADC采样模块I/O资源的配置及上传速率的控制来达到频率在0~900 MHz、功率在-70~0 dBm范围内信号的高精度测量及0.9~1.5 GHz、-40~0 dBm范围内信号相对有限精度下测量的预定性能指标。该模块软件部分共分为配置循环、采样循环及数据上传循环3个部分,通过LabVIEW FPGA Module对FPGA进行图形化编程及相关部署,大大提升系统开发效率。

2.1.1 配置循环

参考FPGA模块的技术文档,此循环通过对User Command、User Data 0&Data 1等信号的参数配置来完成上位机对高速采样ADC模块的配置,此举使得ADC模块能够根据实际的工程所需及时做出相应的改变。

2.1.2 采样循环

鉴于NI 5771高速ADC同步采样模块配备有双通道采样,为达到更高的采样率,本系统考虑采用文献[2]中提出的时间交替采样算法TIS(time-interleaved sampling)。

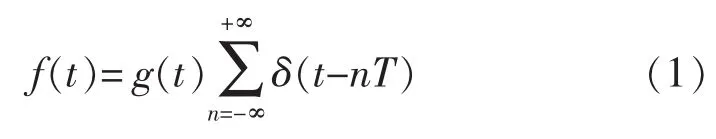

时间交替采样可简述为采用同一采样时钟的N个并行ADC对1个模拟输入信号g(t)进行采样,采样间隔设为T,则单片AD采集的序列为

若相邻使得各ADC以固定的时间差依次对同一模拟信号进行采样,将N片ADC所采样的数字输出按相同顺序进行拼接,此举提升了模拟信号一个周期内的采样点数,从而实现了N倍于单片ADC的采样率[3],理想情况下时间交替采样的数学模型为

然而TIS算法在传统高速数据采集系统的硬件实现上存在通道失配、时延误差及增益误差等难以避及的问题,这些误差很大程度上影响系统的性能指标。本设计的ADC采样模块中所采用的2块相同型号的芯片经过了通道校正,PXI架构中有用于多版同步的触发总线、参考时钟和服务于精确定时的星形触发总线,此硬件结构十分有利于TIS算法的低误差实现[4]。

ADC采样模块NI 5771有2个通道,每个通道有8个端子,可将每个通道的前4个端子即AI 1 N-7~N-4&AI 0 N-7~N-4 组成一个通道,AI 1 N-3~N&AI 0 N-3~N组成另一个通道,这样新形成的2个通道之间自然存在2π/2=π相位差,进而完成时间交替采样在ADC模块的配置以倍乘采样率。其图形化编程如图2所示。

本系统包括微信公众号客户端和管理后台两部分。微信公众号客户端采用PHP语言开发;管理后台采用B/S模式搭建,开发工具选用Visual Studio 2015,兼容IE 7.0以上所有版本浏览器;数据库选用SQL Server 2008 R2。

图2 时间交替采样的图形化编程Fig.2 Configuration of time-interleaved sampling

新形成的2个通道工作于NI 5771 CLIP所定义的采样时钟187.5 MHz下,两通道通过按名称捆绑这一模块将各自的数字输出进行拼接形成U128类型的数据,进而达到倍乘采样率的目的。

考虑到高采样率伴随着高数据生成率,本系统3.0 GS/s的采样率,8 bit量化,每秒生成3.0 GB庞大的数据量,纵使采用适用于高速数据传输的PXI架构和DMA(直接内存访问)技术也很难满足需求。鉴于本系统对实时性要求不高及设备成本等因素,所选用的PXI机箱NI 1073的x1 PCI总线用于数据传输的带宽仅为208 MB/s,因而控制采样数据以合适的速率上传是FPGA模块的主要任务之一。

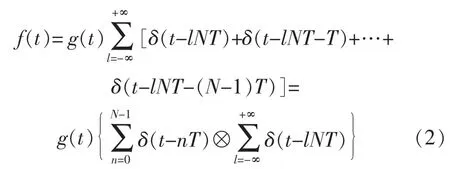

采样数据的触发与上传是由空闲、等待触发、采样和暂停这4个状态控制,这4个状态之间的切换如图3所示。

图3 采样循环控制状态切换框图Fig.3 Switching of the sampling loop control states

采样数据以匹配速率上传的核心在于数据缓冲区可写入元素数量的判断,当数据缓冲区无法存储一次采样所生成的数据量时,即可中断前端ADC的采样以避免数据溢出。当数据缓冲区可容纳至少一次采样所生成的数据量时,再次开启前端ADC的采样,往复循环即可实现采样数据的匹配速率上传。本设计采用块内存定义的FIFO来实现DMA方式的数据上传,使用FIFO方法节点来判断数据缓冲区的可写入元素数量。

2.1.3 数据上传循环

考虑到从PXI机箱NI 1073上传到PC的最大带宽仅能达到208 MB/s,最适合传输的数据类型为U64,故而对从采样循环所接收的数据进行一定的处理,从而以相匹配的数据类型、传输速率进行上传[1]。在本循环中,配置上传时钟为25 MHz,将从采样循环所接收的U128类型数据解捆绑形成适合上传的U64类型数据进行乒乓上传即可。

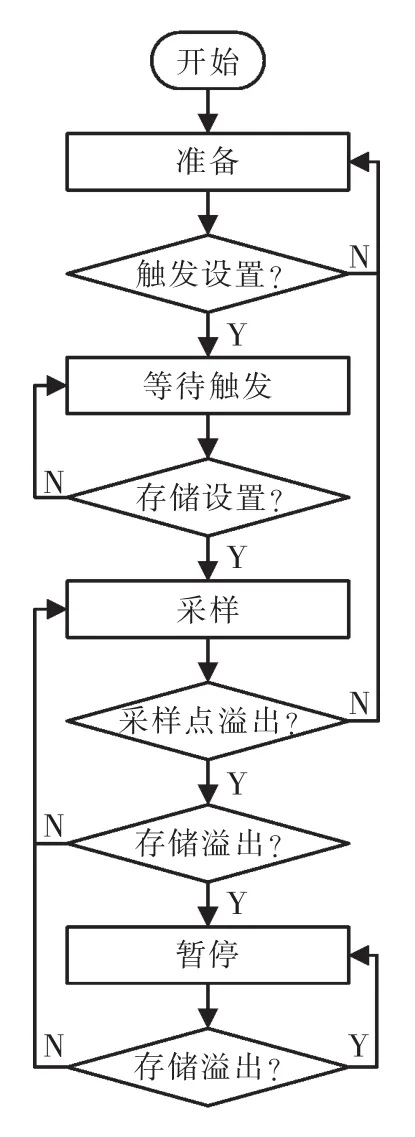

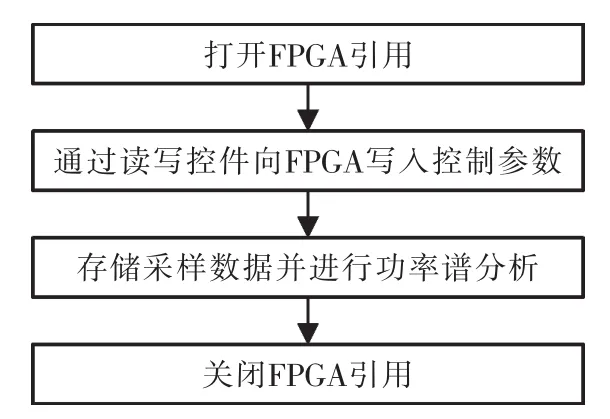

2.2 上位机程序设计

上位机的主要功能由PC机所承担,其程序在LabVIEW环境下搭建[5],程序框图如图4所示。

图4 上位机程序框图Fig.4 Block diagram of the host computer structure

3 系统性能分析

考虑到采样点数及噪底功率等因素,将本系统的采样点数设置为20480,频率分辨率可达到45.8 kHz,下面从信号测量及误差分析2个方面对所设计的高速率数据采集系统进行性能分析。

3.1 信号测量性能分析

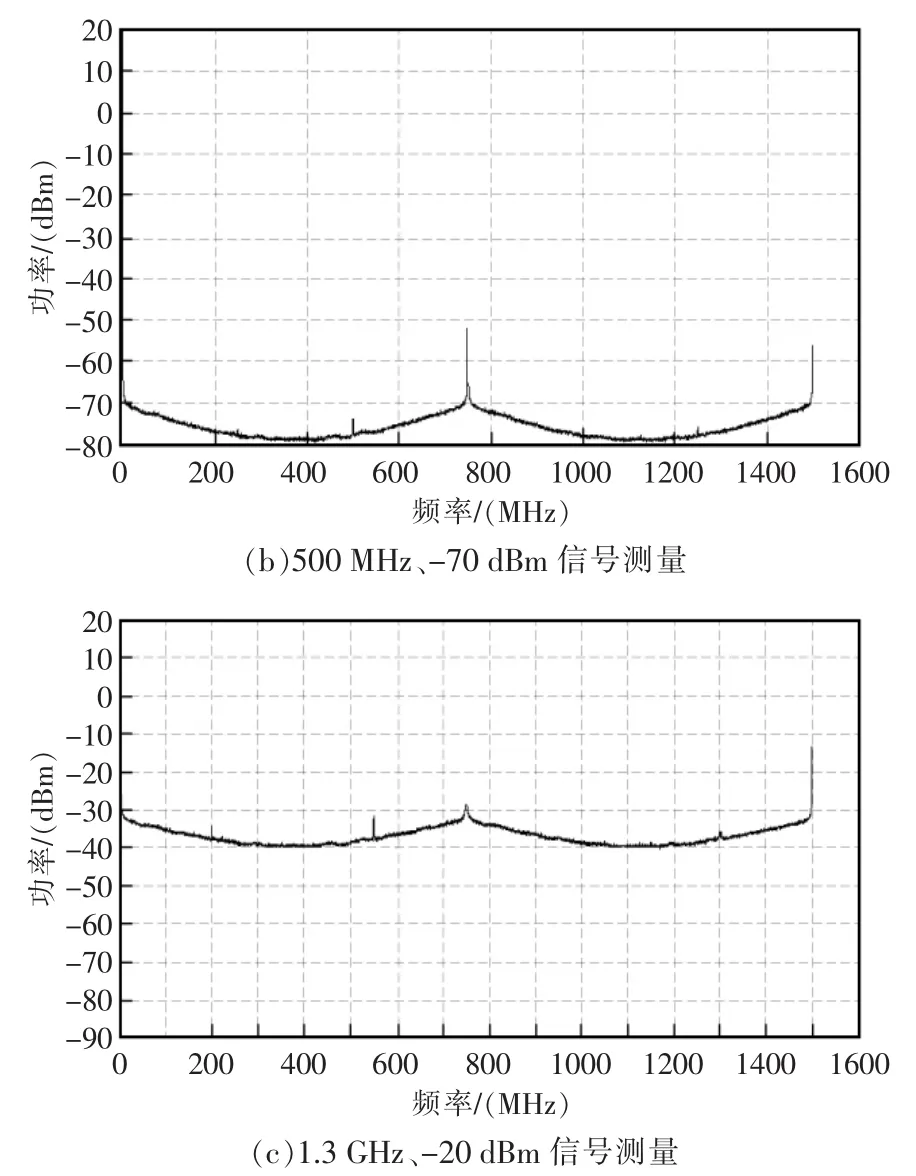

本系统对噪声,500 MHz、-70 dBm的信号以及1.3 GHz、-20 dBm的信号进行测量,结果如图5所示。

图5 使用所设计高速数据采集系统进行信号测量的测试结果Fig.5 Measurement of signals used the system designed

图5(a)为没有外部输入仅有噪声时的功率谱,750 MHz为系统分频所产生的串扰信号,说明该系统可对0~1.5 GHz的信号进行测量,噪底功率最低下探至-82~-76 dBm;图(b)为外部输入为 500 MHz、-70 dBm时的功率谱,说明该系统可对该信号进行较高精度的测量;图(c)为外部输入为1.3 GHz、-20 dBm时的功率谱,由于ADC模块内嵌有3dB带宽为900 MHz的网格滤波器,故而在对频率在900 MHz以上信号的测量只能满足有限的工程应用。

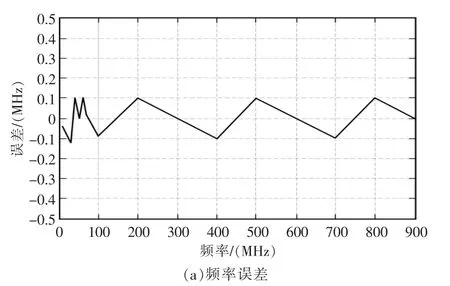

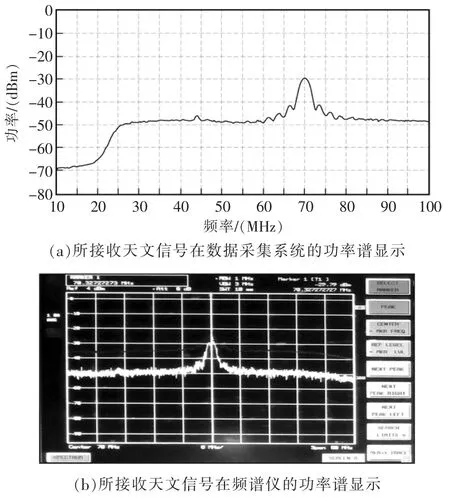

3.2 系统误差分析

鉴于高速ADC模块中集成有1个3 dB带宽为900 MHz的网格滤波器,故此处只对频率处于0~900MHz信号的测量进行误差分析,结果如图6所示。

图6 0~900 MHz信号的频率、功率测量误差图Fig.6 Error of frequency&power measured within 900MHz

图6说明0~900 MHz信号的频率测量误差处于-0.1~0.1 MHz区间内,以300 MHz信号为例的功率测量误差处于-1~1 dBm区间内。

由此得出,本系统可实现0~900 MHz信号的高精度测量及0.9~1.5 GHz信号测量的有限工程应用。

4 系统实际工程测试

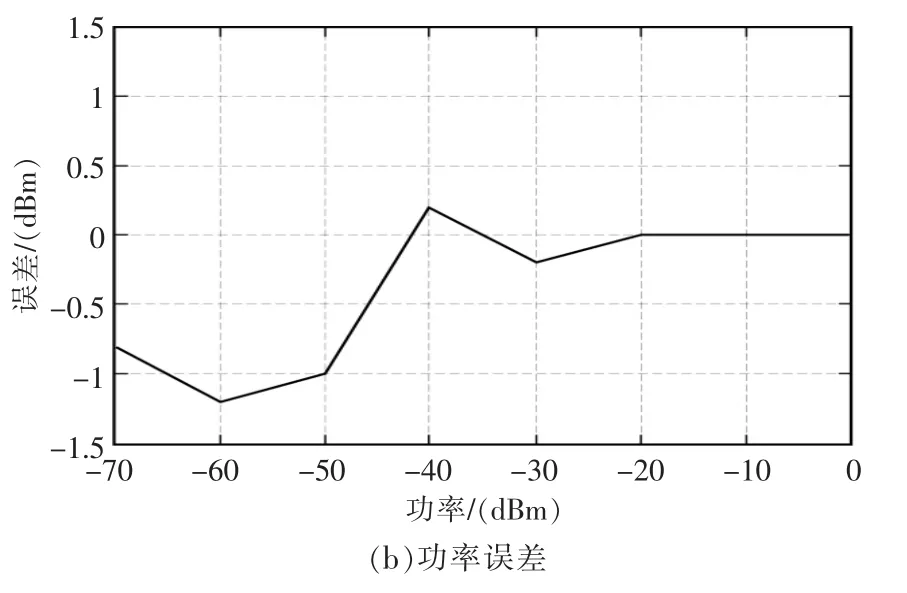

系统设计、搭建完成后,在中科院云南天文台得以实地工程测试。在测试过程中,将本系统及1台频谱仪通过1个二功分连接到40 m射电望远镜上以形成实验对照,所接收天文信号的功率谱如图7所示。

图7 所接收天文信号的功率谱Fig.7 Power spectrum displayed on the system designed and the spectrum analyzer

图7(b)表明,频谱仪接收的天文信号频率为70.32 MHz、功率为-29.79 dBm,与此同时所设计的高速数据采集系统的功率谱中可检测出与前者频率、功率极为相近的信号,可认为两者为同一信号,进而验证了所设计数据采集系统功能的正确性。

5 结语

本文采用PXI架构搭建高速数据采集系统,在下位机通过主控FPGA模块来完成时间交替采样算法在ADC采样模块的相关配置以达到倍乘采样率的目的,与此同时FPGA模块控制采样数据的上传速率以协调高数据生成率和低传输带宽之间的矛盾;在上位机实现数据存储及功率谱的快速计算。本系统的软件设计均在LabVIEW环境下使用图形化编程语言完成,此举大大加速了系统的开发效率。本系统可实现频率在0~900 MHz、功率在-70~0dBm范围内信号的高精度测量以及频率在0.9~1.5 GHz、功率在-40~0 dBm范围内信号的有限精度测量。该系统在云南天文台得以实际应用于工程测试,测试结果验证了所设计高速数据采集系统的功能正确性。

[1]李攀.阵列信号同步采集系统的设计与实现[D].武汉:华中科技大学,2013.

[2]W C Black Jr,D A Hodges.Time-interleaved converter array[J].IEEE Journal of Solid-state Circuits,1980,15(6):1022-1030.

[3]黄炳国,张在琛.超高速1bit采样系统的硬件设计及仿真[J].电子测量与仪器学报,2009(S1):269-273.

[4]易敏,苏淑靖,季伟,等.基于FPGA的高速时间交替采样系统[J].电子技术应用,2015,41(1):71-74.

[5]章佳荣,王璨,赵国宇.精通LabVIEW虚拟仪器程序设计与案例实现[M].北京:北京人民邮电出版社,2013.