基于FPGA的天线选通电路设计

王传刚,栾宝宽,董茂林

(1.海军航空工程学院 青岛校区,山东 青岛 266041;2.西安电子科技大学 电子工程学院,陕西 西安 710071)

某定向设备采用多普勒效应测向原理,即当天线振子做圆周运动时,天线振子本身与目标信号源就会产生相对速度,使振子感应到的信号产生了多普勒频移,通过对振子感应信号相位的处理,从而达到测向的目的。而为了提高天线系统的可靠性、稳定性以及数据处理的可行性,采取的措施是利用脉冲电信号依次打通天线8根振子,通过取样的步进方式代替振子的机械圆周旋转,因此设计一个稳定可靠的天线选通电路就成为了系统的首要目标。传统的方式一般都是采用数字集成块电路实现,一方面需要的集成块较多,电路板较大;二是容易受到外界的影响,脉冲的相位对准相对较难。为了解决以上问题,本文采用FPGA技术,对此电路进行了重新设计,并在电路设计过程中利用Quartus II软件对设计电路进行了功能的模拟仿真,提高了电路设计的可靠性,简化了电路设计与调试的难度,缩短了开发周期,有效的降低了开发成本,提高了设备生产、升级换代的效率。

1 电路设计

1.1 设计思想

本电路采用典型的自顶向下(Top-Down)设计结构。就是从系统总体要求出发,在顶层进行功能结构的划分和设计,在方框图一级进行仿真与纠错,并用硬件语言对高层次的系统行为进行描述,在系统一级进行验证。这样以来,有利于早期发现结构设计中的失误,避免设计浪费,同时减少了逻辑功能的仿真量,提高了设计的一次性成功率。

具体到本电路的设计,由于信号源采用的是规格为1 224 kHz晶振,所要得到的打通天线振子的脉冲信号是8路有效电平依次到达的脉冲信号,即要求8路脉冲信号的相位依次严格对应。最后对低电平有效的打通脉冲进行反向驱动放大,从而得到我们所需要的天线打通脉冲,控制天线振子依次导通,实现多普勒效应测向。结合以上对电路功能的基本分析,利用自顶向下结构对电路进行设计,从输入输出信号关系看,需要由频率高的信号得到信号较低的信号,因此,首先需要对信号进行分频,同时由于信号源产生的是1路脉冲信号,而要得到的是8路打通信号,所以电路还要包括一个8分路的功能电路,具体可以采用计数、译码器来实现。

通过以上的分析,将电路整体功能分步、分模块实现,首先进行分频,将晶体振荡器信号进行分频,初步得到一路1.36 kHz方波信号,然后再将此一路方波信号分成8路170 Hz打通脉冲信号,并使8路脉冲信号的有效电平依次出现,严格对准,保证在同一时间内只且只有一根振子被打通,从而满足系统的要求,综上所述,本电路中要包含分频模块、计数模块和译码模块(分路)以及外围电路。

1.2 硬件电路原理示意图

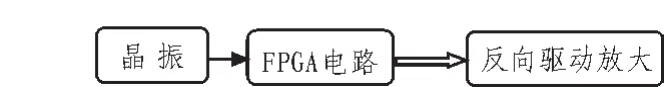

根据设计思想中对电路设计的分析,信号源和反向驱动放大电路为外围电路,中间对信号的处理通过FPGA来实现,具体示意图如图1所示。

图1 天线选通电路原理示意图Fig.1 Antenna selecting circuit schematic diagram

1.3 FPGA电路的VHDL编程实现与分析

本文中电路采用了典型的Top-Down设计结构,也就是将电路分解成几个相对独立的功能模块,通过VHDL编程实现后,生成独立的元件,然后在TOP结构下调用生成的功能模块或库中已有的模块,完成所要设计的电路,从而满足电路功能的要求。因此电路可以分解成了分频模块和计数译码模块(8分路)两大独立的设计单元,具体实现如下。

1.3.1 分频模块

设备中信号源频率为1 224 kHz,因此要得到1.36kHz信号,就是对信号进行900分频。通过VHDL语言可以直接实现900分频,并得到占空比为1:1的分频信号,但此方案过程中计数值较大,不利于电路实现,因此本文中采用多级分频电路串联的方式来实现,即采用三级分频电路,第一级实现9分频(输出信号占空可以为1:1,也可以不是),后两级采用10分频(输出信号占空比1:1),避免了单个过程计数过大的缺点,同时也满足系统设计的需要。其中9分频具体程序(占空比不是1:1)如下:

源代码:

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY div_9 IS

PORT(clk:IN STD_LOGIC;

clk_out:OUT STD_LOGIC);

END div_9;

ARCHITECTURE rtl OF div_9 IS

SIGNAL clk_temp:STD_LOGIC;

BEGIN PROCESS(clk)

VARIABLE counter:INTEGER RANGE 0 TO 15;

BEGIN IF(clk'EVENTAND clk='1')

THEN IF (counter=8)THEN counter:=0; clk_out<='1';

ELSE counter:=counter+1;clk_out<='0';

END IF;

END IF;

END PROCESS;

END rtl;

以上是9分频模块的源代码,输出信号占空比不是1:1,但不影响后面对信号的处理。在10分频模块中采用输出占空比为1:1的方式,具体实现代码如下。

源代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY div_10 IS

PORT(clk:IN STD_LOGIC;

clk_out:OUT STD_LOGIC);

END div_10;

ARCHITECTURE rtl OF div_10 IS

SIGNAL clk_temp:STD_LOGIC;

BEGIN PROCESS(clk)

VARIABLE counter:INTEGER RANGE 0 TO 15;

CONSTANT md:INTEGER:=4;

BEGIN IF(clk'EVENT AND clk='1')

THEN IF(counter=md)THEN counter:=0;

clk_temp<=NOT clk_temp;

ELSE counter:=counter+1;

END IF;END IF;

END PROCESS;

clk_out<=clk_temp;

END rtl;

1.3.2 计数译码模块

要将1.36 kHz方波信号转换成8路170 Hz的打通脉冲信号,可以通过计数和译码来实现。具体模块设计为采用三位输出的计数器和3-8译码器。其中VHDL源程序可以引用现成的标准源代码来实现,也可以根据实际情况自行编写,比较简单,这里不再罗列。同时对于计数、译码这样的通用模块,可以在Top结构中直接从库中调用。

2 电路的功能仿真及结果

2.1 电路功能仿真

本电路的设计采用了Quartus II软件进行功能仿真。Quartus II是Altera提供的现场可编程门阵列 (FPGA)和复杂可编程逻辑器件(CPLD)开发综合环境。Quatus II支持Altera的IP核,包含了LPM/MegaFunetion宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性,加快了设计速度。此外,Quartus II通过和 DSP Builder工具与Matlab/Simulink相结合,可以方便地实现各种DSP应用系统。其支持Altera的片上可编程系统开发,集系统级设计、嵌入式软件开发、可编程逻辑设计于一体,是一种综合性的开发平台,适用于实际电路的设计与仿真,可以大大缩短电路开发的周期,提高设计的效率。

在分层电路设计中,Quartus II可以采用两种结构。第一种结构就是每个模块分别建立一个工程文件,在每个工程中分别调试单元电路,调试通过后,生成器件,然后再TOP中调用元件即可;另一种就是所有模块文件统一放在一个工程文件中,每个模块调试时设置成置顶即可,相互之间没有影响,然后生成器件在Top文件中进行调用。本文电路的设计与仿真采用了第二种方法,统一放置在一个工程文件中,便于文件的管理,提高了设计与仿真过程的效率。

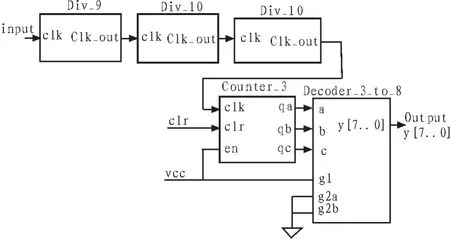

对于TOP-Down结构,顶层设计有两种输入方式,一种是采用VHDL语言编程,利用例化语句将各个组成模块进行逻辑连接,从而实现电路功能;另一种方式就是采用电路图输入方式,分别调用库中已有或编程生成的器件,最终实现电路设计实现。本文设计电路采用原理图输入的方式,在Top结构中最后形成的电路原理图如图2所示。

图2 天线选通电路电路图Fig.2 Antenna selecting circuit diagram

2.2 仿真结果与分析

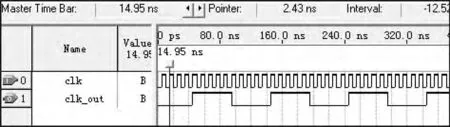

2.2.1 分频模块仿真结果

本电路中共有3级分频电路,采用串联方式连接,分别为一级9分频和两级10分频,需要得到占空比为1:1的信号,因此10分频电路输出必须为占空比为1:1的方波信号,单10分频模块仿真结果如图3所示,能够得到占空比1:1的方波信号,满足了电路的设计要求。

图3 10分频模块仿真结果Fig.3 Simulation result of ten frequency division module

2.2.2 选通电路仿真结果

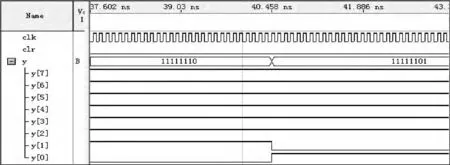

从上文中可以知道,设计天线选通电路的目的就是产生8路天线打通脉冲,且有效脉冲应该是依次出现的,每一时刻有且仅有一路信号是有效的,同时还应按照顺序依次有效。本设计总体电路功能仿真结果如图4所示。从仿真结果中可以看出,在输入一路时钟(CLK)信号的情况下,8路输出端中每一时刻仅有1位为0,也就是1位有效,且为0的位是按顺序依次出现的,因此电路设计输出结果满足系统对电路的要求,同时也说明电路设计是成功的。

图4 天线选通电路仿真结果Fig.4 Simulation result of the antenna selecting circuit

3 结论

本文采用VHDL语言的层次化和模块化的设计方法,对系统的逻辑行为进行描述,然后通过综合工具进行结构的综合、编译、仿真,可在短时间内设计出高效、稳定、符合要求的电路系统,而且在不变化顶层文件的情况下即可任意升级、完善模块电路。硬件描述语言VHDL为设计提供了更大的可移植性和可扩展性,使程序具有更高的通用性,较好的达到了系统对本电路的要求。同时,基于VHDL语言的FPGA技术是近年来新兴技术,功能强大,速度快,应用领域光,在军事、医疗、通信、视频技术等领域都得到了广泛的应用。虽然目前利用FPGA成本偏高,但是随着产量的增加和应用的进一步拓展,成本必将进一步降低。因此,本文中电路设计采用了FPGA技术,符合设备未来发展需求,为将来设备的升级换代提供了必要保障。

[1]侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计(修订版)[M].西安:西安电子科技大学出版社,1999.

[2]Mark Zwolinski.VHDL数字系统设计[M].李仁发,等译.2版.北京:电子工业出版社,2007.

[3]丁文祥.数字革命与竞争国际化[N].中国青年报,2001-11-20.

[4]周润景,图雅.基于Quartus II的FPGA/CPLD数字系统设计实例[M].北京:电子工业出版社,2007.

[5]Stadtmiller,D.J.电子学项目设计与管理[M].施惠琼,译.北京:清华大学出版社,2011.

[6]阎石,王红.数字电子技术基础[M].5版.北京:搞定教育出版社,2010.