模拟器中基于Slave FIFO模式USB数传系统设计

王海滨,刘宝华,解传军,孔 挺

(海军航空兵学院 辽宁 葫芦岛 125001)

在现代科研、实验、教学、训练中,模拟器起着重要作用,它是一种由计算机实时控制、多系统协调工作、能模拟作战环境的模拟设备[1]。利用模拟器进行训练不仅不受天气等自然条件的制约,而且没有各类保障以及训练安全等因素的限制,相较于利用实装训练而言具有很多优势,国内外许多单位为了保证训练任务的圆满完成,均针对不同训练需求研制了各种不同种类和规模的训练模拟器,并取得良好的训练效益。

在模拟器的设计中,有些情况下需要大量的信息能够快速有效地在模拟器的各个模块之间进行高速传递,也就是说需要一定的通信接口协议来实现大量数据的高速交互[2]。在模拟器设计中,很多情况下需要使用USB总线作为连接PC机与模拟器中功能模块的数据通道。USB(通用串行总线)总线是英特尔、微软、BM、康柏等公司在1994年联合制定的一种通用串行总线规范,它是一种广泛应用于各类计算机的标准接口,具有可扩展性强、支持热插拔、传输速率高等优点,特别适用于有大量数据实时传输要求的场合[3]。USB2.0支持三种速率,低速 1.5Mbit/s,全速 12Mbit/s,高速 480Mbit/s。本文旨在研究一种用于模拟器的高速USB传输模块,并且要使系统具有传输速率高、可扩展性强的特点。本文研究的内容主要是结合USB2.0的Slave FIFO方式,给出了一种适合模拟器通信的设计方案,主要分为硬件系统设计和软件系统设计两大部分内容,系统硬件设计研究了基于Cypress公司的CY7C68013A与ALTERA公司EP1C6Q240的硬件设计方法,系统软件设计主要介绍了同步Slave FIFO模式的FPGA编程实现方法以及CY7C68013A的固件程序设计。

1 系统硬件设计

在系统硬件设计中,选用ALTERA公司EP1C6Q240 FPGA作为核心处理器。选用Cypress公司的CY7C68013A作为上位机和FPGA中间的接口芯片。Cypress公司的EZ-USB FX2LP是世界上第一款集成USB2.0高速协议的芯片,它集成了1个USB数据收发器、1个SIE(串行接口引擎)、1个增强型的8051微控制器、8.5kB RAM、4kB FIFO和可编程的外围接口[4]。选用FPGA作为处理器,能够在速度和体积上有更好的适应性,可以增强模拟器通信接口设计的灵活性和可扩展性。FPGA选用ALTERA公司的EP1C6Q240,EP1C6Q240是ALTERA公司的一款高性价比的属于CYCLONE系列的FPGA,采用0.13 μm工艺技术,工作电压为 3.3 V,内核电压为 1.5 V,有 5 980 个 LEs,MK4 RAM 块(128×36bits)的数量为20个,总的RAM空间共计92 160Bit,最大用户I/O为185个,内嵌2个锁相环电路,可实时处理USB高速传输的数据,完全可以满足系统需求。

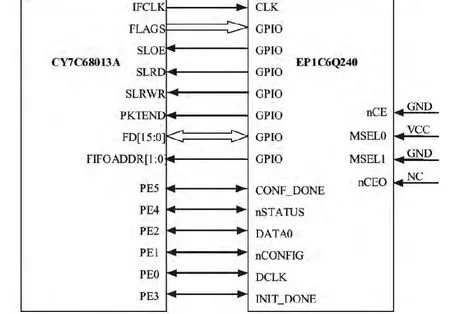

系统硬件设计采用“CY7C68013A+EP1C6Q240”的架构,当有一个与FX2芯片相连的外部逻辑只需要利用FX2做为一个USB 2.0接口而实现与主机的高速通讯,而它本身又能够提供满足Slave FIFO要求的传输时序,可以做为Slave FIFO主控制器时,即可考虑用Slave FIFO传输方式。Slave FIFO传输示意图如图1所示。

图1 Slave FIFO传输示意图Fig.1 Transport schematic diagram for Slave FIFO

在Slave FIFO模式下,CY7C68013A固件的功能是配置Slave FIFO相关的寄存器以及控制FX2何时工作在此种模式下。当8051固件将相关的寄存器配置完毕,同时使其工作在Slave FIFO模式之后,FPGA即可按照Slave FIFO的传输时序,高速与主机进行数据通讯,8051固件可不参与数据的传输。

系统设计中CY7C68013A是USB2.0的纽带,在CY7C68013A的前端放置LC6-2SC6芯片,然后LC6-2SC6芯片再与上位机USB接口相连接。FPGA程序加载方式通常可以采用JTAG方式和AS方式,系统硬件设计中,对于FPGA的配置方式采用PS模式进行加载,要完成FPGA的配置就需要将CY7C68013A的GPIO与EP1C6Q240的PS加载线进行连接,具体接口连接如图2所示。

图2 Slave FIFO总线与PS配置接口连接图Fig.2 The interface diagram of Slave FIFO BUS and PS configuration

2 系统软件设计

在系统软件设计中主要研究基于同步Slave FIFO模式的高速USB通道数据传输。CY7C68013A有3种工作模式,本系统中通过固件初始化使其工作在同步Slave FIFO模式下。当CY7C68013A工作在同步Slave FIFO方式下时,则需要由外部控制器控制[5]。Slave FIFO是从机方式,即FX的CPU不直接参与USB数据处理,而是简单地把FX作为USB和外部数据处理逻辑之间的通道。FX2在数据传输中主要利用了4kB的FIFO,其中端点2、4是输出端点,端点6、8是输入端点。数据在其内部传输控制是通过full(满)和empty(空)两个控制信号来完成的,当full为真时不能再写,当empty为真时,则不能再对FIFO进行读。在模拟器的USB数传系统设计中,采用FPGA作为主控制器,由FPGA提供CY7C68013A的SLOE、SLRD和SLWR等信号,可以方便产生Slave FIFO时序所需逻辑,因此选择Slave FIFO方式构建高速数据传输通道。Slave FIFO包括同步Slave FIFO和异步Slave FIFO两者模式,相比较而言,同步模式传输速率更高,在模拟器中需要实时传输高速数据的情况下选择了同步Slave FIFO模式进行设计。

2.1 CY7C68013A固件程序设计

为了实现同步Slave FIFO模式数据传输,需要对CY7C68013A进行固件程序设计。USB固件是运行在CY7C68013A中的代码。可以采用两种方法将USB固件下载到FX2的RAM中,一种是通过将固件存储于片外EEPROM中,上电固件自行加载;另一种就是编写能自动完成固件下载以及设备重枚举功能的设备驱动程序。考虑到模拟器通信数据接口的可扩展性,设计中采用了第二种方法。Cypress公司提供的固件编程框架为简化固件编程提供了有利条件,可在其基础上进行完善修改。固件程序采用Keil C51 uVision2编写,主要包括 fifo.c、FW.C、DSCR.A51、Ezusb.lib、USBJmpTb.OBJ等文件[6],其中fifo.c为外围设备控制文件,主要进行USB功能设备的初始化以及用户函数挂钩的相关定义,在此文件中的void TD_Init(void)函数主要功能是完成FX2的初始化,主要是初始化各个端口以及各端口的先入先出缓冲区。对于选择Slave FIFO的工作方式、工作频率、时钟源及同步方式都可以通过设置IFCONFIG寄存器的值来实现[7]。

2.2 FPGA对同步Slave FIFO的读写逻辑设计

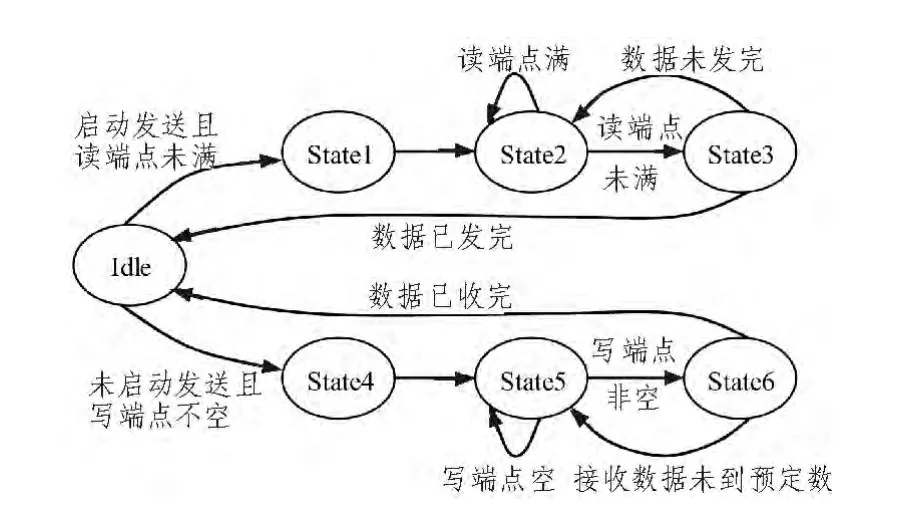

为了实现同步Slave FIFO模式数据传输,还需要编写FPGA程序实现对同步Slave FIFO的读写逻辑。通过构造有限状态机来实现FPGA对于同步Slave FIFO的读写逻辑。根据模拟器通信数据传输的实际情况,本文设计了一种状态机来实现同步Slave FIFO的批量读写任务,图3为状态机设计图,Idle、State1、State 2、State 3 构成同步 Slave FIFO 写逻辑,Idle、State 4、State 5、State 6 则构成同步 Slave FIFO 读逻辑。

图3 FPGA同步Slave FIFO读写状态机Fig.3 Reading and writing FPGA state machine for synchronous Slave FIFO

2.2.1 同步Slave FIFO写

Idle:当有写事件发生时,从Idle转到State1。

State1:指向 IN FIFO,设置 FIFOADR[1:0],进入 State2。

State2:判断如 FIFO满标志“真”,则在State2等待,否则转到State3。

State3:将驱动数据发送到数据线上,激活SLWR使之有效,持续一个IFCLK,如数据未发完,则进入State2,否则进入Idle。

2.2.2 同步Slave FIFO读

Idle:当有读事件发生时,从Idle转到State4。

State4:指向 OUT FIFO,设置 FIFOADR[1:0],进入 State5。

State 5:激活SLOE使之有效,判断如FIFO空标志“真”,则在State5等待,否则转到State6。

State 6:从数据线上读取数据,激活SLRD使之有效,持续一个IFCLK,如接收数据未到预定数量,则进入State 5,否则进入Idle。

2.3 EP1C6Q240固件文件生成

ALTERA公司FPGA芯片有3种配置下载方式,分别是AS方式(主动配置)、PS方式(被动配置)和JTAG配置方式。不同下载方式,其硬件连接方式不用。AS下载方式,程序烧写到FPGA的配置芯片内,在上电后,FPGA芯片直接从配置芯片读写程序配置到FPGA,然后运行。JTAG下载方式,程序烧写到FPGA芯片内RAM中,JTAG下载完成后直接运行,但是FPGA芯片内的程序掉电后无法保存,一般用于调试程序时使用。JTAG接口是一种业界标准,主要是用于芯片测试等功能。PS方式则是由外部计算机或控制器控制配置过程。而在本系统设计中,考虑到模拟器的可重构性、功能扩展和升级,首先建立USB控制端点通信管道,然后在此基础上在线传输FPGA固件,对于FPGA加载采用PS模式。

在Quartus II环境中对FPGA进行开发,但QuartusⅡ编译生成的SOF格式的配置文件不能直接用于PS模式下配置FPGA,需要进行数据转换才能得到可用的配置数据。在QuartusⅡ中的开发工具可以生成多种配置文件,有数据转换选项,可以将.SOF格式文件转换为.rbf格式文件。Quartus II提供了转换工具,转换方法为点击Quartus II软件File菜单,选择Convert Programming Files子菜单,其中Programming file type中选择rbf文件格式,Mode选项选择1-bit passive serial,即PS模式,在input files to convert列表中添加需要转换的SOF文件,最后点击generate,则在指定位置生成rbf文件。FPGA芯片型号决定了rbf格式配置文件的大小,必须注意配置文件长度的差异。EP1C6系列FPGA[8-9]生成的rbf文件为145 902字节,而EP1C12系列FPGA生成的rbf文件为290 405字节。

3 结束语

文中重点研究了一种应用于模拟器中的基于同步Slave FIFO模式的高速USB数据传输设计方法,相较于其他设计方法,采用FPGA作为系统的主控制器,可降低成本,能够在速度和体积上有更好的适应性,可以增强模拟器通信接口设计的灵活性和可扩展性。在系统软件设计中研究了CY7C68013A固件程序设计、FPGA对同步Slave FIFO的读写逻辑设计以及EP1C6Q240固件文件生成方法。采用PS加载模式的优点是无需用户额外操作即可实现固件的自动升级和加载运行,大大提高了系统功能的可扩展性。经实际测试,本文设计的同步Slave FIFO数据传输系统,在上位机数据传输程序充分优化的情况下,采用48 MHz时钟、16 Bit位宽Slave FIFO总线,高速USB通道数据传输速率可达40 MB/s,并且可以有效稳定传输,已经接近USB2.0极限速率。

[1]黄安祥.现代军机先进仿真技术与工程设计[M].北京:国防工业出版社,2006.

[2]徐强,顾宏斌,高振兴.飞行模拟器座舱仪表通信技术研究[J].信息技术,2012(1):1-4.XU Qiang,GU Hong-bin,GAO Zhen-xing.Researchon communication technology of the cockpit instrument in flight simulator[J].Information Technology,2012(1):1-4.

[3]薛圆圆.USB应用开发技术大全[M].北京:人民邮电出版社,2006.

[4]张俊涛,王豫莹.基于FPGA和USB2.0的高速数据采集系统[J].仪表技术与传感器,2011(10):46-48.ZHANG Jun-tao,WANG Yu-ying.High-speed data acquisition system based on FPGA and USB2.0[J].Instrument Technique and Sensor,2011(10):46-48.

[5]赵乐森,王旭柱.基于FPGA与USB2.0的实时数据采集与处理系统[J].微型机与应用,2011,30(17):25-27.ZHAO Le-sen,WANG Xu-zhu.Real-time data acquisition and processing system based on FPGA and USB2.0[J].Microcomputer&Its Applications,2011,30(17):25-27.

[6]Cypress CY7C68013A Datasheet[EB/OL].[2013-03].http://www.cypress.com.

[7]Cypress EZ-USB Manual Technical Reference[EB/OL].[2013-03].http://www.cypress.com.

[8]崔智军,刘昭元,张瑜.基于FPGA的简易触摸电子琴设计[J].现代电子技术,2014(22):114-116.CUI Zhi-jun,LIU Zhao-yuan,ZHANG Yu.Design of simple touch electronic piano based on FPGA[J].Modern Electronics Technique,2014(22):114-116.

[9]张冬阳,薄振桐.基于FPGA与USB 2.0接口的红外图像采集系统设计[J].电子科技,2014(11):48-51.ZHANG Dong-yang,BO Zhen-tong.Infrared image acquisition system based on FPGA and USB 2.0 interface[J].Electronic Science and Technology,2014(11):48-51.