基于FPGA的直流无刷电机控制器的设计与实现

佛山华芯微特科技有限公司 陈炳成

基于FPGA的直流无刷电机控制器的设计与实现

佛山华芯微特科技有限公司 陈炳成

传统的直流无刷电机速度控制是通过MCU软件编程实现,其响应速度不快,占用资源较多,且难以快速实现复杂算法控制。本文提出一个基于FPGA的六步直流无刷电机速度控制的硬件实现方案,该方案利用硬件对直流无刷电机进行控制,能够快速灵活地实现直流无刷电机的启停、加速、减速、正反转、刹车、转速检测等动作,同时编写的直流无刷电机控制器IP核能够进行移植和复用,作为SOC芯片的功能模块。直流无刷电机控制器采用Verilog HDL语言进行编写,IP核在Modelsim 6.5g上通过功能仿真,并且在XUPV5-LX110T FPGA开发板上通过硬件测试,实现结果表明方案的可行性。

FPGA;直流无刷电机控制;六步;Verilog

1 引言

随着当前能源的日益短缺,节能减排已成为我国的一个基本国策,降低生活和工业能耗也成为所有人共同努力的目标。直流无刷电机因其扭矩转速特性好、动态响应快、高效能等优点,逐渐被社会大众所接受,并广泛应用于日常生活用具、白色家电、汽车工业、航空、消费电子、医学电子、工业自动化装置和仪表等领域。

2 六步BLDCM控制器设计

2.1 BLDCM控制器概述

设计的有霍尔六步BLDCM控制器包括三部分:光电编码器信号处理模块AB4F、PWM脉宽调制模块PWM_CTRL以及直流无刷电机换相控制模块BLDCM_CTRL。工作原理为:电机光电编码器的输出信号A、B和Z经过光电编码器信号处理模块的处理,得到电机的转向信号DIR、AB的四倍频脉冲以及电机的转速;电机霍尔传感器的输出信号U、V、W以及得到的电机转向值DIR输入到电机换相控制模块,得到电机的换相序列;电机的换相序列和PWM脉宽调制模块输出的与速度相关的脉冲信号进行结合处理,最终输出控制3相功率开关的6个PWM控制信号。

2.2 光电编码器信号处理模块原理

模块对光电编码器两相输出A、B信号进行4倍频及电机转向提取,并计算倍频脉冲值及电机实时转速值。编码器输出为三相脉冲信号A、B和Z,其中A、B为相位相差90°的信号,A超前B表示电机正转,A滞后B表示电机反转,根据A、B间的相位关系可以判断电机转向。为了保证光电编码器的测速精度,一般要求对AB信号进行4倍频处理。AB信号4倍频的最简单方法是对AB信号进行取沿运算,即在一个A、B信号周期内捕捉4个沿(两个上升沿两个下降沿),如图1所示,从而在一个AB信号周期内产生4个脉冲,实现AB信号的4倍频。

图1 AB信号及取沿运算

2.3 PWM脉宽调制模块原理

直流无刷电机的调速需要脉宽调制电路来实现。由换相控制逻辑电路输出的换相信号的频率与电机的转速有关,还与电机的磙钢极对数有关,无论何种情况下,换相控制信号的频率都远远低于PWM信号的频率。因此,可以把PWM信号和换相控制信号通过逻辑“与”的办法合成在一起,通过调节PWM信号的占空比,来调节电动机的定子电枢电压,从而实现调速。图2为PWM调制信号的产生原理图,其中T为PWM周期,H为三角波的最大值。通过设置H1值,即可输出与H1相关的脉冲OUT1。

图2 PWM调制示意图

2.4 BLDCM换相控制模块原理

换相控制模块是控制器的核心模块。直流无刷电机的转动是根据霍尔位置传感器采集输出的U、V和W三相转子位置信号,导通三相全桥逆变电路相应功率晶体管,使电流依次流经电机线圈绕组产生顺时针(逆时针)旋转磁场,并与转子磁铁发生电磁效应,驱动电机正转/反转实现,导通信号是由换相控制模块处理输出。图3为霍尔位置传感器输出的三相位置信号U、U和W。U、V和W编码可产生8种输出状态组合,加上正反向各一组,一共有16种输出状态组合。由于霍尔位置传感器一个周期(360°)输出6个代码组合(分别为101、100、110、010、011、001),因此有4组代码(包括1000,0000,1111,0111)为无效代码,输出均为111000,上下臂功率晶体管没有串联导通。其余情况均有一组管串联导通。

图3 霍尔位置传感器输出的三相位置信号U、V、W

3 六步BLDCM控制器实现

3.1 光电编码器信号处理模块实现

光电编码器信号处理模块具体实现:在时钟的上升沿对AB信号状态进行检测,实现AB信号4倍频及转向信号提取。假设AB信号在当前时钟上升沿到来前状态为prestate,当前状态为state,则由AB信号组成的8种状态转换(prestate->state),包括00->10、10->11、11->01、01->00、00->01、01->11、11->10及10->00,可以判断当前电机的转向,并在每个状态转换时刻(即A、B信号的每个沿)产生cp四倍频脉冲。

图4 光电编码器信号处理模块仿真波形

图5 BLDCM换相驱动输出功能仿真波形

3.2 PWM脉宽调制模块实现

PWM调制采用加减计数比较法实现。加减循环计数器从零开始加1计数直到最大值H,然后再减1计数直到零,循环产生周期为T的三角波。设定一个数值H1,与循环计数器的计数值比较。当循环计数器的计数值大于H1时输出低电平,计数值小于H1时输出高电平,反复循环,模块输出与H1相关的PWM调制信号。

3.3 BLDCM换相控制模块实现

三相转子位置信号U、V和W编码可产生8种输出状态组合,加上正反向各一组,一共有16种输出状态组合,组合可通过设计组合译码器实现。

4 六步BLDCM控制器验证

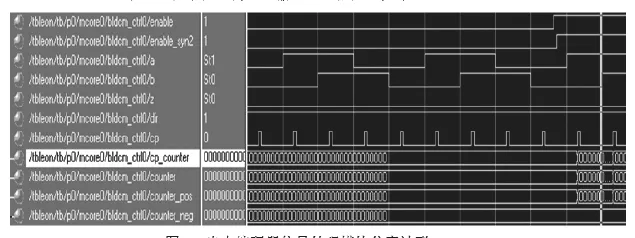

六步BLDCM控制器IP核在Modelsim 6.5g上通过功能仿真,以下为功能仿真波形图。

4.1 光电编码器信号处理模块功能仿真

图4为光电编码器信号处理模块仿真波形。

4.2 BLDCM换相控制模块功能仿真

图5为BLDCM换相驱动输出功能仿真波形。

5 结语

目前六步BLDCM控制器IP核已经在XUPV5-LX110T FPGA开发板上通过硬件测试,并且将作为功能模块应用于SOC芯片设计。实践证明,基于FPGA的BLDCM控制器能够克服MCU软件编程响应速度不快,占用资源较多,且难以快速实现复杂算法控制的缺点,可应用性强。

[1]徐德鸿.电子电子系统建模与控制[M].北京:机械工业出版社,2005.

[2]周渊深.交直流调速系统与MATLAB仿真[M].北京:中国电力出版社,2007.

[3]洪乃刚.电子电子、电机控制系统的建模与仿真[M].北京:机械工业出版社,2010.

[4]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[5]吴继华,王诚.设计与验证Verilog HDL[M].北京:人民邮电出版社,2006.

陈炳成(1983—),硕士,现供职于佛山华芯微特科技有限公司,主要研究方向:嵌入式系统新技术及SOC芯片设计技术。