杜绝插头板工艺导线残留的设计改善

陈 涛 赵启祥 施世坤 张亚锋(胜宏科技(惠州)股份有限公司,广东 惠州 516211)

杜绝插头板工艺导线残留的设计改善

陈 涛 赵启祥 施世坤 张亚锋

(胜宏科技(惠州)股份有限公司,广东 惠州 516211)

简述插头板传统工艺导线设计工艺的弊端,提出了新的设计理念,避开传统观念的插头前端添加工艺导线,而是采用板内寻找网络连接点,建立新的制作流程,实现插头镀金的这一最新理念,从根源上解决了插头工艺导线设计的难题。

内拉工艺导线;网络连接点;蚀刻方式;镀金工艺导线

随着印制电路板行业的快速发展,客户对产品的要求越来越高密度、高性能、高频率化,特别是针对多层板、HDI板,插头板也不例外。特别是针对于HDI系列的插头板品质要求也是越来越特殊。既不允许有工艺导线的存在,又要管控好严格的公差。普通插头、长短插头、如何镀金,而又不能残留工艺导线、斜边露铜,可以说是一个难题。传统设计的前端拉线,已经无法满足所谓的长短插头设计。只有从传统的观念中跳出来,才能适应市场。

现主要从设计的理念和工艺流程上进行改变,结合本公司的机器设备,从根本上解决插头工艺导线残留的问题,提升品质,节约成本、满足客户的需求。

1 传统观念下的工艺导线设计

1.1 普通插头的工艺导线设计

(1)采用插头前端和侧位添加工艺导线的方式,实现印制插头的镀金过程。

(2)弊端。

①插头前端距边缘的高度,在斜边高度的范围内,必然出现斜边后的插头露铜;

②插头前端距边缘的高度,超出了斜边高度的范围,必然出现插头前端工艺导线的残留;

③短插头的侧位拉线,成型后必然出现侧位露铜,上件后出现漏电,闪火。

1.2 长短插头的工艺导线设计

(1) 同样采用前端插头添加工艺导线的方式(图1),实现插头的镀金过程。

图1 长短印制插头均采用前度添加工艺导线的方式

(2) 弊端

①短印制插头由于高度的问题,始终会出现工艺导线的残留;

②长短插头的斜边规格不同于普通板的斜边规格,其斜边高度均会偏小,一般为0.3 mm±0.2 mm的规格,所以,对于斜边机的精度和制程管控的要求甚高,很容易出现斜边高度不够,或者斜边过度,出现披锋、毛刺、甚至于微短;

③因长短印制插头的高度差过大,短印制插头的工艺导线残留太长,在插槽的来回出入,很容易出现工艺导线的脱漏、搭桥引起设备故障,造成产品的投诉,甚至退出市场。

1.3 传统工艺流程

发料——裁板——基板烘烤——内层图形——内层蚀刻——内层检测——压合——钻孔——整板电镀——外层图形——图形镀铜/镀锡——外层蚀刻——外层检验——喷砂——选化干膜(gold-c/s-1)——镀金——去膜——选化干膜(二)(gold-c/s-2)——外层蚀刻(DES)——去膜——检测——阻抗测试——防焊——阻抗测试(二)——文字印刷——成型——测试——FQC——表面处理(OSP)——包装——成品仓

2 新理念的工艺导线设计

鉴于传统印制插头板工艺导线设计的弊端,提出新的PCS内拉工艺导线理念,通过寻找合适的网络点,从而实现插头镀金的设计。

2.1 插头内拉工艺导线的概念

插头内拉工艺导线,主要指的是放弃前端添加工艺导线的设计,通过插头上端的线路或者添加线路,实现与板内其他网络的连接,建立统一的网络关系。

2.2 网络连接点原则

(1)孔PAD与铜皮间;

(2)贴片与贴片间;

(3)IC与铜皮间;

(4)BGA间;

(5)线路与线路(非阻抗线)。

因PCB本身布线的不同,其选择连接的原则必须依次顺序,优先选择(1)、(2)。具体以资料本身的设计为准。

2.3 镀金图形(gold-c/s-1)和蚀刻图形(gold-c/s-2)的辅助设计

2.3.1 镀金辅助图形

指的是采用干膜(抗金干膜)将插头位需要镀金的区域裸露出来,其它非镀金区域全部爆死,保护非镀金区域不可镀金。本文的代码命名为:TOP 层gold-c-1, BOT层gold-s-1。

2.3.2 蚀刻辅助图形照片

指的是采用干膜(抗金干膜),将辅助镀金工艺导线区域裸露出来,保护其它板内布线,不影响客人的布线及设计要求。本文的代码命名为:TOP层gold-c-2,BOT 层gold-s-2。

2.4 工艺流程>

2.4.1 普通工艺

发料——裁板——基板烘烤——{内层图形—内层蚀刻(一)——内层检测压合——钻孔}——整板电镀——外层图形(LDI)——内层蚀刻(二)——外层检验——喷砂——选化干膜(gold-c/s-1)——镀金——去膜——选化干膜(二)(gold-c/s-2 LDI)——外层蚀刻(DES)——去膜——检测——阻抗测试——防焊——阻抗测试(二)——文字印刷——成型——测试——FQC——表面处理(OSP)——包装——成品仓

2.4.2 电镀回填工艺

发料——裁板——基板烘烤——内层图形—内层蚀刻(一)——内层检测——压合——钻孔——整板电镀——树脂塞孔——塞孔研磨——减铜——沉铜+GAP电镀——外层图形(LDI)——内层蚀刻(二)——外层检验——选化干膜(gold-c/s-1)——镀金——去膜——选化干膜(二)(gold-c/s-2 LDI)——外层蚀刻(DES)——去膜——检测——阻抗测试——防焊——阻抗测试(二)——文字印刷——成型——测试——FQC——表面处理(OSP)——包装——成品仓

2.5 镀金图形的PCS内的设计(gold-c/s-1)

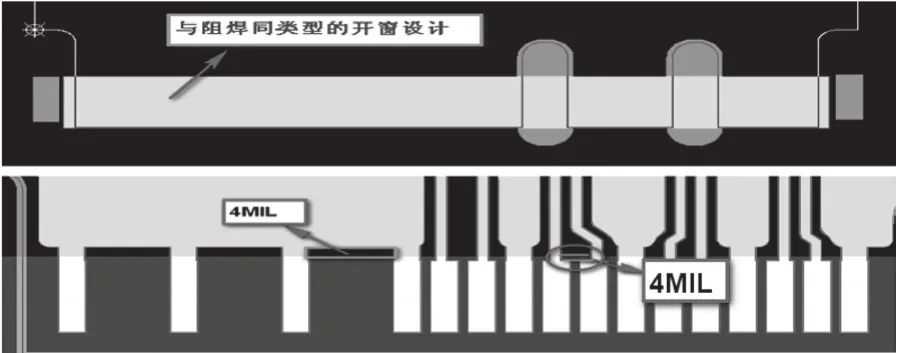

插头的阻焊开窗均是按通窗设计,避免插头间因油墨存在,在多次的来回穿插中出现掉墨,微短现象。因此,镀金图形的设计也是依通窗设计为准,最好依客户阻焊通窗开窗的设计为准,为了确保镀金图形的公差以及插头的长度公差,其镀金图形必须在与金插头上端平齐的条件下,上提0.1 mm,确保插头镀金的完整性。其镀金图形的开窗上端距板内铜皮及线路至少保留0.1 mm的距离,以免因图形照片的偏差导致板内非镀金区域出现部分镀金,影响品质。如图2示。

图2

2.6 具体分析网络连接个原则点的设计

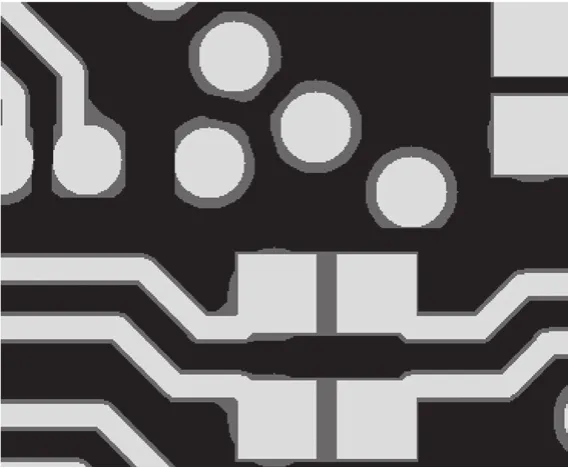

2.6.1 孔PAD与铜皮间的设计

(1)工艺导线设计。寻找印制插头上端对应线路的网络关系,确定其过孔位置后,将过孔与周片的铜皮,按最小0.15 mm的工艺导线相连接,使其插头与铜皮间成为同一个网络关系。为了避免过孔破孔,其过孔的环必须大于0.125 mm,孔PAD与铜皮间的间距至少在0.125 mm以上,如图3示。

图3

(2)蚀刻图形的设计(gold-c/s-2)。蚀刻图形照片的设计原则依圆弧为准,确保蚀刻后连接点间的圆滑,避免蚀刻后成品出现凹凸不齐的状态。

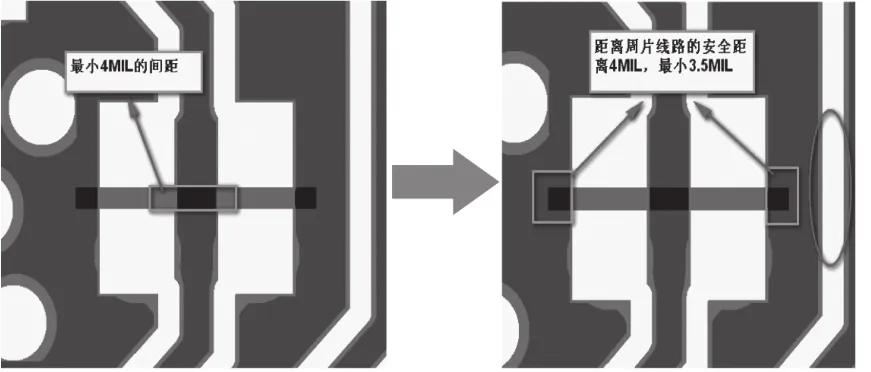

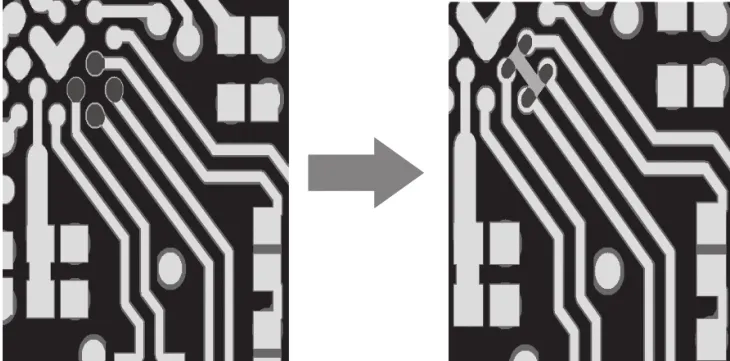

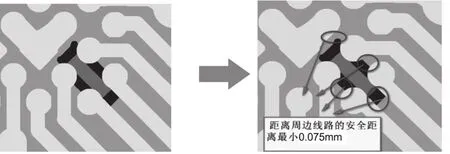

2.6.2 贴片与贴片间的设计

(1)工艺导线设计。通过PTH孔的网络关系,寻找同组贴片,建立连接点,形成网络关系,实现插头的镀金。其贴片间的工艺导线连接,必须依贴片的同等大小相连,不可出现线性的连接。例如:同组贴片的大小为:0.46 mm×0.46 mm,贴片的间距为0.15 mm。连线的设计如图4示。

图4

此种工艺导线方式的设计,便于控制贴片的大小完整以及目视外观效果完整性的。工作稿贴片间的间距最小为0.75 mm,但因反蚀刻差数的影响。为了确保贴片的大小,可将贴片为连接点部分的另一端拉长0.025 mm ~ 0.05 mm。

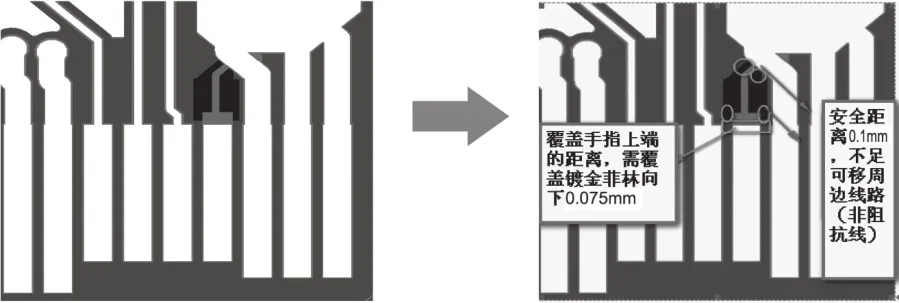

(2)蚀刻图形的设计(gold-c/s-2)。设计原则依直线为准。确保贴片蚀刻后的完整平滑。贴片间的间距最小0.1 mm,蚀刻线距离周边线路及贴片的安全距离0.1 mm,最小0.075 mm,距离不足可移动周边的线路(非阻抗线),或者适当削PAD(0.025 mm ~0.05 mm),具体如图5示。

图5

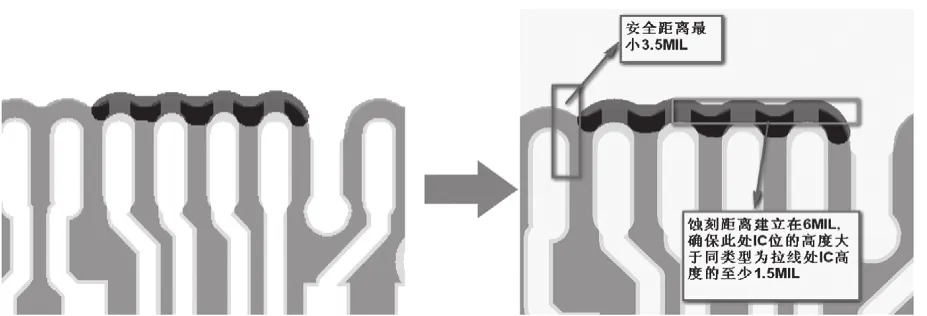

2.6.3 IC与铜皮间的设计

(1)工艺导线设计。建立IC与铜皮间的网路关系,工艺导线的大小不可大于1/2 IC的大小,原则依0.15 mm设计,IC与铜皮的间距最小0.125 mm。

(2)蚀刻图形的设计(gold-c/s-2)。蚀刻图形的设计原则依圆弧为准,确保蚀刻后连接点间的圆滑。如图6。

图6

2.6.4 BGA间的设计

(1)工艺导线设计。建立BGA间网络关系,工艺导线的大小不可小于1/2 BGA的大小,原则依0.125 mm设计,如图7。

图7

(2)蚀刻图形的设计(gold-c/s-2)。蚀刻图形的设计原则依圆弧为准,确保蚀刻后连接点间的圆滑。如图8示。

图8

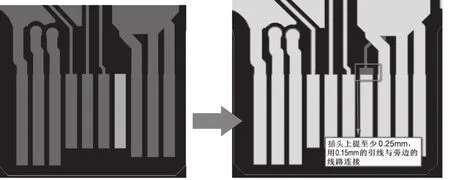

2.6.5 线路与线路间的设计

(1)工艺导线设计。此设计主要针对于独立插头,在无法实现以上几种方案的情况下的设计。工艺导线大小原则6 mil,如图9示 。

图9

(2)蚀刻图形的设计(gold-c/s-2)。确保插头上上端的完整,如图10示。

图10

2.7 镀金工艺导线的设计

2.7.1 插头工艺导线的板内设计

镀金工艺导线也需板内设计,不可按依常规的从插头两侧或者内层拉工艺导线,以免成型后露铜,上件板出现漏电、闪光。设计原则:选择接近外形边缘的铜皮,必须是与插头建立网络关系的铜皮,(不可选择线路、贴片、IC)。工艺导线的大小标准0.3 mm ~ 0.5 mm。

镀金工艺导线的外形外拉,原则是选择铣槽位,V-CUT位置,便于反蚀刻,满足客人的需要。如图11所示。

图11

2.8 工艺导线蚀刻的设计

2.8.1 工艺导线蚀刻

工艺导线蚀刻通过建立gold-c/s-2辅助图形照片,曝光、显影、蚀刻从而将工艺导线蚀刻掉,设计原则如下:

(1)PCS内工艺导线的蚀刻上面已针对不同类型的设计都有描述;

(2)镀金工艺导线的外拉以及拼版内工艺导线的蚀刻,原理一致,只是将本身不需要的辅助设计去除掉,大小无特别要求,只是其蚀刻线距离周边的安全距离不能小于0.1 mm,避免底片的涨缩偏差。

2.9 辅助图形板边的设计

2.9.1 镀金图形板边的设计(gold-c/s-1)

采用正片照相底片,板边开导电窗,导电窗开与印制插头水平的方向,长度大于1/2板边的长度,居中即可,上下板边做出线路自动CCD对位圈,照片对应料号名。假印制插头的镀金开窗只需开出对应导电窗边缘的高电流区即可。无需全部做出,浪费金。

镀金开窗对应的板边即为高电流区域,所以对应的假插头需开窗镀金,分担电流,其它假印制插头均不需开窗镀金。

2.9.2 蚀刻图形板边的设计(gold-c/s-2)

(1)采用负片作业,处理板内工艺导线及板边拉升的辅助工艺导线需要蚀刻外,其余部分全部覆盖,不可露出线路。板边做出定位孔环、长边防焊CCD对位PAD(与防焊CCD一致,采用正片格式)、线路CCD对位PAD(负性格式)、料号名即可。

(2)长边防焊CCD对位PAD主要是用于LDI作业时,对位抓点。

(3)线路CCD对位PAD(负性格式)由于干膜曝光作业的自动对位。

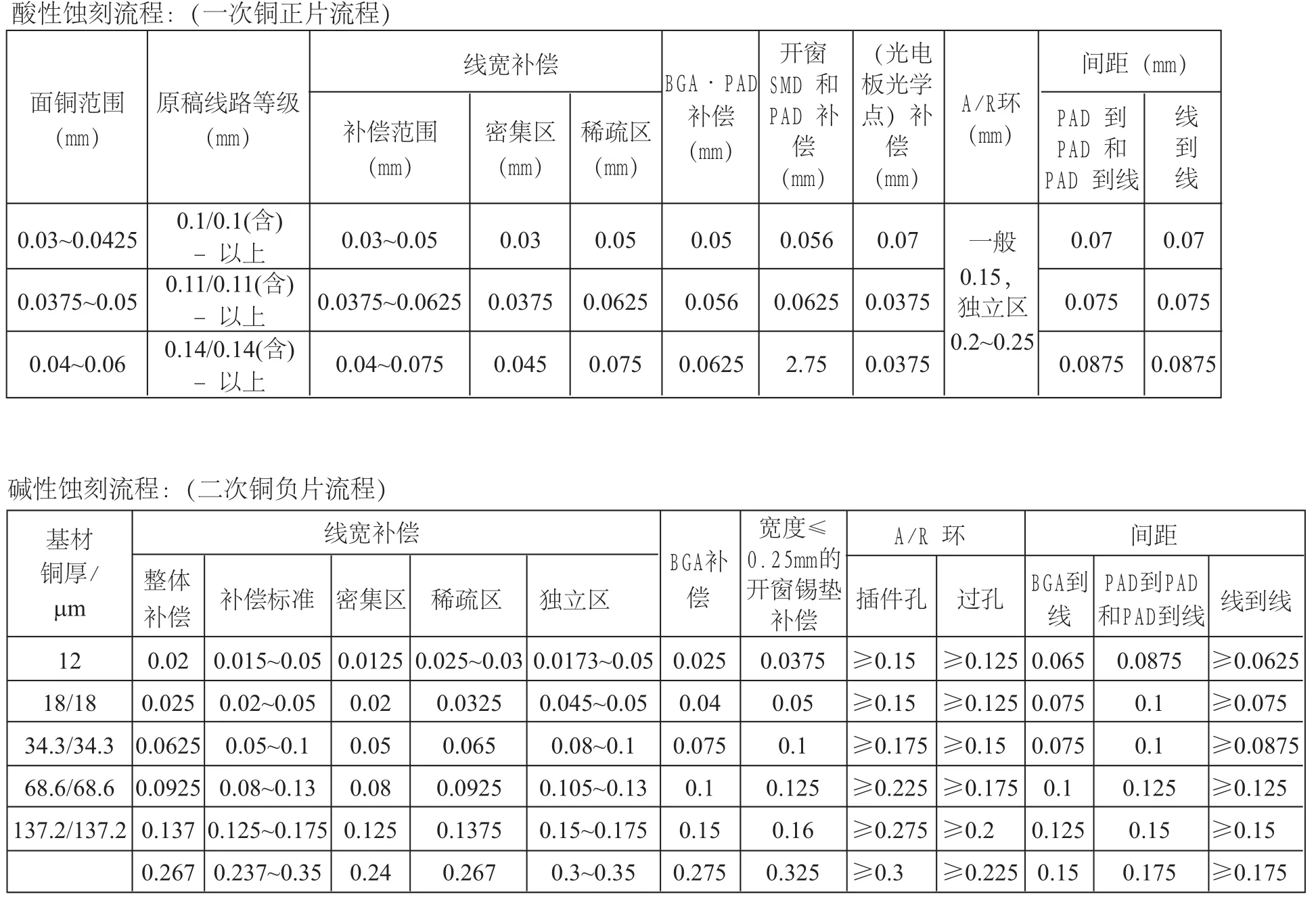

以上只是对发料铜厚度为12 μm及18 μm/18 μm板内工艺导线设计的法案,针对于发料34.3 μm/34.3 μm及68.6 μm/68.6 μm的设计,其工艺导线板内选择连接点的原则均是相同的,只是34.3 μm与68.6 μm因各公司的蚀刻能力不同,所以线宽线距的最小标准不同,其内工艺导线设计的线宽和安全距离与其蚀刻能匹配即可以。其辅助图形以及板边所添加的SMBER 均是一样的。以下图12为我公司的补偿标准,可做参考。

备注:

(1)板内连接点的选择必须遵循的原则, 孔PAD与铜皮;贴片与贴片间;IC与铜皮;BGA间;线路与线路(非阻抗线)。则有选择、此两中连接方式;

(2)对于客户要求电镀回填之料号,必须采用LDI 酸性蚀刻方式,在整板电镀工序,管控孔铜要求;

(3)如果采用BGA间的网络连接点方式,因考虑对位偏差的因素,针对于第一次干膜线路(图形转移)以及蚀刻辅助干膜(gold-c/s-2),必须采用LDI作业,确保品质;

(4)回填电镀的要求,建议采用LDI作业的方式,酸性蚀刻方式,确保品质及控制成本,不建议使用干膜CCD作业的方式。

图12

3 结果

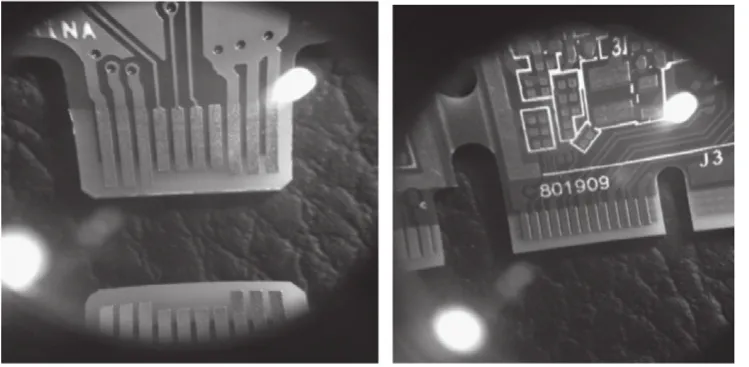

3.1 印制插头的成品效果(图13)

图13

3.2 此设计的优点

(1)彻底杜绝了插头前端工艺导线的存在;

(2)解决了因前端设计工艺导线存在的披锋、翘皮、微短等品质问题;

(3)避免了因侧位添加工艺导线出现的漏电、闪火现象;

(4)减小因品质造成的补料、报废、人力、水电的成本。

印制插头板内拉工艺导线的新理念以及工艺流程的改进,在很大程度上改变的传统印制插头的工艺导线作法,提升了印制插头板的品质。

陈涛,行业高级工程师,专注于高精密度线路板的研发、生产与销售,运用科学运营管理模式带领公司不断发展壮大。

Improving design to avoid lead residue of gold finger

CHEN Tao ZHAO Qi-xiang SHI Shi-kun ZHANG Ya-feng

This paper mainly introduces the traditional weakness of finger plate leading design technology and raises a new design concept concerning a variety of problems to avoid adding wire at the front end of the finger by looking for network connection point to establish new process to fulfill the latest idea of gold plating of finger so as to solve the problem from the root by putting an end.

Pull Wire; Network Connection Point; Etching Method; Gold Plated Lead

TN41

A

1009-0096(2015)05-0031-06