基于电阻链移相的时栅高速测量方法研究*

索龙博, 陈锡侯, 苟 李, 张天恒, 曹 焕

(重庆理工大学 机械检测技术与装备教育部工程研究中心 时栅传感及先进检测技术重庆市重点实验室,重庆 400054)

基于电阻链移相的时栅高速测量方法研究*

索龙博, 陈锡侯, 苟 李, 张天恒, 曹 焕

(重庆理工大学 机械检测技术与装备教育部工程研究中心 时栅传感及先进检测技术重庆市重点实验室,重庆 400054)

针对时栅位移传感器因频率响应慢影响测量速率的问题,提出了一种电阻链移相结合数据处理的方法。利用电阻链对时栅输出信号进行移相处理,采用多路模拟选择器和整形输出电路对移相后的信号分时输出,运用可编程片上系统(SOPC)技术进行数据处理和误差补偿。实验结果表明:采用该方法采样频率由原来的400 Hz提高到12.8 kHz,大幅度提高了现阶段时栅位移传感器的频率响应,使传感器实现了高速实时测量。同时能够有效地降低了随机误差,对极内的误差峰—峰值由1.5″降低为0.8″,测量精度提高了近1倍。

时栅; 电阻链; 多路模拟选择器; 可编程片上系统

0 引 言

时栅位移传感器采用相对运动双坐标系,将静止坐标系上的位置之差,转换成运动坐标系上的时间之差,从而实现“用时间测量空间”[1,2],其具有高精度和高分辨力、低成本、抗干扰能力强等诸多优点。近年来,时栅传感器在业界表现出强大的竞争力,正在向产品化、产业化方向发展,已在精密数控转台控制系统、传动误差检测系统以及国防精密加工中得到广泛的应用。根据时栅传感器时间测量原理,在400 Hz的激励频率下,通过高频时钟插补动、定测头感应信号正向过零点时间差的方式,使得传感器的测量速率仅有2.5 ms/次,难以实现高速测量。

为了提高时栅传感器的频率响应,从而提高测量速率,实现高速测量,使其在同等的时间间隔内采集更多的数据进行平均处理以减小随机误差,从而提高传感器的测量精度,现提出电阻链移相的方法。电阻链移相是一种常用的电子细分手段,一般用于光栅传感器以提高角度测量的精度和分辨力。本文将其应用于时栅传感器的信号处理系统来提高传感器的频率响应,从而解决现阶段时栅所存在的测量速率慢的问题。在系统设计中采用可编程片上系统(SOPC)技术将信号的采集、处理、传输等集中在高性能现场可编程门阵列(FPGA)上实现,解决了移相后多路数据处理的实时性问题。

1 时栅位移传感器原理

1.1 结构原理

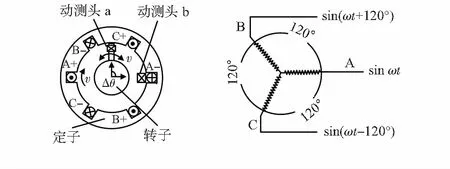

时栅传感器的结构主要包括定子、转子、定子内嵌线圈以及2个线圈绕制的测头,如图1所示。其结构与三相交流电机类似,在空间上互差120°的三相线圈中通入时间上互差120°的交流激励电源后,定、转子之间产生一个匀速旋转磁场,旋转速度为V。两个测头置于旋转磁场内,一个固定不动,称作定测头;另一个随转子一起运动,称作动测头,其运动速度为v。在已知旋转磁场速度V的情况下,通过检测旋转磁场经过两个测头的时间差ΔT,就可以得到转子转动的角位移θ=VΔT[3](设两个测头重合的地方为起点,即角位移为0)。

图1 时栅传感器结构原理图

1.2 时间测量原理

时栅传感器的时间测量原理如图2所示。首先通过零检测电路将动、定测头上感应出的两路行波信号转换为方波信号;再利用高性能比相电路把动、定测头信号正向过零点之间的相位差转换成为时间差,即完成时空转换;最后采用高频时钟脉冲对该时间差进行时钟插补,高频时钟脉冲的频率大约在10 MHz以上[4]。每个时钟脉冲对应一定的空间角位移,对脉冲进行计数就可实现位移测量,可根据式(1)计算出角位移值

(1)

式中Ti为动测头上升沿出现时刻;T0为定测头上升沿出现的时刻;W为绕组节距;ΔT为动、定测头正向过零点之间的时间差。

图2 时间测量原理图

2 电阻链移相的应用

在现有400 Hz的激励频率下,为实现对时栅信号在一个信号周期内完成多次测量,提高传感器频率响应,实现高速测量。应用电阻链移相原理设计了具有32路输出的电阻链移相网络,将传感器在一个信号周期内只能测量一次,转变为可以进行32次测量,极大提高传感器的频率响应。

2.1 频率响应的分析

现有时栅传感器频率响应较慢的原因主要来自两方面:一是电路处理方式的原因,因为时间行波信号过零点处的斜率最大,为了提高时栅传感器的灵敏度,尽可能减少干扰对转换时刻点的影响。整形输出电路采用过零检测电路实现。这种处理方式虽然提高了传感器灵敏度,减小了干扰对信号转换质量的影响,但过零检测的方式降低了传感器的频率响应,使得传感器在一个信号周期内只能进行一次测量,严重影响传感器的测量速率;二是激励信号频率的原因,时间行波的变化速率与激励频率呈正比关系。激励信号频率越高,其变化速率越快,采集一次数据的时间就越短,因此,传感器的频率响应越高,测量速率越快,在相同的时间内可采集更多的数据平均处理,测量的精度就越高。但激励信号频率越高,同样的干扰对传感器的影响就越大。且在插入的高频时钟频率一定的情况下,脉冲当量就越大,即分辨力就越低。要提高分辨力,就只能提高插入的高频时钟频率,高频信号对信号处理系统的设计和对电路板的电磁兼容性设计提出了更高的要求。因此,综合考虑上述几方面的因素,时间信号的频率选为400 Hz[4]。根据时间测量原理传感器在2.5 ms内只能完成一次测量,其频率响应较慢,测量速率受到限制。

2.2 电阻链移相原理

电阻链移相作为一种常用的电子细分方法,常用于光栅信号的细分,以提高光栅传感器的分辨力和精度,其具有细分能力强、精度较高、电阻元件容易获得等优点。

电阻链移相原理是将两个不同的交变信号施加在电阻链两端[5,6]。由于电压合成的移相作用,在电阻链的各电阻插头上将得到幅值和相位不同的一系列移相信号。本文将时栅动测头输出的两对正交信号施加在电阻链两端[7~9],把动测头信号的非过零点通过移相转换成为过零点,然后利用整形输出电路将移相后的信号整形为方波,与定测头方波信号进行比相,实现一个信号周期内可以进行多次测量的目的,这种方式在保证传感器灵敏度和抗干扰能力的情况下,提高了传感器的频率响应,从而实现了高速测量。

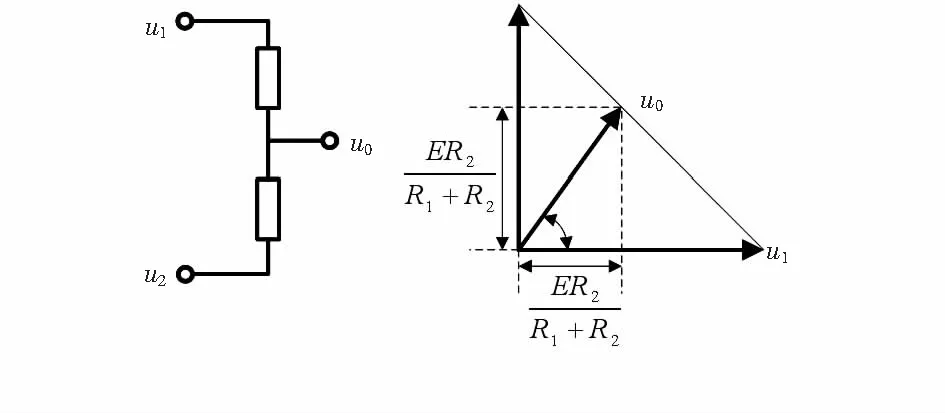

设电阻链由电阻R1和R2串联而成,电阻链两端加有交流电压u1=Esinωt和u2=Ecosωt。

应用叠加原理求出电阻链节点处输出电压为

(2)

由图3中矢量图求得幅值和相位差为

(3)

(4)

输出电压可以表示为

uo=uomsin(ωt+θ).

(5)

根据图3中矢量图可知,通过改变R1和R2的比值,可以改变θ,即实现了信号的移相,矢量uo的终点沿直线运动,当θ=45°时,uom取最小值,第一象限的情况如此。电路两端若接cosωt和-sinωt,可以得到第二象限各相输出电压;接-sinωt和-cosωt可以得到第三象限各相输出电压;接-cosωt和sinωt可以得到第四象限各相输出电压。因此,可以通过移相的方式将动测头信号的任意位置移动到过零点来实现测量。

图3 电阻链移相原理图

3 系统设计

为了完成对信号的高性能实时性处理,采用SOPC技术,利用硬件描述语言(Verilog HDL)进行数字处理模块的设计。动测头输出的两对差分信号经电阻链移相转换为32路信号输出,为了不增加整形输出电路的个数,在硬件上,设计多路选择电路,利用每路信号之间固有的相位差,对其分时输出。在软件上,设计Nios II软核处理器内主控程序对采集的信号进行数据处理[10]。

3.1 硬件设计

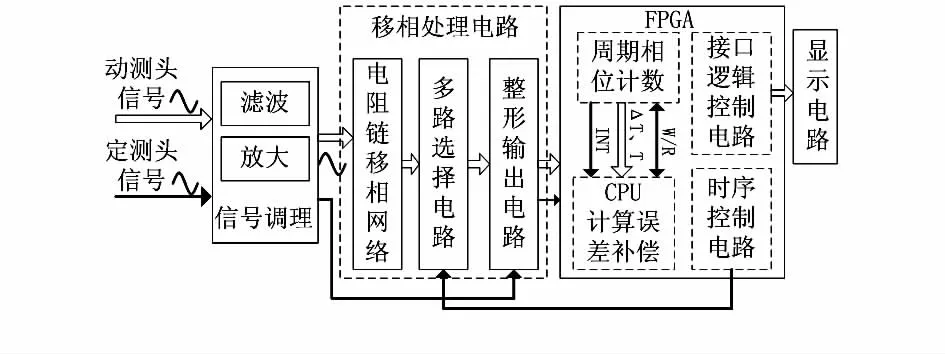

时栅位移传感器信号处理系统框图如图4所示,该信号处理系统主要包括信号调理电路、电阻链移相网络、多路选择电路、整形电路、FPGA数字信号处理电路以及显示电路。

动、定测头的感应信号通过信号调理电路放大、滤波后,送入电阻链移相网络进行电压合成移相。利用选择器分时输出移相后的动测头信号,同时把选择器输出信号和调理后的定测头信号分别送入整形输出电路进行处理,得到方波信号。将两列方波信号送入FPGA,利用周期相位计数电路对两列信号相位差和动测头信号的周期进行高频时钟插补,把所得到的计数值送入CPU进行相位校正、数据处理和误差补偿,最终将结果送入数码管显示电路进行显示。

图4 信号处理系统框图

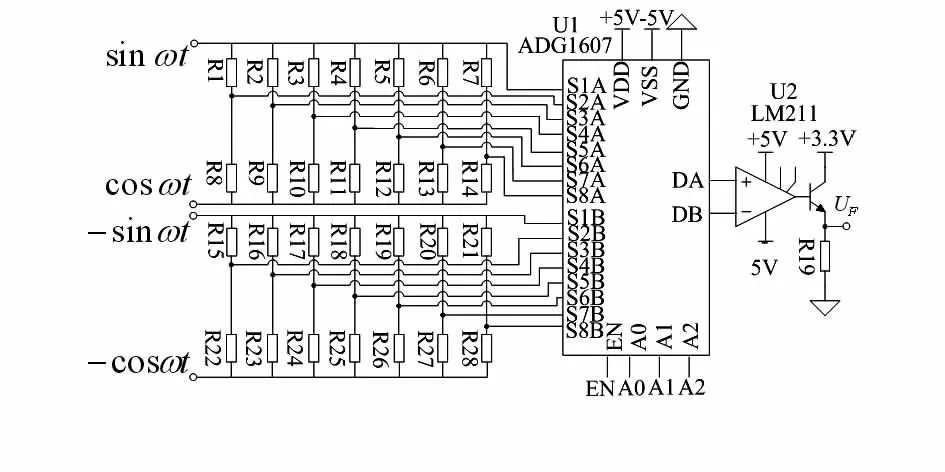

移相处理电路原理图如图5所示,电阻链移相网采用并联的方式设计,其优点在于每个支路输出信号的移相角只与该支路上两个电阻的比值相关,而不受其他支路电阻的影响,便于计算。将两对时栅差分信号经移相网络移相后输出32路信号,相邻两路信号之间的相位差为11.25°。现以第一象限为例加以介绍,为抑制共模干扰,减小零点漂移,整形输出电路采用差分输入的接法。根据电阻链移相的原理可知,移相后第一象限的输出信号和第三象限的输出信号对应正好构成一对差分信号,因此,利用差分多路模拟选择器(ADG1607)将该差分信号分时输出到整形输出电路进行转换,得到一系列方波信号。多路选择器的时序控制信号由FPGA的时序控制电路提供。

图5 移相处理电路原理图

3.2 软件设计

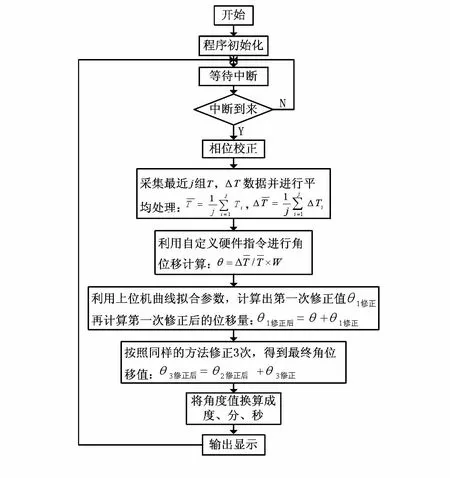

通过Eclipse集成开发环境完成相关软件程序设计。利用高频时钟插补电路对动、定测头正向过零点的时间差进行时钟插补,将所得的计数值送入Nios II嵌入式软核处理器,在CPU中计算当前的角位移大小。因为经过移相后的信号与实际信号之间有一个固定的相位差,所以,在进行角度计算之前要先对每路信号完成相应的相位校正,得到真实的角位移值。为提高CPU的运算速度,通过在Nios II指令系统中增加自定义指令,把复杂的标准指令序列中的乘法指令运算转换为一条用硬件实现的单个指令,以提高软件处理的实时性[11]。利用谐波修正技术对角度误差进行修正[12],极大提高测量精度。系统软件流程图如图6所示。

图6 软件设计流程图

4 实验研究

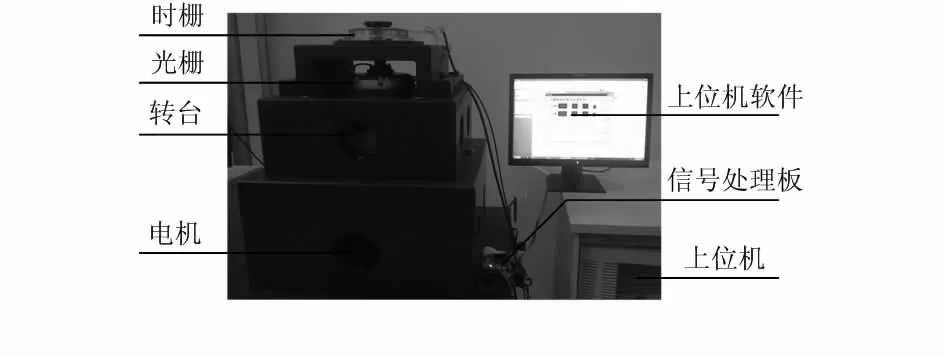

为验证设计的时栅信号处理系统的性能,对所研制的时栅信号处理板做如下实验,实验平台如图7所示。

图7 实验平台

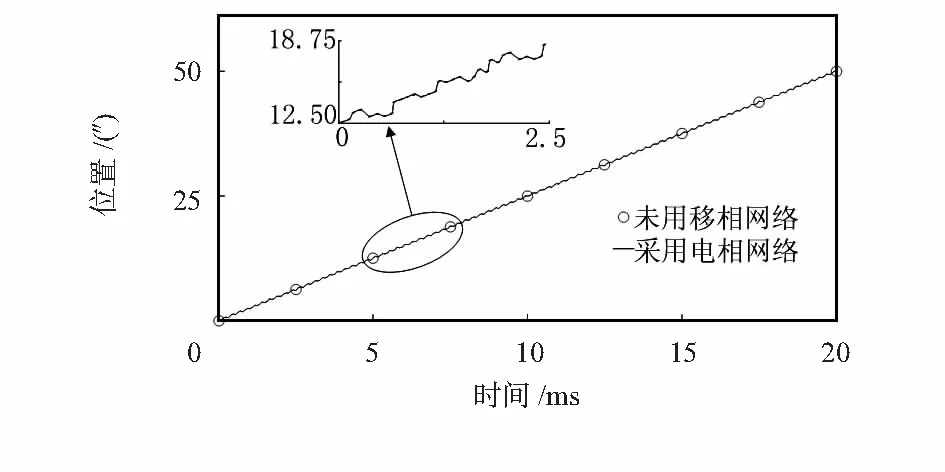

利用一元线性回归对所采集的时栅数据进行拟合,得到时栅传感器频率响应曲线,如图8所示。当未使用电阻链网络时,依照时栅传感器时间测量原理,在8个时间周期,即20 ms内,只能完成8次测量,得到8个采样点。当采用具有32路输出的电阻链移相网络之后,在相同8个时间周期可以完成256次测量,得到256个采样点。采样频率从之前的400 Hz增加到12.8 kHz,实现高速测量。图8中小图表示1个时间周期内,因测量点数增多所反映的时栅角位移细节变化情况。从图中明显看出:因传感器频率响应的提高,得到更加精确的时栅角位移变化曲线。

图8 频率响应曲线图

对比实验以高精度的Heidenhain 圆光栅(精度为±1″)作为基准,以分度转台作为测量对象。光栅与时栅同轴安装,转台转动的同时,时栅和光栅进行同步采样,两者测量值之差即为误差值。图9为72对极的时栅位移传感器对极内的误差曲线。从图中可以看出:采用电阻链移相网络后时栅对极内的误差峰—峰值由之前的1.5″降低为0.8″,实现高精度测量。

图9 误差曲线图

5 结束语

通过采用电阻链移相网络提高了时栅位移传感器的频率响应,实现高速测量。利用多路选择电路解决了整形输出电路的冗余问题,在节约系统成本的同时,也实现了系统的小型化设计。基于SOPC技术定制符合需求的专用Nios II软核处理器对时栅信号进行处理,系统仅集成在一片高性能的FPGA上,即简化了电路的结构设计,降低系统功耗,又提高了传感器的动态性和实时性。实验结果表明:该方法大幅度提高了现阶段时栅位移传感器的频率响应,同时使测量误差减小近1倍,峰—峰值仅为0.8″。

[1] 彭东林,张兴红,刘小康.场时时栅位移传感器研究[J].仪器仪表学报,2003,24(3):321-323.

[2] 彭东林,陈锡侯,朱 革,等.时栅的波动方程分析和行波形成新办法[J].机械工程学报,2006,42(11):113-115.

[3] 汤其富,彭东林,武 亮,等.时栅角位移传感器中的多普勒效应影响及其抑制方法研究[J].仪器仪表学报,2014,35(3):620-626.

[4] 彭东林,刘小康,谭为民.时空坐标转换理论与时栅位移传感器研究[J].仪器仪表学报,2002,21(4):338-342.

[5] 强锡富.传感器[M].3版.北京:机械工业出版社,2001:188-194.

[6] 于 耕,马晓梅,郭华鹏.圆光栅测角系统信号细分电路设计[J].电子设计工程,2012,20(15):99-102.

[7] Tan K K,Zhou H X,Lee T H.New interpolation method for quadrature encoder signals[J]. IEEE Transactions on Instrumentation and Measurement,2002,51(5):1073-1079.

[8] 杨继森,许 强,冯济琴.基于STM32F4 的时栅位移传感器信号处理系统集成化设计[J].传感器与微系统,2013,32(12):113-116.

[9] Birch K P.Optical fringe subdivision with nanometric accura-cy[J].Precision Engineering,1990,12(4):195-198.

[10] 蒋丽雁.基于FPGA的光栅信号处理电路设计[J].工具技术,2010,44(5):100-102.

[11] 郑方燕.基于SOPC的时栅位移传感器信号处理系统设计[J].传感技术学报,2012,25(10):1429-1432.

[12] 高忠华,陈锡侯,杨继森,等.直线时栅传感器全误差模型与误差修正方法研究[J].传感器与微系统,2012,31(8):87-89.

陈锡侯,通讯作者,E—mail:cxh0458@163.com。

Study on method for time-grating high-speed measurement =based on phase-shifting of resistance chains*

SUO Long-bo, CHEN Xi-hou, GOU Li, ZHANG Tian-heng, CAO Huan

(Engineering Research Center of Mechanical Testing Technology and Equipment,Ministry of Education,Chongqing Key Laboratory of Time-Grating Sensing and Advanced Testing Technology,Chongqing University of Technology,Chongqing 400054,China)

Aiming at the problem that measuring rate of time-grating displacement sensor is affected due to slow frequency response,,a method combining data processing and phase-shifting of resistance chains is proposed.The output signal of time-grating is phase-shifting processed by resistance chains and timeshare output by multiplexers and shaping output circuit,and the SOPC technology is used for data processing and error compensation .Experimental results show that the original sampling frequency of 400 Hz can be improved up to 1.28 kHz,which can substantially increase the frequency response of the time-grating displacement sensor ,and high-speed real-time measurement is achieved.Meanwhile the random error is effectively reduced,the peak-peak value of error is decreased from 1.5″ to 0.8″ within antipode,and the measurement precision is nearly double improved.

time-grating; resistor chain; multiplexers; SOPC

2015—01—12

国家高科技研究发展计划(“863”计划)资助项目 (2012AA041202)

10.13873/J.1000—9787(2015)09—0051—04

TP 206

A

1000—9787(2015)09—0051—04

索龙博(1988-),男,陕西宝鸡人,硕士研究生,主要研究方向为计算机辅助测试技术与仪器。