基于FPGA 的CPU 设计分析

李 翰 姜彦吉

辽宁工程技术大学软件学院

本文对基于FPGA 的CPU 设计进行了分析,主要包括CPU 指令代码的设计以及电路的设计,对嵌入式CPU 设计工作的相关研究具有一定的参考价值。

1 FPGA 简介

FPGA 是以GAL、PAL、PLD 等可编程器件为基础发展起来的一种现场可编程门阵列。相对于GAL、PAL和PLD,FPGA 具有较大的规模,它能够替代几十甚至几千块通用的IC 芯片,具有处理速度快、存储容量高、I/O 功能强大、功耗低等多种特点。通过FPGA 技术,可以更方便快捷的设计出较为简单的完整CPU 模型机。FPGA 的应用可以有效解决定置电路的缺陷,同时还能突破原有可编程器件对门电路的限制。FPGA 突出的特点使得其可以很好的应用在各类PLD、应用门阵列和中小规模的通用数字集成电路设计工作中。

2 基于FPAGA 的CPU 设计

CPU 设计功能

基于FPGA 的CPU 主要包括指令系统的设计、电路的设计两个方面的内容。本CPU 采用RISC(精简指令集)架构的指令系统,按照功能可以将本CPU 的指令分为计算指令、数据传送指令、位操作指令以及转移指令;电路的设计则主要包括基本电路和主要电路模块的设计两部分内容。

指令代码设计

(1)ALU 运算指令

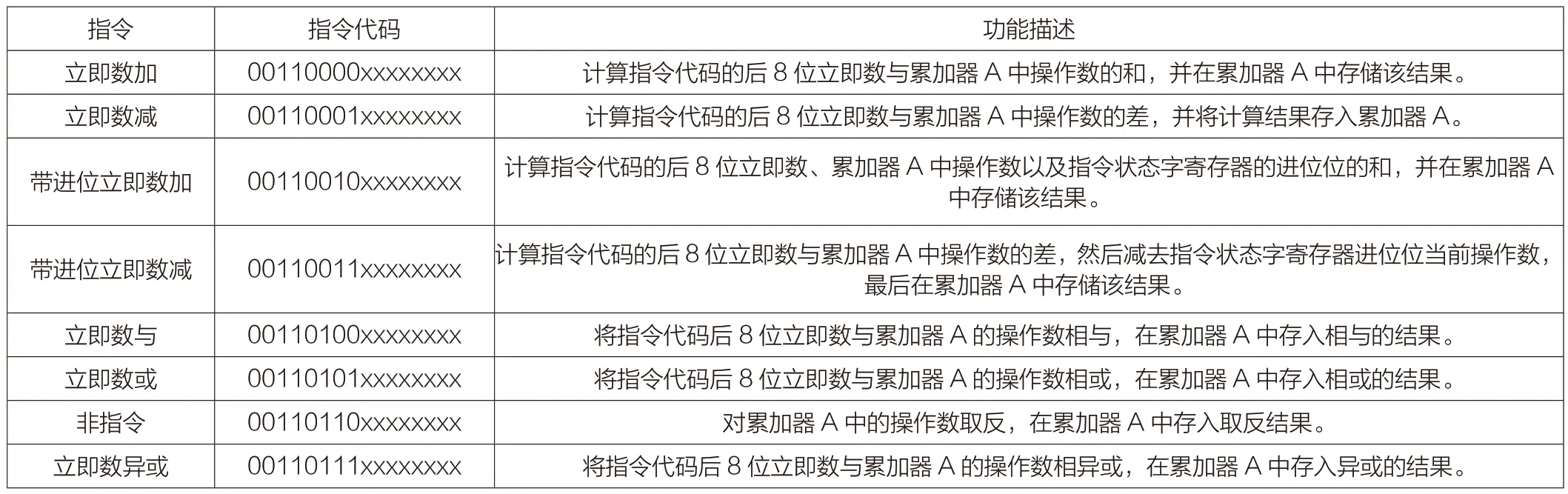

表1 ALU 立即数指令

表2 数据传送指令

ALU 运算指令的操作数来源有两个,其中一个操作数由累加器A 提供,另一个操作数则是指令字中立即寻址方式所提供的8 位操作数或者RAM,然后在累加器或者RAM 中存入操作数。ALU 运算指令分为两类:立即数指令和双操作数指令。其中立即数指令的操作数分别来自累加器A 以及指令立即寻址方式所提供的8 位操作数,并将指令结果存入累加器A,其中,累加器A 中的操作数属于非运算操作数。ALU 立即数指令如表1 所示。

(2)数据传送指令

数据传送是CPU 所需要基本的数据处理功能,数据传送的主要目的是拷贝指定的源操作数字节内容到目的操作数单元。表2 对本CPU 的数据传送指令代码和作用进行了说明,表中的“z”表示该位代码无效,其取值不会对指令的具体功能产生任何影响,而“x”则表示该位中的数据可以任意取值,其取值结果代表当前指令的操作数。

(3)位操作指令

位操作指令主要是对二进制数据的某一位进行左右移操作,内存单元的自增、自减以及工作寄存器组的自增、自减。从总体分,可以将其分为移位和自增自减两类指令。

(4)转移指令

转移指令可以分为条件转移和无条件跳转两大类,具体又可分为条件转移、跳转、过程调用以及返回指令。在设计条件转移指令时,固定其转移条件使其跳过当前条件直接执行下一条指令。要想实现真正的跳转,需要利用强制跳转指令代码,使其进行强制跳转,具体实现代码如下:

JC

JMP MAIN_LOOP

MOV A,#00H

MAIN_LOOP:MOV R0,#0FFH;

只有CY 为1 时,JC 语句后执行MOV A,#00H(跳过了JMP MAIN_LOOP 指令);而当CY 为0 时,则JC 语句之后按照正常顺序执行指令。

电路设计

(1)基本电路

在CPU 设计的过程中,CPU 的基本电路由逻辑门电路、触发器、译码器等构成。与、或、非是最基本的三种逻辑关系,在CPU 电路设计中,分别以与门、或门以及非门表示。逻辑与的操作是两个操作数的按位与,可以用Z=A.B 表示;逻辑或操作则是两个操作数的按位或,可以用Z=A+B 来表示;逻辑非操作是将操作数按位取反,可以用Z=!A。

译码器的主要功能是对通过译码操作将二进制数值转换成特定编码形式的输出信号。当译码器中所输入的二进制数值位数为n 时,则输出数据的个数则为2 的n 次幂。所有输出数据都对应一个二进制数值。

数据选择器的逻辑功能是利用地址选择信号对输出的数据进行控制,然后从多个数据中选择一个输出。

(2)CPU 各模块电路的设计

CPU 的硬件电路可以分为多个模块,主要包括算术逻辑单元、移位模块、译码模块等。下面列举了其中几个模块的设计。

1)算术逻辑单元设计。CPU 的算术逻辑单元共包括3 个数据输入端和4 个数据输出端。其中,3 个数据输入端中的一个固定由累加器输入,另外两个数据则分别由8 位立即数、RAM 或者特定的工作寄存器以及CY 输入。数据输出端中的3 个1 位输出分别为算术逻辑单元运算的进位输出端CY_ALU、标志算术逻辑单元运算结果是否为0 的输出端Z_ALU 以及标志算术逻辑单元运算是否发生溢出的输出端V_ALU;另外一个则是算术逻辑单元运算数据输出端。

2)移位模块的设计。CPU 的移位指令有循环移位、带进位循环移位、逻辑移位和算术移位4 种操作。这4种移位操作均可以分为左移和右移两种操作。其中,循环移位是按照固定的方向对操作数进行移位循环移位,移出移至移入位;带进位循环移位则是将操作数移出位移至进位位,进位位移至移入位;逻辑移位是将操作数看作没有符号位的逻辑数,在每次进行移位时,其移入位的值均为0;算术移位将操作数看作有符号位的数据,而符号位中的值可以决定操作数的移入位。

电路仿真

利用Quartus Ⅱ软件进行电路仿真,每次构建好一个电路模块便进行一次仿真,保证在构建整个电路前,各个电路模块的功能均正常。在构建完整的CPU 电路之后,在对整个电路进行仿真,在每次仿真之后,发现错误,需要立即进行改正,并再次进行仿真。

3 CPU 功能测试

在仿真工作完成后,对整个CPU 的功能进行测试,主要包括各项基本功能的测试以及物理测试两个方面的内容。将CPU 写入FPGA 新片中,并在FPGA 中构建RMA 模拟指令存储器用来放入CPU 的各项操作指令,同时还需要设计一个完整的外围测试系统,实现对CPU全部功能的测试工作。

4 结语

虽然目前的CPU 种类较多,结构也存在较大差异,但是目前的主流CPU 几乎都采用硬核结构,本文设计了一款基于FPGA(软核)的嵌入式CPU,对促进嵌入式CPU 设计工作的发展具有重要的作用。