基于FPGA主备倒换的电路设计与实现

谭 宇,姚亚峰,陈 登,霍兴华

(中国地质大学机械与电子信息学院,湖北武汉430074)

责任编辑:魏雨博

目前,主备倒换技术已广泛应用于数据通信领域。由于主备倒换技术的引入,提高了设备的可靠性。作为光接入网的局端设备OLT,通常也增加一个备用主控卡以作数据备份和冗余[1-3]处理。传统的主备倒换是通过两块主控卡上的CPU互相通信来控制主备倒换。其实现方法是通过主主控CPU不断地发送报文给备主控,当备主控有应答,并接收到主主控的主备倒换请求时,则执行主备倒换。但是在这种方式下,主控上的CPU需要启动一个轮询当前主控状态和外部控制指令的任务,这就延长了主备倒换时间,还加重了CPU的负担。在考虑以下情况:1)如果整个系统的CPU未完成初始化时,报文无法发送本主控的状态,从而导致主备状态是不确定的;2)如果系统在某个任务阻塞时,由于备主控没有接收到主主控发送的报文,于是就会误动作将备主控升级为主主控。为了改善传统方案中的这些缺陷,提出了一种基于FPGA硬件逻辑控制的优化方案。实践表明,基于FPGA的实现方案比传统的CPU通信方案在倒换速度及稳定性方面都有明显改善。

1 FPGA逻辑控制方案

本方法是通过在主控卡上增加FPGA芯片来承担主备之间的通信。其核心思想是:在主备之间预留3根线作为主备通信的物理接口,运用这3根线将主备启动过程中的各个状态按照一定的编码规则进行编码,通过读取编码来获取主备之间的状态信息。编码的引入,使得主控在启动过程中的各个状态是闭环的。这样一方面可以改善主备状态的不确定性,另外一方面可以提升主备倒换的时间和减小系统CPU的负担。

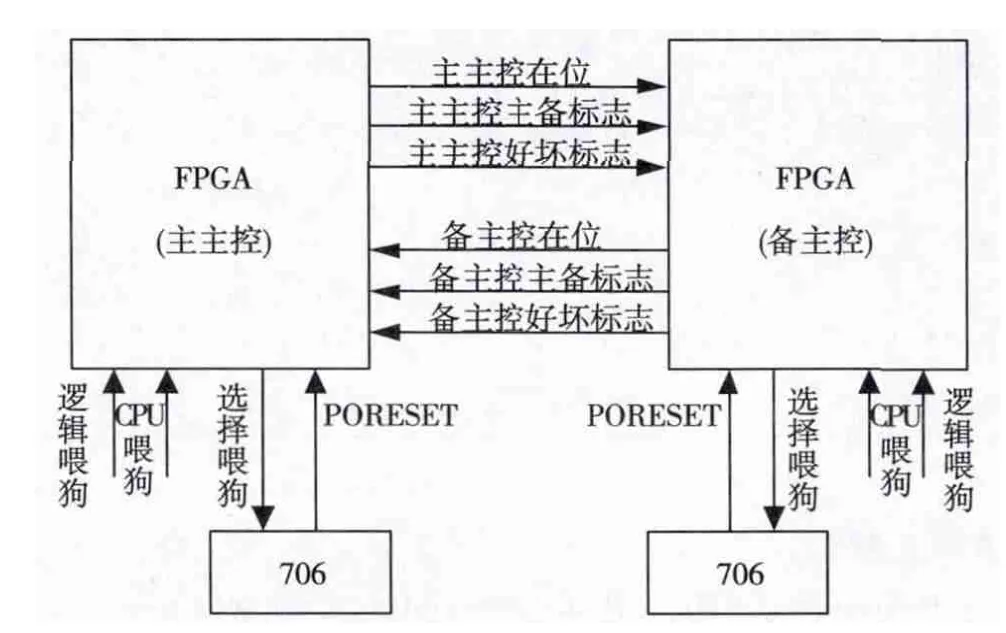

1.1 硬件架构

OLT设备中有12个槽位,主控卡槽位号分别为SLOT6和SLOT7。其中,SLOT6为默认主主控。两块主控卡之间有3根线用于主备的状态信息编码。其中,3根线分别表示为:主(备)主控在位、主(备)主控主备标志、主(备)主控好坏标志。复位芯片为MAX706,主控卡的复位模块在FPGA中完成。硬件设计原理图如图1所示。

图1 主备倒换硬件设计原理图

1.2 模块说明

1.2.1 I/O模块

主控卡上的FPGA芯片的I/O信号通过LBC总线传送到CPU;系统初始化完成后,CPU会通过LBC扫描FPGA上的所有I/O信息;另外,实时监控某些I/O的电平状态,然后发中断给CPU,CPU接到中断后会启动ISP,扫描被监控的I/O上的电平。涉及到主备倒换的I/O信号有主控卡的槽位ID信号、主备之间的心跳信号、主备之间的在位信号、主备之间的复位信号、主备之间的工作状态信号。

1.2.2 复位模块

主控卡的复位模块是在FPGA中完成的。上电时,通过MAX706输入给FPGA的复位信号,首先给CPU卡复位;当CPU初始化完成后,再通过LBC总线向FPGA写复位寄存器,完成复位过程。

1.2.3 看门狗模块

主控卡的看门狗模块是完成对CPU模块的监控,如果CPU模块“死机”,看门狗会执行主备倒换到备主控上,同时复位自己本主控系统。实现过程如下:

1)上电后,FPGA初始化所有寄存器的值,FPGA的喂狗信号开始输出周期性的脉冲。

2)如果检测包含初始化信息的寄存器为0,则FPGA输出给MAX706的看门狗信号由FPGA的喂狗信号提供;如果检测为1,则看门狗信号由CPU的喂狗信号提供。

3)如果看门狗失效,则会产生主复位信号PORESET。

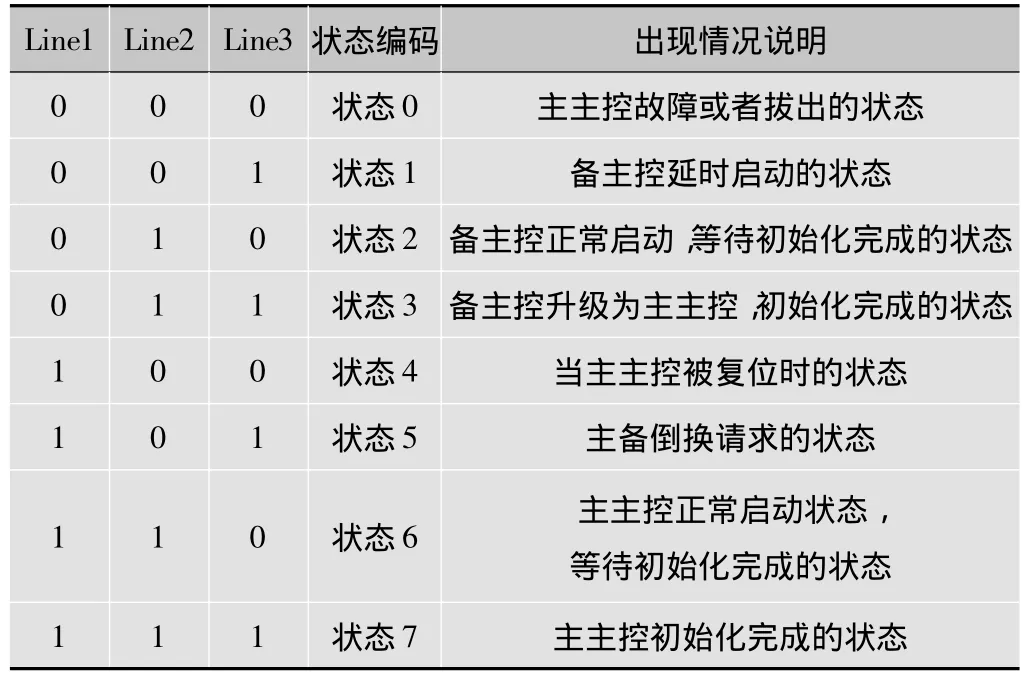

1.3 编码原则

两块主控卡之间的3根线可以组成8种状态编码。通过对这些编码赋予特殊的定义,当对方的FPGA监听和读取到主备互传的这些编码,上报给CPU,从而来实现主备状态快速传递。信号定义和编码规则如表1所示。

表1 信号编码规则

主/备控在位(Line1):主控卡的在位状态。1表示主控卡在位;0表示主控卡不在位。

主/备主控主备(Line2):主控卡的运行状态,用来指示本主控卡是否为主主控。1表示本卡为主主控卡;0表示本卡为备主控卡。

主/备主控好坏标志(Line3):周期性的心跳信号。1表示运行正常;0表示为初始化未完毕或者运行非正常。

1.4 主备倒换原理和实现

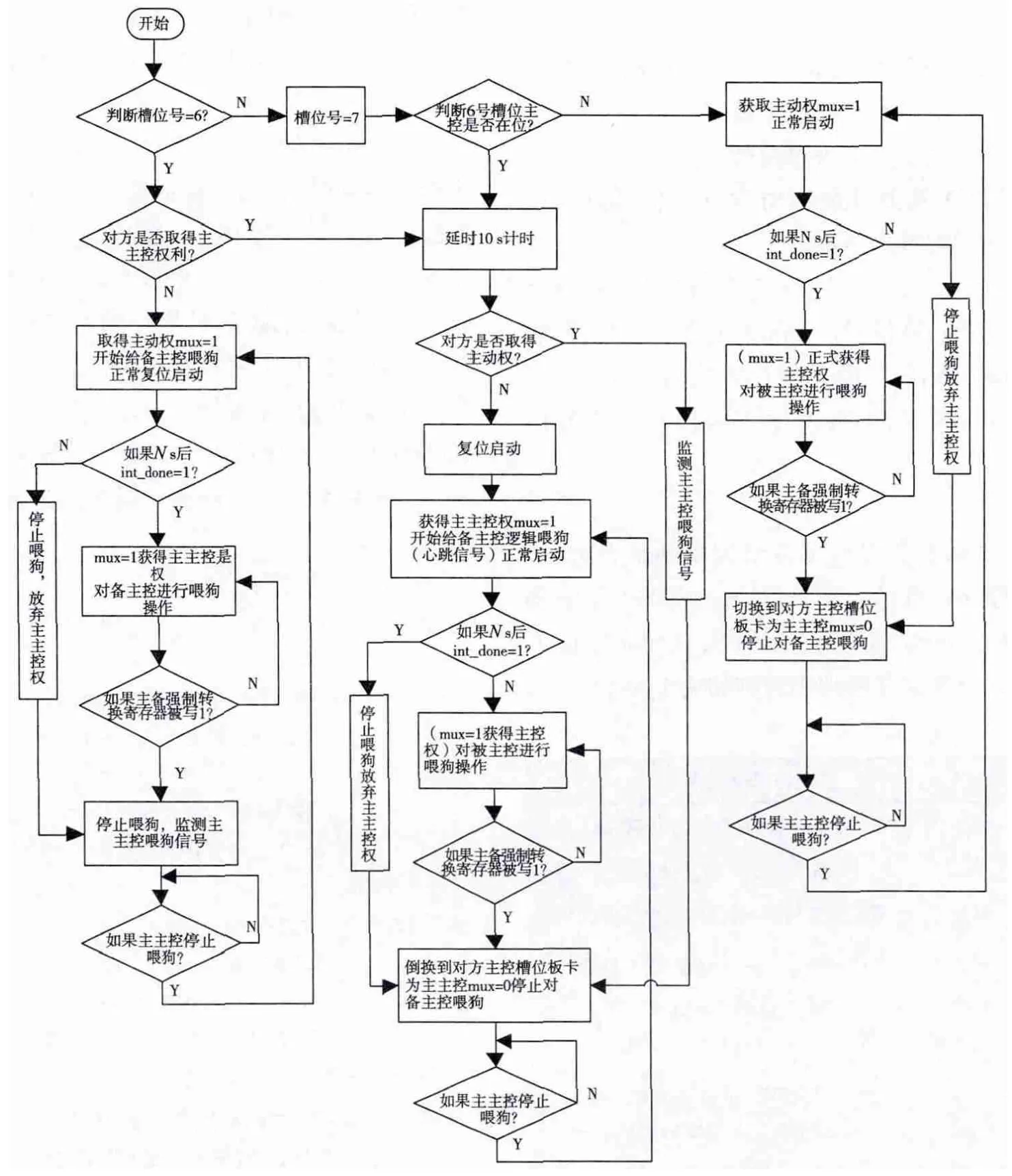

1.4.1 设备启动过程中的主备倒换

1)上电启动时,若FPGA检测到本主控处在6号槽位,而7号槽位没有主控卡时,则6号槽位主控按照正常初始化过程进行启动,当CPU完成初始化时,该主控就自动升级为主主控。

2)若FPGA检测到本主控处在7号槽位,而6号槽位没有主控卡时,则7号槽位的主控仍然按照正常初始化过程进行启动,整个启动过程同上。

3)若6号槽位的主控正常启动,完成初始化并获得主主控状态。与此同时,7号槽位的主控上电时,检测到备主控在位且处在7号槽位。这时,FPGA就需要控制本主控的启动时间,通过控制整个系统的复位状态,将本主控的启动时间延时10 s。当10 s延时到达后,7号槽位的主控通过主备之间的3根线判断6号槽位的主控已经升级到主主控状态时,7号槽位的主控就自动降为备主控。并一直处于监听主主控状态,当监听到主主控状态编码为复位状态(100),主备倒换请求状态(101),拔出(故障)状态(000)时,7号槽位主控就自动升级为主主控状态。

上电启动过程中状态关系如图2所示,逻辑框图如图3所示。

逻辑代码结构如下:

IF(备主控在位);

IF(备主控好);

IF(检测到备主控有CPU喂狗);

IF(备主控主备状态为主)本主控主备状态为备(高阻态);

ELSE本主控主备状态为主;

ELSE本主控主备状态为备(高阻态);

ELSE

IF(检测到主主控有CPU喂狗);

IF(备主控主备状态为备)本主控主备状态为主;

ELSE本主控主备状态为备(高阻态);

ELSE本主控主备状态为备(高阻态);

ELSE本主控主备状态为主;

1.4.2 设备运行过程中的主备倒换

图2 主控启动过程状态转移图

图3 主控启动过程逻辑框图

1)主动倒换:当后台主动发出指令要求系统主备倒换时,主主控进入主备倒换请求状态,当备主控监控到该请求时,升级为主主控状态,同时主主控自动降级为备主控状态。

2)自动倒换:当主主控出现故障或者拔出时,备主控检测到主主控处于该状态(000)时,备主控自动升级为主主控。

3)复位倒换:当主主控被复位时,主主控输出复位状态编码(100),当备主控检测到此状态编码后,自动升级为主主控状态。被复位后的主控按照备主控方式启动,并处于备主控监听状态(011)。

2 实验验证

验证方法:根据测试用例对OLT进行主控卡1+1冗余保护测试。正常数据业务收发时,执行主备倒换,观察数据业务是否正常。环境搭建拓扑如图4所示。

图4 测试拓扑图

2.1 常温环境测试

测试过程:

1)通过网管配置数据业务,测试仪通过ONU/OLT发送上下行数据,观察在OLT上联口和ONU的UNI口接收的流量,数据业务正常。

2)串口连接至主控制卡,show当前主控主备状态。

FP8680(config)#show slot status

Slot Present Status Cur-Type Bind-Type

6(Local)online active FP8680-SMC(M)FP8680-SMC

7 online active FP8680-SMC(S)FP8680-SMC

3)后台执行主备倒换。

FP8680(config)#switch-over

WARNING:Thiswill switch themaster and slave status!Continue?(y/n)[y]

Now themaster and slave status is change,pleasewait...

4)测试停止,观察数据业务丢包是否严重。流量测试如图5所示。

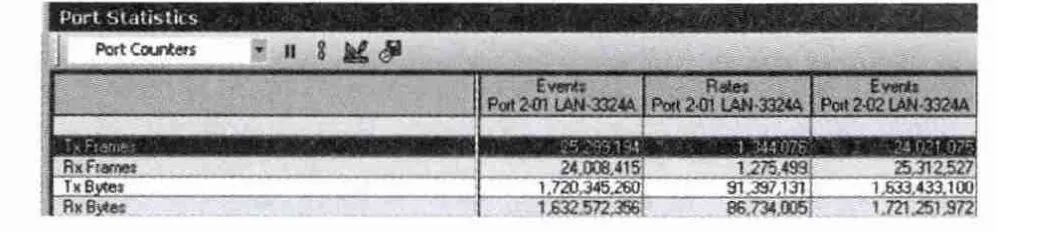

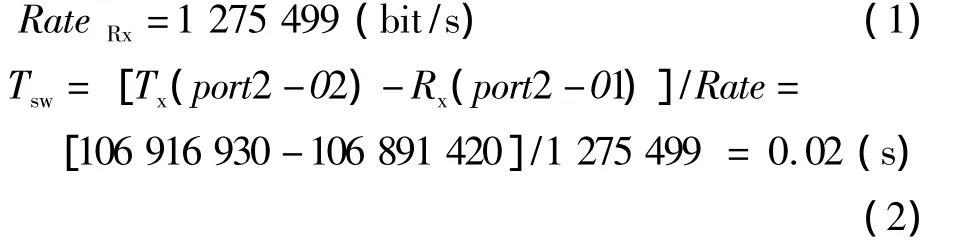

5)计算倒换时间

计算方法:倒换时间可以通过主备倒换过程中丢包数量和发送速率的比值来确定丢包时间。发送速率如图6所示。

图6 Smart bit流量发送速率(截图)

式中:RateRx为接收端速率,Tsw为倒换时间。

2.2 高低温环境测试

将OLT设备置于高低温测试箱,对主控进行主备倒换测试。目的是在高低温环境下,测试主控执行主备倒换的稳定性。

测试条件:

1)高低温冲击实验

高温40℃ ±5℃,持续4 h;

低温0℃ ±5℃,持续4 h;

2)高低温交变湿热实验

相对湿度为50%~60%。

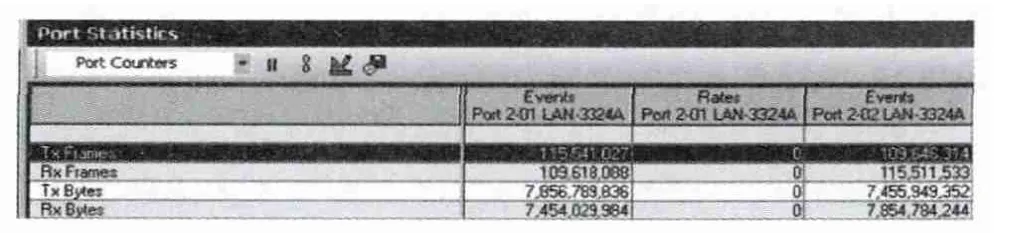

测试过程:重复2.1节测试实验。测试结果如图7所示。

图7 高低温环境下Smart bit流量测试结果(截图)

计算倒换时间

2.3 热插拔测试

对两块主控卡交替插拔50次,通过串口打印信息,观察主控卡都能自动完成主备倒换过程,并无出现数据流完全中断。

通过测试主备的倒换时间约为20 ms,远远少于传统方案(勉强临近电信50 ms[4])的标准。同时通过高低温环境测试和热插拔测试,并未发现不良情形,进一步保证了设备的稳定性。此结果说明了该方案实现了主备的无缝式倒换。

3 小结

本文从硬件逻辑设计的角度提出了基于FPGA实现的详细框架、过程和编码,将主控启动过程中状态信息采用编码的思想,对传统的主备倒换方案进行了优化设计和实验验证,较好地改善了主控启动时间慢,主备倒换误操作和主备倒换时间长的缺陷。该设计方案通过了设备量产和广电及电信运营商的开局测试,达到了广电和电信测试标准。

[1]李洁,黄婷熙,潘涛涛.高可靠性通信设备主备倒换软件实现方法[J].电视技术,2013,37(11):170-172.

[2]施世华,高西全,靳松杰,等.高可靠性通信设备的主备倒换设计[J].电子科技,2007(7):47-50.

[3]何先波,李志蜀,唐宁九,等.面向通信领域的主备倒换与数据同步技术[J].计算机应用,2005(10):2312-2314.

[4]孙立新.第三代移动通信技术[M].北京:人民邮电出版社,2000.