基于Verilog的VGA控制器

惠为君 沈兆军

摘 要:介绍了VGA的基本概念和有關协议,给出了VGA 行场扫描的时序图。基于verilog语言实现了VGA视频编码芯片ADV7123的控制器。测试表明,该控制器是有效的。

关键词:Verilog;VGA;控制器

中图分类号:TN911

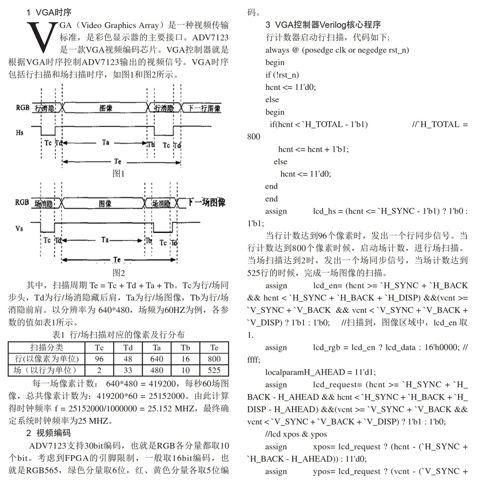

1 VGA时序

VGA(Video Graphics Array)是一种视频传输标准,是彩色显示器的主要接口。ADV7123是一款VGA视频编码芯片。VGA控制器就是根据VGA时序控制ADV7123输出的视频信号。VGA时序包括行扫描和场扫描时序,如图1和图2所示。

其中,扫描周期 Te = Tc + Td + Ta + Tb。Tc为行/场同步头,Td为行/场消隐藏后肩,Ta为行/场图像,Tb为行/场消隐前肩。以分辨率为 640*480,场频为60HZ为例,各参数的值如表1所示。

每一场像素计数: 640*480 = 419200,每秒60场图像,总共像素计数为:419200*60 = 25152000。由此计算得时钟频率 f = 25152000/1000000 = 25.152 MHZ,最终确定系统时钟频率为25 MHZ。

2 视频编码

ADV7123支持30bit编码,也就是RGB各分量都取10个bit。考虑到FPGA的引脚限制,一般取16bit编码,也就是RGB565,绿色分量取6位,红、黄色分量各取5位编码。

3 VGA控制器Verilog核心程序

行计数器启动行扫描,代码如下:

行列计数器值计数到有效图像数据(640*480)区域时候,控制器输出有效的16bit信号,驱动ADV7123。同时,输出有效的x、y坐标,读取该坐标对应的存储器中的二维图像信息。

4 VGA控制器验证

通过控制器控制可以在LCD显示屏上显示字符、RGB彩色图像、视频图像。显示字符时,在ROM中加载字模的mif文件。显示彩色图像时,先要提取彩色图像的R、G、B各分量,制成mif文件,然后,在ROM中分别加载各个分量的mif文件。视频图像的显示方法是把采集的视频按帧显示图像即可。如图3所示,为了验证设计,生成了两个模块,一个是提供时钟的PLL,PLL输出时钟为25MHZ。一个是控制存储字模数据ROM的模块lcd_display。Lcd_display读取两个ROM,ROM1中存放字符为:Hello World*^_^*,ROM2中存放的字符为:电子设计自动化。其中,英文字符的的尺寸为32*64,中文字符的宽度要求为英文字符的两倍,因此,中文字符的尺寸为64*64。为了简单起见,取两个ROM的宽度为64,深度都为512。字符在显示器水平方向的起始位置为64,英文字符竖直方向的起始位置为128,中文字符的竖直方向的起始位置为256。以中文字符为例,读取字符代码如下:

4 结束语

本文设计的控制器适用于VGA字符、图像和视频的显示控制,仿真和试验表明该设计是可靠的,控制器性能是稳定的。

参考文献:

[1]刘威,石彦杰,高博.基于FPGA的VGA显示模式识别[J].计算机工程与科学,2008(04):152-155.

[2]廖永清,丁旭昌.基于FPGA的VGA图像动态显示控制器的设计与实现[J].电视技术,2011(17):52-54.

[3]夏宇闻.Verilog数字系统设计教程[M].北京航空航天大学出版社,2008.

[4]姜世杰出,余红英.基于FPGA的VGA接口驱动技术[J].电子测试,2012 (12):42-45,29-32.

[5]袁堂青,张玉璘.基于FPGA的VGA汉字显示系统设计与实现[J].济南大学学报(自然科学版),2011(01).

作者简介:惠为君(1969.03-),男,硕士,信息学院讲师,主要从事电子信息方面的教学工。

作者单位:盐城工学院,江苏盐城 224051