一种智能化ARINC429通讯卡设计与实现

陈 磊,苗克坚,王毅航

(西北工业大学 计算机学院,陕西 西安 710072)

一种智能化ARINC429通讯卡设计与实现

陈 磊,苗克坚,王毅航

(西北工业大学 计算机学院,陕西 西安 710072)

介绍了一种基于ARM微处理器的ARINC429航空总线通讯卡的设计方法,以实现两发四收的信息控制。该设计以LPC3250作为嵌入式微处理器,采用DEI1016/BD429芯片组构建ARINC429总线通讯系统,为航空电子系统提供了高效可靠的通信平台。

ARM; ARINC429; LPC3250; DEI1016/BD429

ARINC429总线广泛用于航空电子系统内各设备间大量数据信息的传输[1]。传统的ARINC429通讯卡依赖通信平台处理机来完成控制与处理工作[2-3],增加了平台处理机的负担,降低了数据传输速率,系统可靠性及效率不高。为了解决这一工程难题,本文做了深入研究,结合现有研究成果[4-5],致力于设计一种新的通讯卡,提高通信板卡智能化水平,减轻系统通讯负担,降低协议通信的控制难度,为航空电子系统构筑一个可靠高效的ARINC429总线通信平台。

1 ARINC429通讯卡设计

通讯卡主要完成以下任务:完成两路ARINC429接收数据的串并转换;实现两路ARINC429发送数据的并串转换;支持中断方式、查询方式接收和发送数据。

目前常用的ARINC429收发器主要有DEI1016/BD429和HS3282/3182两种芯片组,本次设计采用DEI1016/BD429构建ARINC429总线通讯系统。DEI1016是美国DDC公司生产的ARINC429总线接口芯片,提供有标准航空串行数据和16 bit宽数据总线接口。

DEI1016在发送时按协议完成发送数据的并-串转换并发送;接收时完成电平转换并按协议完成接收数据的串-并转换;在初始化时进行数据格式、波特率、奇偶校验等设置。一块DEI1016芯片可实现一路ARINC429数据发送及两路ARINC429数据接收功能。

图1 通讯卡整体结构Fig. 1 Structure of the communication card

1.1 DEI1016的数据发送与接收

DEI1016的发送器电路包括一个发送缓存器和一个控制逻辑。发送缓存器是一个8*32 bit的FIFO,数据的载入由LD1和LD2 两个信号控制。LD1有效时载入第一个16位,LD2有效时载入第二个16位,而且在每个数据字载入过程中LD1必须在LD2之前到来。另外,数据载入时发送器是处于禁止状态的。而控制逻辑则允许ARM微处理器给发送器写数据块,并通过ARM微处理器使能发送器,即置ENTX信号有效来使该数据块自动发送出去。数据在TTL电平格式下,经过BD429电平转换然后发送出去。值得注意的是每8个数据字间的发送并不是连续的,而是具有由DEI1016自动产生的4个字时钟间隔时间。

ARINC429信号的接收通过接收字间隔时序电路采样产生一个数据字。接收采样频率是正常数据速率的10倍,以保证不会出现含混的数据字。采样得到的数据被存进一个32位的移位寄存器中,并由控制寄存器内容决定是否接收该字。数据字长度由控制寄存器的“WLSEL”确定。保持寄存器中的数据以2个16位字的形式放在数据总线上。数据应及时读出,以避免新的数据将原来的数据覆盖。读取数据时,先将接收选择线SEL拉低,且使能OE读出低字,再将SEL拉高并使能OE时读取高字。

1.2 DEI1016/BD429外围电路设计

BD429芯片为ARINC429的发送驱动器,与DEI1016配套使用。发送驱动器的作用是将ARINC429协议芯片送出的TTL逻辑电平转换为符合ARINC429协议信号电平要求的信号进行发送。设计应用电路如图2所示。

该应用电路中的两个68 pF的电容很重要,会影响到ARINC429信号上升和下降的斜率,容值过大会使斜率变小,反之容值过小会使斜率变大。

图2 DEI1016/BD429芯片组应用电路Fig. 2 Application circuit of DEI1016/BD429 chipset

在设计中采用DEI1016输出的429信号作为其输入信号,输出数据速率通DEI1016确定,而不采用SYNC、CLOCK和DATA信号相与的方法调整,因此直接把SYNC和CLOCK信号拉高。1MCK由16M晶振经CPLD分频给出,在CPLD逻辑中分频系数可调,因而数据速率在12. 5~100k之间可调。SEL信号直接连至微处理器的最低地址位A0,由地址的变化控制数据读取时的高低16位选择。MR信号控制由阻容复位电路实现。其余发送与接收控制信号如OE、LD等均与CPLD相连,由CPLD译码控制。

2 DEI1016/BD429与CPLD的接口设计

2.1 DEI1016/BD429与CPLD的接口电路设计

为了灵活实现ARINC429数据的发送与接收,采用一片CPLD芯片进行控制。在CPLD逻辑中应实现地址译码和时钟分频功能,完成对某路发送或接收及ARINC429协议时钟的设定;通过设置ARINC429协议控制字进行自检;对中断屏蔽或使能等。CPLD器件采用ALTERA公司的EPM3064A实现,该芯片具有3.3 V I/O特性,可容忍5 V,适合应用于5 V、3.3 V多电压应用的场合。由于LPC3250为3.3 V I/O特性,而所选用的ARINC429接口芯片DEI1016为单一5 V供电,所以需要对微处理器与ARINC429数据和地址总线进行电压转换。这里选用四片SN74LVC4245DBL驱动器来实现16 bit数据总线和地址总线的电压转换。由于地址总线是单向的,即只能由处理器到ARINC429接口芯片,故负责地址总线电压转换的两片SN74LVC4245-DBL芯片DIR引脚可以接死;而负责双向数据总线电压转换的两片SN74LVC4245-DBL芯片DIR脚则需要通过CPLD进行逻辑控制。

慢病毒介导的三种神经元谱系相关转录因子脑内转移治疗帕金森病的实验研究 ……………………………………………………………… 陈品,于波,罗雨,等 215

2.2 DEI1016/BD429与CPLD的接口逻辑设计

ARINC429通讯卡片选由LPC3250的CS1和地址BA11~BA4共同控制,即当CS1有效且BA( 11 to 4 )=“00000000”时选通,全译码,地址空间为E100 0000-E100 000F

1)数据发送逻辑设计

DEI1016是16位数据线,所以32位数据字必须分成两个16位写入, 而控制字只需一次写入即可。以下VHDL代码实现了对429数据发送的控制:

LD_1(0) <= '0' WHEN WR ='0' AND A=X"4" ELSE '1' ;--第1片429发送低字

LD_1(1) <= '0' WHEN WR ='0' AND A=X"5" ELSE '1' ;--第1片429发送高字

LDCW_1 <='0' WHEN WR ='0' AND A=X"6" ELSE '1' ; --装载控制字

ENTX_1 <= '0' WHEN WR ='0' AND (A=X"0" OR A=X"1")ELSE '1';--置使能发送有效

2)数据接收逻辑设计

本通信系统实现两发四收,4个接收通道接收到的数据放在各自独立的FIFO中。数据接收采用中断—查询方式实现,即由接口芯片DEI1016的DR信号有效产生中断,通知处理器有新的有效数据到达。由于四路接收通道共用一个中断,所以必须在CPLD逻辑中实现中断屏蔽,并在中断有效时可查询是哪一路接收通道引发的中断,对于中断的处理逻辑为

INT<=RDY_429_1(0)AND RDY_429_1(1)AND RDY_429_2(0)AND RDY_429_2(1);--中断信号处理

以上逻辑表明,4个接收通道中任一路有数据时都会引发中断,此时查询数据线,即可得出是哪一路接收引发的中断。

3 ARM固件程序设计

固件程序担任着通讯系统最基础最底层的工作,是硬件设备的灵魂,且由于硬件设备除了固件以外没有其它软件组成,所以固件也就决定着硬件设备的功能及性能。本系统中ARM固件中断源为一个六位的寄存器,高位到低位分别标志:第一路发送、第二路发送、第一片两路接收、第二片两路接收路接收。

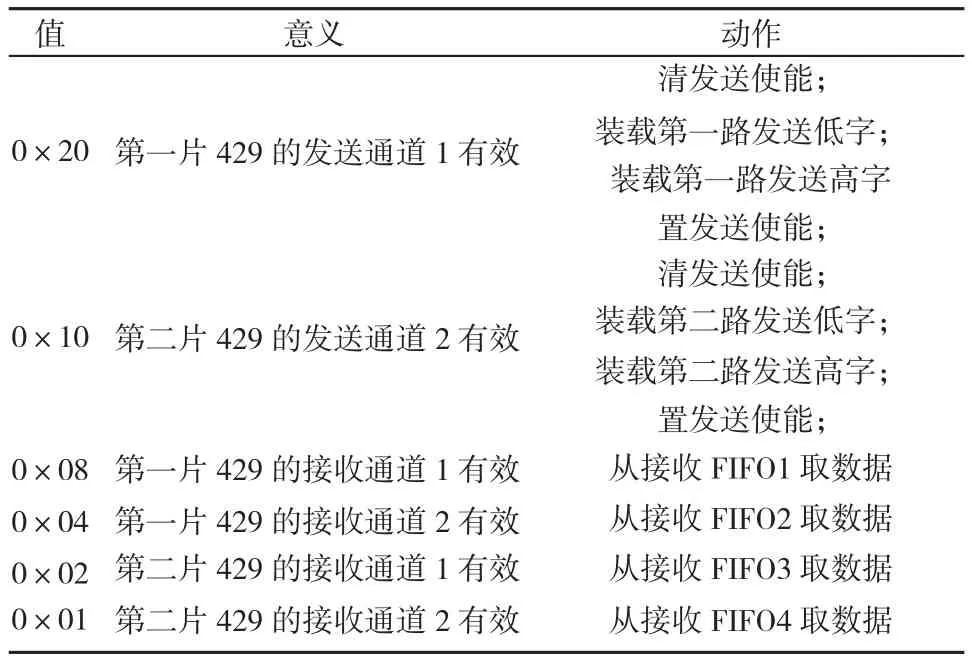

在本系统中,ARM固件程序需循环装载控制字,然后检查中断控制寄存器(PORT_CPLD_INT_SOURCE)的值,根据该值做具体的发送和接收操作。中断控制寄存器的取值及其对应的操作在表1中给出。

表1 中断控制寄存器值及其对应的操作Tab.1 Interrupt control register value and its corresponding action

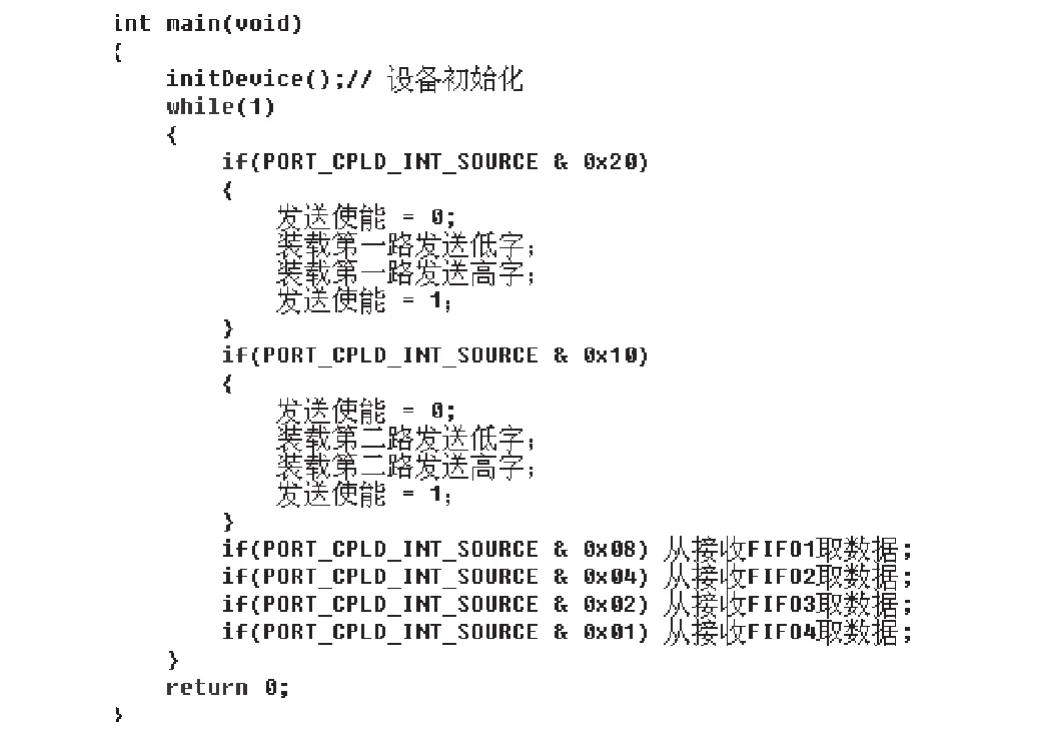

根据以上的分析阐述,给出程序的伪代码如图3所示。

4 结束语

ARINC429是航空电子系统中应用广泛的通信标准,而ARM微处理器在目前的测控领域也占有相当重要的位置,因此基于ARM微处理器的ARINC429通信系统无疑有着很好的适用范围和实用意义。同时,上述设计的接口通信板在多个不同的航空电子系统中成功的应用,证明了其正确性和高效性。

图3 ARM固件核心程序伪代码Fig. 3 Pseudo code of the ARM firmware kernel

[1] 王瑞敏,苗克坚,王亚妮.基于ARM处理器的ARINC429接口板软件设计[J].计算机工程与设计,2008(21):5471-5473.

WANG Rui-min,MIAO Ke-jian,WANG Ya-ni.Software design for ARINC429 interface card based on ARM microprocessor[J].Computer Engineering and De-sign,2008(21):5471-5473.

[2] 危淑敏,苗克坚,王毅航.基于DEI1016及BD429的ARINC429总线接口设计[J].长春理工大学学报:自然科学版,2008(1):111-114.

WEI Shu-min,MIAO Ke-jian,WANG Yi-hang.Design of ARINC429 PCI Communication In-terface Based On DEI101 6 and BD429[J].Journal of Changchun University of Science and Technology,Natural Science Edition,2008(1):111-114.

[3] 胡红明,苗克坚.基于DD-03282的ARINC429 PCI通信接口设计[J].计算机工程,2006(6):280-282.

HU Hong-ming,MIAO Ke-jian.Design of ARINIC429 PCI communication interface based on DD-03282[J].Computer Engineering,2006(6):280-282.

[4] 张小宁,苗克坚.基于ARM 微处理器的智能化PXI 总线扩展卡的设计[J],计算机应用,2007,27(3):709-711.

ZHANG Xiao-ning,MIAO Ke-jian,GAO Zhi-qiang.intellective PXI bus extended card design based on ARM microprocessor[J].Computer Application,2007,27(3):709-711.

[5]蒋谢芳,苗克坚,王长浩.基于嵌入式微处理器的ARINC429通信板卡的设计与实现[J].测控技术,2006(3):52-57.

JIANG Xie-fang,MIAO Ke-jian,WANG Chang-hao.Design and realization of communication card of ARINC429 based on embedded microprocessor[J].Computer Measurement and Control,2006(3):52-57

[6] 姬昕禹,马捷中,翟正军,等.基于ARINC429总线接口板卡的驱动程序设计与实现,计算机工程与设计,2007(14):3511-3514.

JI Xin-yu,MA Jie-zhong,ZHAI Zheng-jun,et al. Design and implement of device driver for ARINC-429 bus interface card[J].Computer Engineering and De-sign,2007(14):3511-3514.

[7] 曲建清,陈欣,吕迅竑.基于单片机和 CPLD 的ARINC429接口设计[J].计算机测量与控制,2009.17(3):558-560.

QU Jian-qing,CHEN Xin,LV Xun-hong. Interface design of ARINC429 based on single chip and CPLD[J].Computer Measurement and Control,2009,17(3):558-560.

[8] 张华强,赵剡,陈雨.基于 FPGA 的 ARINC429 通讯系统的设计与实现[J].通信技术,2010(12):4-6.

ZHANG Hua-qiang,ZHAO Yan,CHENG Yu. Design and implementation of ARINC429 commu-nication system based on FPGA[J].Communications Technology,2010(12)12:4-6.

Design and implementation of ARINC429 card based on LPC3250

CHEN Lei, MIAO Ke-jian, WANG Yi-hang

(College of Computer Science, Northwestern Polytechnical University, Xi’an 710072, China)

A method of ARINC 429 aero bus communication card based on ARM is introduced, in order to meet the information control of 2-Transmitter and 4-Receiver.The LPC3250 is used as embedded microprocessor in this design,at the same time DEI1016 and BD429 are used to construct an ARINC429 communication system which provides a communication platform with high efficiency and reliable to the avionics system.

ARM; ARINC429; LPC3250; DEI1016/BD429

TN918

A

1674-6236(2014)03-0171-03

2013–06–13 稿件编号:201306082

陈 磊(1986—),女,安徽淮北人,硕士研究生。研究方向:计算机测控与嵌入式计算。