基于ARM9+FPGA的便携式视频展示台的设计

梁皓东,张国平

(华中师范大学物理科学与技术学院,湖北武汉 430079)

基于ARM9+FPGA的便携式视频展示台的设计

梁皓东,张国平

(华中师范大学物理科学与技术学院,湖北武汉 430079)

目前市场上的便携式视频展示台普遍功耗大、成本高。针对此问题,基于对ARM9和FPGA的嵌入式实时图像处理平台的研究,提出了一种便携式视频展示台的设计方案。充分利用ARM9高性能、低功耗、低成本等特点,结合FPGA传输处理高分辨率图像的能力,设计了便携式视频展示台,其具有体积小、易携带、低功耗、低成本和高清显示等特点。此外,详细介绍了各模块Linux设备驱动的设计。

便携式视频展示台;嵌入式Linux;LCD控制器;SDRAM控制器;VGA时序

视频展示台是将实物、文稿、图片和过程等信息转换为图像信号输出在投影机、显示器上展示出来的一种演示设备。便携式视频展示台由于具有体积小、易于携带等优点,被广泛用于教学、大型会议及产品展示等场合,具有较大的研究前景。市场上的视频展示台普遍存在体积大、功耗高、价格贵等特点。本文采用并行嵌入式处理结构,设计了基于ARM9和FPGA的便携式视频展示台,在最大限度实现高分辨率图像实时处理与显示的同时,也使图像处理平台体积更小、功耗更低、成本更低。其内容主要包括高清图像的采集与存储,基于FPGA的SDRAM控制器的设计、ARM9和FPGA的通信方式以及各模块基于Linux平台的驱动设计。此视频展示台输出分辨率为1 024×768,60 Hz。

1 系统硬件设计

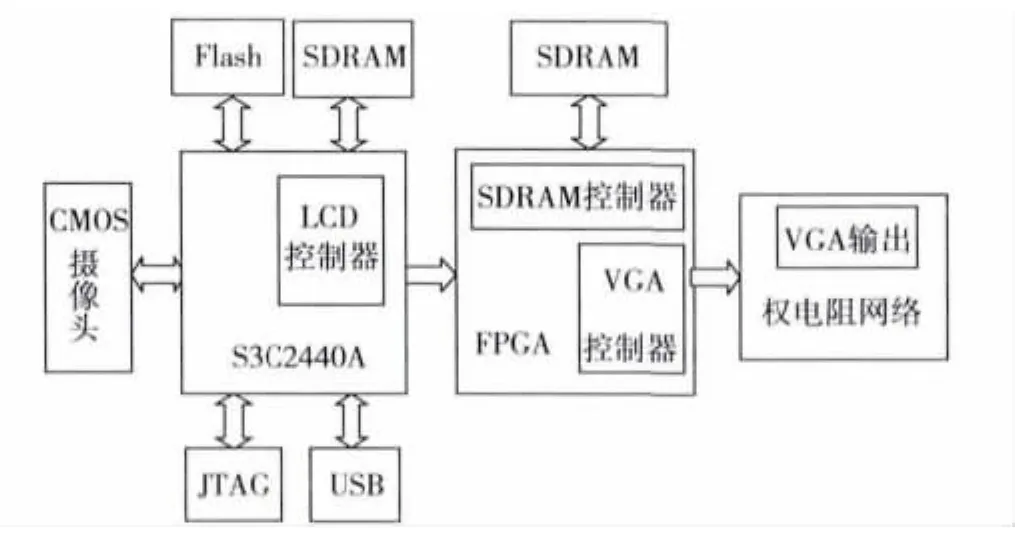

本便携式视频展示台的设计方案主要由两个模块构成:ARM9主控模块和FPGA从模块,如图1所示。ARM9主控模块采用具有极快读写速度的2片32 Mbit/s的SDRAM来保证Linux操作系统的流畅运行。主要功能是控制实物、文稿、图片和过程等视频信号的采集与存储,并把采集到的信号通过自身携带的LCD控制器并行送入FPGA从模块,这能很好地解决其他设计通过SPI总线串行传送图像导致的传输图片大小和速率受限的问题。

图1 硬件系统图

FPGA从模块的主要功能是把从LCD控制器传送过来的LCD接口信号送入高速SDRAM进行缓存,并通过SDRAM控制器把SDRAM中缓存的信号读出送入具有模数转换功能的权电阻网络中,将LCD接口信号转换成与VGA扫描逻辑相匹配的时序信号。

此外,为了给实物、文档、图片或者演示过程提供照明光源,本方案在OV9655摄像头旁边加了一圈LED小灯,并通过步进电机来控制照明小灯的高度,保证良好的采集视野,小灯的暗灭与高度变化采用按键来操作。硬件采用基于ARM9内核的三星S3C2440A处理器,其具有高性能、低功耗、低成本等特点。采用Altera公司的FPGA处理器EPC3T14417N,这是一款性能较好但成本较低的FPGA芯片,满足本设计图像数据的处理要求。

2ARM9主控模块

2.1 视频采集硬件接口及其分析

本部分采用摄像头接口控制单元CAMIF和I2C总线来控制和传输具有130万像素的OV9655摄像头采集实物、图片、文档或者过程等视频数据。选择CMOS传感器是因为它有功耗低、编程方便、成本低等优点。其主要引脚及功能描述如下:CAMCLKOUT是CPU输出的采样时钟,帧同步信号VSYNC、行同步信号HREF、像素时钟信号PCLK由OV9650内部产生,输入到S3C2440A芯片中,用于对图像采集进行控制[1]。此外,本设计充分利用了OV9655摄像头在Linux系统下的照相功能,可把实物或者文档的照片保存在Flash中进行回放。按照系统的要求,在配置摄像头信号输出模式时,选择P通道模式,输出数字RGB556信号。

2.2 视频采集驱动设计

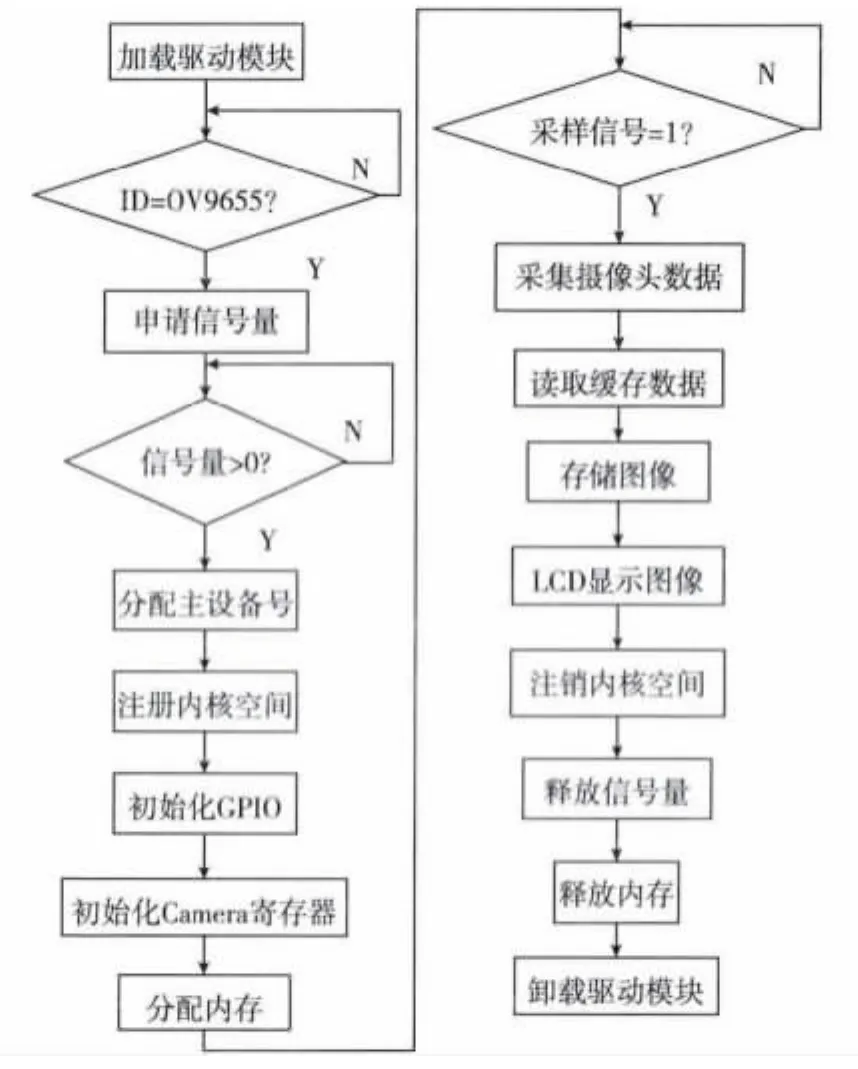

在 Linux 2.6.30/drivers/media/video 目录下建立OV9655.c、CAMERAIF.c 和 SCCB.c 三 个 源 文 件。OV9655.c负责设备初始化、与内核的通信;CAMERAIF.c管理摄像头寄存器的配置;SCCB.c用于I2C数据传送[2]。其驱动设计流程图如图2所示。

图2 摄像头驱动设计流程图

修改 Linux 2.6.30/drivers/media/video目录下的Kconfig、Makefile文件,添加新增摄像头驱动信息,把驱动设置为<M>类型,表示属于可加载型驱动以避免重新编译内核。编译源文件,生成3个加载模块:V9655.ko,CAMERAIF.ko 和 SCCB.ko,通过串口复制到开发板[3]。

3 FPGA从模块

3.1LCD控制器接口和VGA接口描述

S3C2440A带有LCD控制器,可以很方便地控制驱动扫描式接口的TFT显示。其主要功能引脚有:像素时钟信号引脚 VCLK/LCD,场同步信号引脚 VFRAME/VSYNC,行同步信号引脚 VLINE/HSYNC,VD[23:0]是RGB数字信号输出端口。LCD控制器能够传输图像数据和产生需要的控制信号、本设计中ARM9通过并行接口按照24位传送给FPGA.

VGA接口使用模拟RGB通道,逐点、逐行扫描,其关键信号有5个,分别是行同步信号、场同步信号、红色模拟信号、绿色模拟信号和篮色模拟信号[4]。

本设计引入FPGA从模块对高分辨率图像进行缓存,并根据VGA接口时序,把LCD接口信号转换成XVGA接口信号输出,同时可以利用FPGA内异步FIFO解决不同时钟域间通信速率匹配的问题。

3.2 FPGA从模块的设计

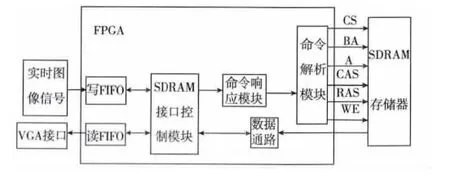

FPGA从模块的重点是实现对SDRAM的读写控制,本文借助FPGA内部的逻辑资源设计SDRAM控制器实现SDRAM读写控制,达到用SDRAM缓存高分辨率实时图像的目的。

3.2.1 SDRAM 控制器

本文借助FPGA片内的2个异步FIFO作为SDRAM的读写缓存。SDRAM控制器结构图如图3所示。

图3 SDRAM控制器结构图

SDRAM控制器主要由接口控制模块、数据通路模块与命令解析模块、命令响应模块组成[5]。各模块功能为:

1)接口控制模块:SDRAM初始化完成后,用户可以通过控制器的接口模块输入指令控制SDRAM数据的读写。

2)命令响应模块:响应外部读写要求并产生状态指令给命令解析模块。

3)命令解析模块:命令解析模块用于接收状态指令并生成合适的操作命令给SDRAM存储器。

4)数据通路模块:负责对SDRAM进行数据读写,使数据按照一定的时序有效地写入写出。

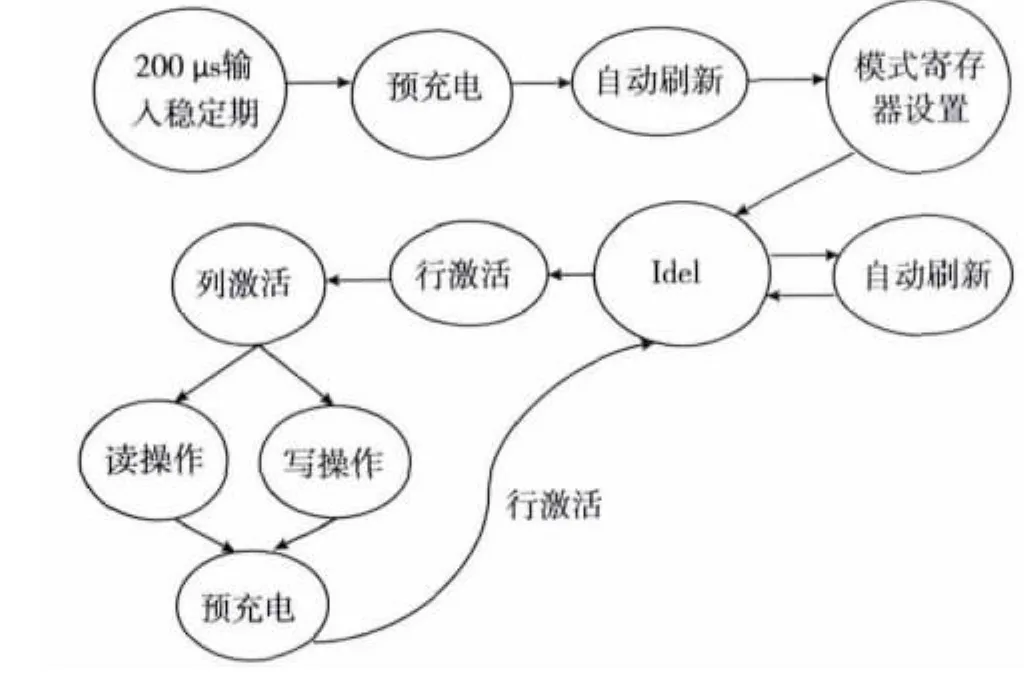

本方案的SDRAM采用页模式突发读写方式以提高SDRAM的数据吞吐量。根据SDRAM的寄存器特点,FPGA对SDRAM的读写控制如图4状态机所示[6]。FPGA从模块使用Verilog HDL硬件描述语言实现。

图4 SDRAM控制器状态机图

3.2.2 SDRAM控制器的实现及时序仿真

用Verilog语言在Quartus9.0的开发环境中进行仿真,并通过Modelsim工具对SDRAM的工作状况进行仿真验证[7],图5、图6、图7分别为SDRAM 在初始化、突发写、突发读时的工作时序。其中SDRAM_CMD包括:[4]CKE,[3]CS,[2]RAS,[1]CAS,[0]WE。初始化过程依次发出了将近200 μs的空闲状态、预充电、自动刷新和模式寄存器设置等命令;写过程依次发送激活、写命令以及一些时间要求(tRCD,tRCD,tRP);读过程依次发出激活、读命令以及一些时间要求(tRCD,CAS Latency,tAC,tRP)。

图5 SDRAM初始化时序时序仿真图(截图)

3.3 VGA驱动设计方案

图6 SDRAM写时序写时序仿真图(截图)

图7 SDRAM读时序仿真图(截图)

在FPGA从模块中,把缓存在SDRAM中的LCD接口信号送到FPGA片外的权电阻网络进行模数转换就能送往VGA接口显示。VGA显示是借用了S3C2440自带的LCD控制器功能实现的,只要根据VGA时序修改LCD控制器相关寄存器即可,这和普通的TFT液晶屏的驱动类似,此方式在很大层面上降低了VGA驱动开发的难度。

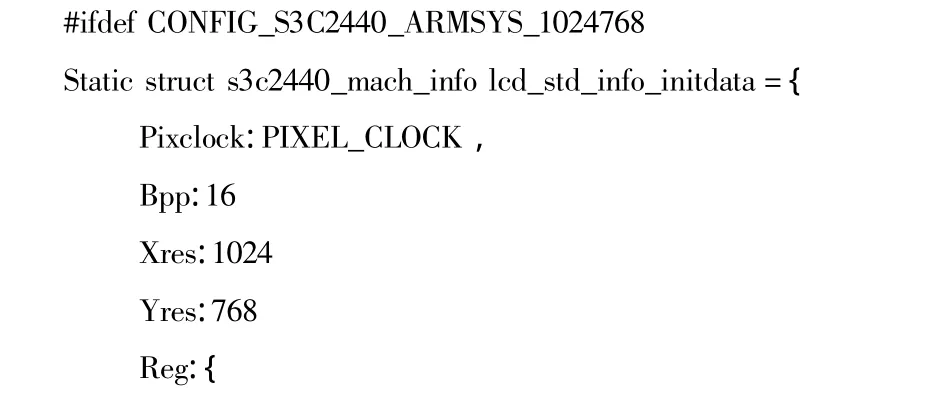

在本设计中S3C2440A的HCLK=100 MHz,VCLK=40 MHz,根据公式VCLK=HCLK/[(CLKVAL+1)×2],故需设置CLKVAL=0.25。VSYNC(帧频)的计算式为Frame_Rate=1/{[(VSPW+1)+(VBPD+1)+(LINEVAL+1)+(VFPD+1)]×[(HSPW+1)+(HBPD+1)+(HFPD+1)+(HOZVAL+1)]×[2×(CLKVAL+1)/(HCLK)]},则帧频为25.78 Hz,经过 FPGA 从模块的SDRAM高速缓存后,帧频可以达到60 Hz,分辨率是1 024×768。根据XVGA显示时序特点,配置S3C2440A的 LCD 控制寄存器 LCDCON1 ~ LCDCON5[8],就能实XVGA输出。相关寄存器设置如下LCD初始化代码所示。

由于Linux2.6.30内核已经很好地支持了LCD显示,因此,驱动并不需要重新编写,只要进行适当的修改。打开内核源代码,找到arch/arm/mach-s3c2440/machsmdk2440.c文件,修改LCD的初始化代码,包括寄存器的初始值、LCD的长宽等。LCD初始化代码修改部分如下所示:

修改好LCD初始化代码后,重新编译内核并生成内核镜像zImage,然后复制内核镜像zImage到/tftpboot/目录中。

4 系统效果测试验证

编译内核并生成内核镜像,然后将内核镜像移植入本便携式显示系统开发板中。将便携式显示系统与投影仪相连接,对本便携式显示系统进行测试论证。图8是本便携式视频展示台的投影效果验证截图,输出分辨率为1 024×768,60 Hz。通过观察测试结果,本方案切实可行,对实物、图片、文档或者过程的显示效果清晰,无抖动、无卡顿。

图8 便携式视频展示台的效果(截图)

5 小结

根据市场对视频展示台的大量需求但价格贵、功耗高的现状,提出了基于ARM9+FPGA的便携式视频展示台的设计方案。本方案充分发挥ARM和FPGA各自的特性,在实现便携式视频展示台体积小、低成本和低功耗的基础上,最大限度地实现图像的高清流畅显示。ARM9主控制模块利用自身携带的Camera接口和LCD控制器,实现了高清图像的采集和图像数据在ARM9主控模块和FPGA从模块模块之间的并行传输,提高了传输速度。FPGA从模块设计了一种SDRAM控制器,实现了高分辨率图像实时显示,也解决了在多个时钟域间进行信号通信的问题。方案采用模块化的设计原则,降低了开发成本和难度。

:

[1]张挺飞,樊永生,孙凌云.基于FPGA+ARM的智能图像门控系统[J].电视技术,2012,36(17):156-158.

[2]樊围栋,石红瑞,张健.嵌入式LINUX下CMOS摄像头驱动的设计与实现[J].工业仪表与自动化装置,2010(3):68-70.

[3]李亚峰,欧文盛.ARM嵌人式Linux系统开发从入门到精通[M].北京:清华大学出版社,2007.

[4]廖永清,丁旭昌,付建国,等.基于FPGA的VGA图像动态显示控制器的设计与实现[J].电视技术,2011,35(17):52-54.

[5]刘冬,焦明华,程飞龙.基于可编程逻辑器件的高速SDRAM控制器的实现[J].电脑知识与技术,2012,32(8):7816-7825.

[6]侯宏录,张文芳.基于FPGA的SDRAM 控制器设计方案[J].兵工自动化,2012,31(2):57-60.

[7]向厚振,张志杰,王鹏.基于FPGA视频和图像处理系统的FIFO缓存技术[J].电视技术,2012,36(9):41-43.

[8]尹柱霞,郑喜凤,于洪涛.ARM+FPGA控制的LED脱机屏系统设计[J].液晶与显示,2010,25(2):262-266.

Design of Portable Video Showcase Based on ARM9 and FPGA

LIANG Haodong,ZHANG Guoping

(School of Physics and Technology ,Central China Normal University,Wuhan 430079,China)

Currently,portable video showcases on the market usually have big energy consumption and high cost.To solve this problem,a new kind of portable video showcase based on ARM9 and FPGA embedded real-time image processing platform is put forward.ARM9’s high performance,low power consumption,low cost and other characteristics are taken full advantage in this scheme.As the ability of FPGA which can transport and process high-resolution images is combined,the designed portable video showcase have some characteristics,such as small,easy to carry,low energy consumption,low cost,high definition display and so on.Additionally,the Linux device driver design of each module is discussed in detail.

portable video showcase;Linux;LCD controller;SDRAM controller;VGA timing

TP302.1;TP391

A

【本文献信息】梁皓东,张国平.基于ARM9+FPGA的便携式视频展示台的设计[J].电视技术,2014,38(3).

湖北省自然科学基金项目(2012FFC023)

梁皓东(1988— ),硕士生,主研嵌入式系统设计,嵌入式linux驱动开发;

张国平(1969— ),教授,博士生导师,主研光通信、光电子技术、图像处理、认知无线电。

责任编辑:魏雨博

2013-06-26