一种软硬件协同的WMA解码器的设计

朱彩霞

(淮安信息职业技术学院 电子工程学院,江苏 淮安 223003)

0 引言

随着人们对于便携播放的需求越来越高和集成电路生产工艺的越来越精密,采用软硬件协调的方法实现超低功耗音频解码已成为一种趋势。目前,大部分的MP3解码和WMA解码都是使用DSP实现,该方法的缺点是软件开发难度大、功耗也比较大。采用纯硬件实现的缺点在于格式扩展不方便、设计周期长和文件兼容性不够。ARM7TDMI具有成本低、功耗低、代码密度高和容易开发等特点。硬件设计具有低功耗、低成本等优点,其缺点是一旦生产就不可更改,所以一般设计都是把没有兼容性需求、计算量大的部分采用硬件设计,而有兼容性需求的部分采用软件设计[1]。

1 WMA 简介

WMA是微软公司提出的一种音频标准,是Microsoft Windows Media技术中的一部分,它包含了对音频格式的一个完整定义,包括音频编码和加密。相比于MP3,它具有更好的高频音质和更低的压缩率,相比于AAC,它具有更高的接受度[2],又因为WMA具有DRM版权保护,所以具有更好的市场价值。

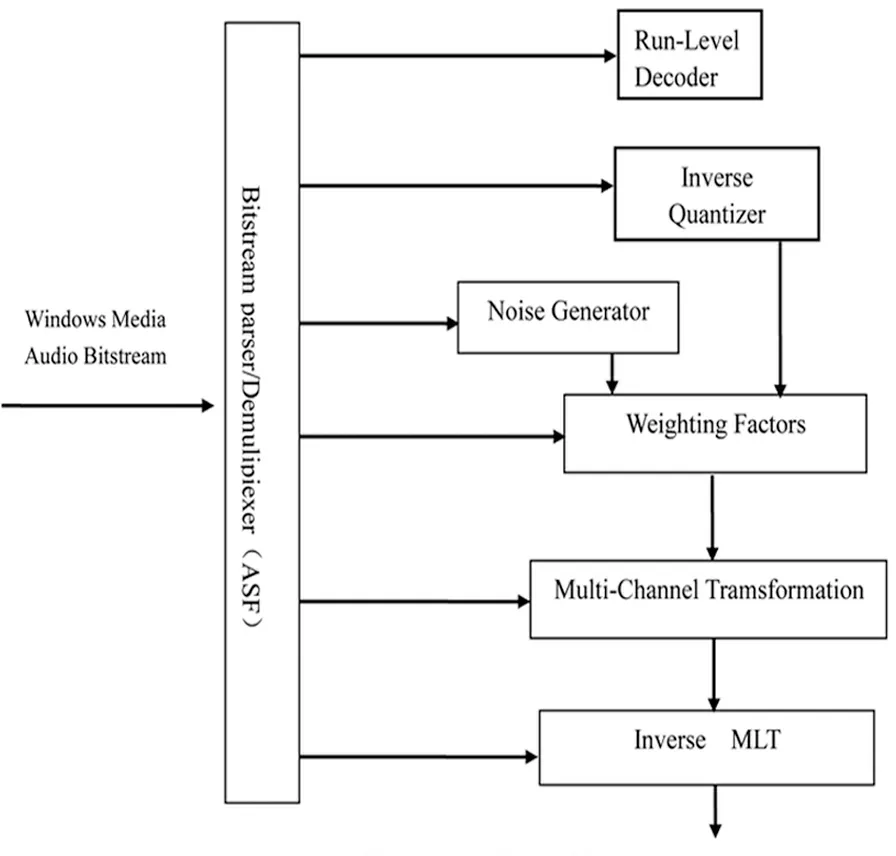

图1给出了WMA的解码过程,通过游程解码(Run-Level Decoder)和控制信息解码得到残差系数,反量化(Inverse Quantizer)后得到频域系数,噪声产生模块用于生成舒适噪声以改善频域过于集中时候的音质,多声道变换得到立体声的双声道单独系数,最后通过反重叠变换(Inverse MLT)得到时域音频信号[3]。

图1 WMA的解码过程

在图1中,Run-Level Decoder和Inverse MLT部分采用硬件实现,其它部分采用软件实现。Run-Level Decoder的运算单位都是BIT,ARM7的指令运算单位都是字节,用软件的方式会浪费功耗。Inverse MLT 类似FFT运算,该步骤在整个WMA解码中占大约40%的MIPS,采用硬件会大大减少功耗[4]。

2 解码器设计

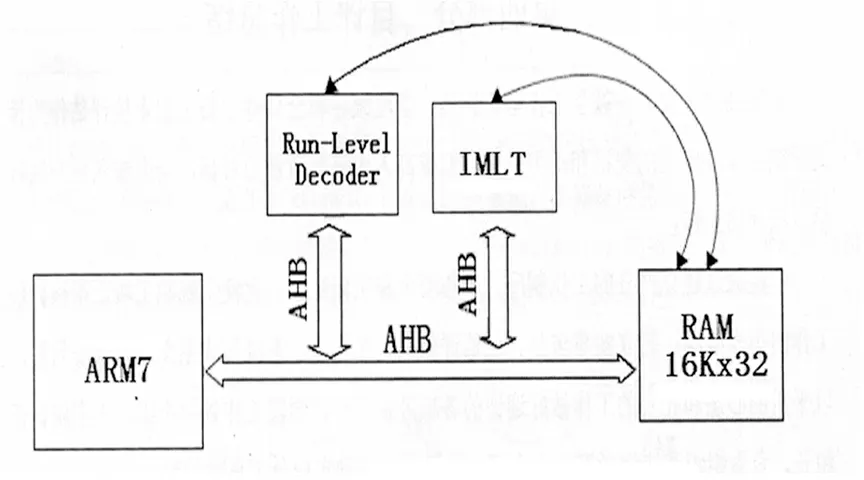

WMA解码的设计过程如图2所示。

图2 WMA解码的设计图

ARM7上运行的系统软件采用UCOS-II + UCFS,采用FAT32文件系统,WMA存储在SD卡中,解码器首先读出WMA文件,进行ASF头解析,判断其是否为正确的WMA文件,如果是,则继续解析ASF头、Packet、Frame和SubFrame等。

2.1 游程解码(Run-Level Decoder)

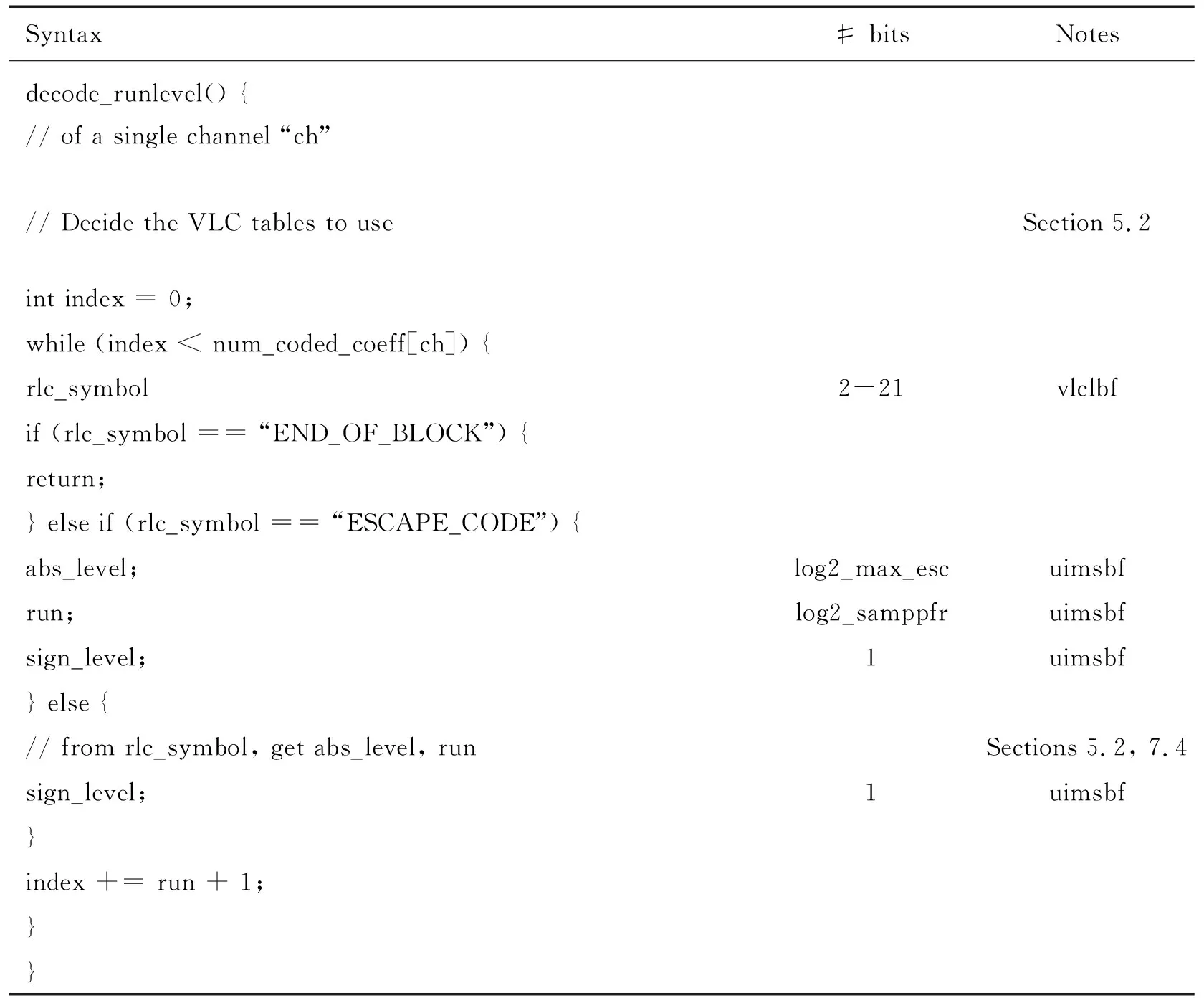

游程解码的读码流文件的过程如表1所示。

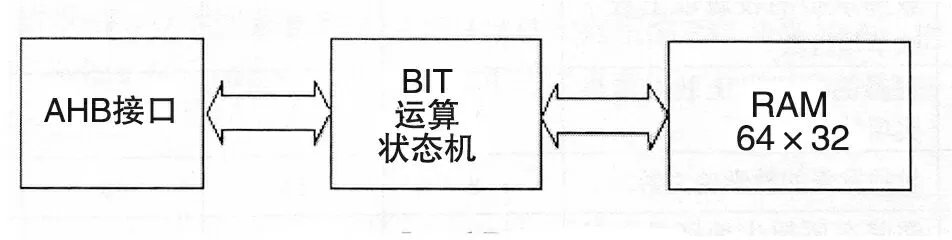

读比特的过程和游程解码VLC采用硬件设计,RLD解码器具有两种功能:一种是ShowBits和GetBits,ShowBits是查看nLength长度比特的数值,不移动硬件bitstream的指针,GetBits是读取nLength长度比特的数值并且移动硬件bitstream的指针;另一种功能是自动解码VLC的系数,解码系数自动写到SRAM。

在解码WMA文件时,首先读出SD卡中的WMA文件,因为WMA文件是ASF格式封装的,而MP3/FLAC/APE等文件都不是ASF文件,所以通过文件前四个字节可以检测文件是否确实是WMA格式的文件,防止错误文件解码。正确文件解码开始首先通过AHB填写256个字节到RLD的内部RAM,称为初始化过程。

读比特的过程如下:

uint_32 bs_read( sint_32 i_count )

{

DEC_BSI_UVLC_CTL_REG = (4<<6) | (i_count<<1) | 1 ;

do{

status = DEC_BSI_UVLC_STA_REG ;

}while( (status&1)==0) ;

return (status>>8) ;

}

uint_32 bs_show( sint_32 i_count )

{

DEC_BSI_UVLC_CTL_REG = (5<<6) | (i_count<<1) | 1 ;

do{

status = DEC_BSI_UVLC_STA_REG ;

}while( (status&1)==0) ;

return (status>>8) ;

}

表1 游程解码语法描述

Run-Level Decoder解码的流程如图3所示。

图3 Run-Level Decoder解码

首先CPU通过AHB接口填写256个字节数据到RLD的内部RAM,ShowBits和GetBits时,只需要配置一个寄存器,然后读取状态寄存器,内部运算完成后,读取数据寄存器的内容,每次最多读取24Bit;

在残差系数VLD解码时,解码过程不需要CPU干涉,由CPU配置num_coded_coeff参数到寄存器,然后启动VLD解码器,软件处于等待状态,如果256个字节数据用完,内部硬件设置标志位并暂停解码,CPU根据状态寄存器标志位重新填写256个字节,直到硬件解码完毕。VLD硬件解码首先初始化RAM输出,全部写0,然后将解码数据写到RAM中,由CPU来读取。

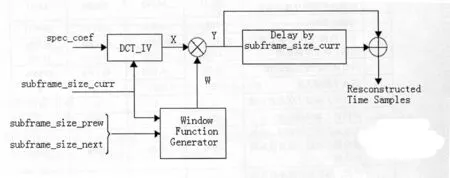

LMIT解码功能示意图见图4。

图4 IMLT解码功能示意图

2.2 IMLT解码

IMLT解码包含两个部分,DCT-IV和加窗计算。其中DCT-IV的计算是主要部分,使用了两个模块,IMLT根据CPU配置输入和输出的RAM地址,到系统RAM中读取输入,把DCT-IV计算后的结果写到输入RAM中,加窗计算从输出RAM的读取数据,计算完成后写回输出RAM。

DCT-IV的数学表达如下:

for0≤N<2n

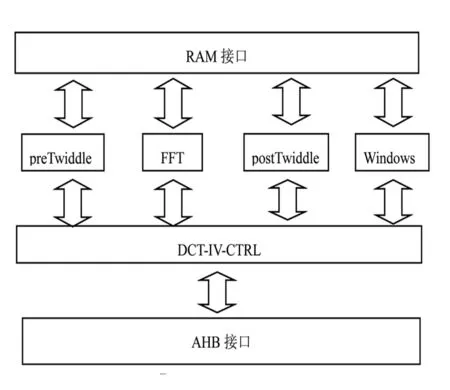

在计算的时候采用快速算法,首先进行preTwiddle,该模块是把输入数据进行FFT转换,计算复数输入,然后继续FFT运算,最后调用postTwiddle把FFT运算的结果转换为DCT-IV的输出,这些运算的中间结果都存储输出RAM中。

图5为IMLT硬件解码图,其中DCT_IV_CTRL是总体控制模块,负责和CPU交互,模块内部包含解码控制状态机,用于启动和停止四个流程的模块,在四个模块的工作全部完成后,产生中断通知CPU。四个模块都是采用状态机设计,每个模块之间没有关系,数据的存取都是来自RAM,这样可以最大限度的实现模块化设计。

图5 IMLT硬件解码图

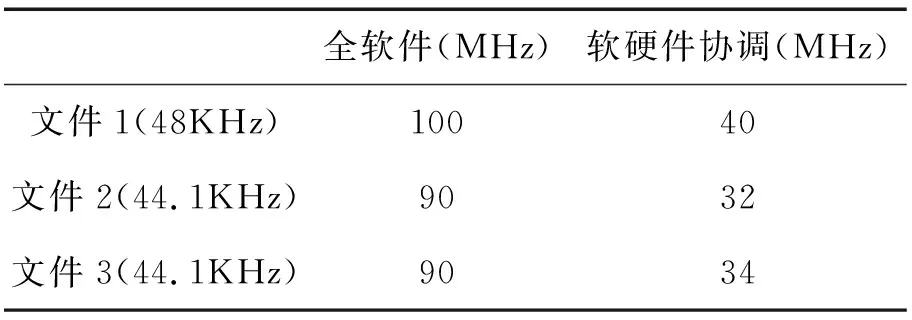

3 实验结果

实验过程中测试了大约10个文件,每个文件大约在4分钟,以对ARM7的时钟需求为分析标准,实验分析的结果如表2所示。芯片功耗在同等面积下与芯片工作频率的成正比,降低芯片工作频率是优化功耗最快的方法,该项设计达到了降低系统功耗的目的。

表2 硬件优化比较

4 结束语

本文采用ARM7为CPU,结合游程解码和DCT-IV硬件计算单元,降低WMA解码的功耗,为实现便携式音频解码SOC提供了一种开发速度快、可扩展性强的方法。另外,在后续的研究中,音频格式MP3/FLAC/APE等解码将全部共享RAM,因此在多格式音频解码时,该方法能够更好地降低系统成本。

参考文献:

[1] Charles D,Murphy,K.Anandakumar.Real-Time MPEG-1 Audio Coding and Decoding on a DSP Chip[J].Trans.on Consumer Electronics,1997,43(1):347-353.

[2] 周锦峰,倪光南.低功耗MP3解码器设计及其可测性报告[D].北京:中国科学院计算技术研究所,2003.

[3] 张海滨,李挥.基于S3C2410的WMA开源解码程序优化[J].计算机工程与设计,2009,30(1):13-15.

[4] Pramod,Kumar,Meher.LUT optimization for memory-based computation[J].IEEE Transaction on Circuits and System,2010,57(4):285-289.