一种基于改进型游程编码的FPGA动态重构方法

邵 龙

(中国电子科技集团公司第十研究所,成都 610036)

一种基于改进型游程编码的FPGA动态重构方法

邵龙*

(中国电子科技集团公司第十研究所,成都 610036)

摘要:在分析传统FPGA动态重构方法性能缺陷的基础上,创新性的提出了基于改进型游程编码的FPGA动态重构方法,并详细介绍了该方法的设计实现。与传统FPGA动态重构方法对比测试结果表明,基于改进型游程编码的FPGA动态重构方法不仅可以显著提高FPGA动态重构的速度,而且可以降低对程序存储器容量要求。目前,该技术已在重大工程项目中得到应用。

关键词:FPGA;动态重构;全局重构;游程编码;重构速度

FPGA 动态重构是指切换FPGA其全部或部分逻辑资源功能的应用方法[1-3]。FPGA动态重构可分为全局重构和部分重构。全局重构是指重新配置FPGA的全部逻辑,重构前后电路相互独立,没有关联。部分重构是指重新配置FPGA 的部分区域,重构过程中,FPGA未重构部分的工作状态不受影响[4-5]。

目前,实现FPGA全局重构比较通用的方法有3种:方法1通过DSP或其他CPU读取存储器中的bit文件对FPGA进行串行加载或并行加载[4],但重构速度一般很低,不能实现状态高速切换;方法2是使用Xilinx 公司的专用配置芯片XCFxxP系列[6],但由于该系列配置芯片存储容量有限,对于功能复杂的系统,FPGA的软件版本多,需要多片专用配置芯片,不能适应小型化的要求;方法3是基于CPLD的FPGA快速动态重构[7],克服了方法1和方法2的缺点,是在实际工程应用中FPGA动态重构速度最快的方法。但随着FPGA芯片规模增大,实现的功能也越来越复杂,bit文件大小也不断增加,方案3在某些场景下已经逐渐不能满足对重构速度的要求。本文在方案3的基础上,提出了采用改进型游程编码进一步提高FPGA动态重构速度的方法。

1 基于CPLD的FPGA快速动态重构

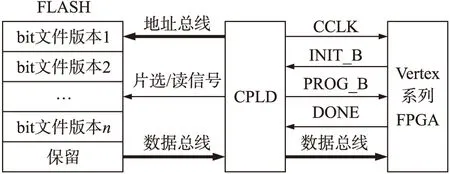

基于CPLD的FPGA快速动态重构工作原理框图如所图1示。FPGA被配置为被动并行加载模式,CPLD接收到bit文件版本切换信号后,读取对应的bit文件并送入FPGA的被动并行加载数据端口D[7:0],完成对FPGA的加载。

基于CPLD的FPGA快速动态重构流程如图2所示。首先拉低FPGA的PROG_B管脚一段时间再拉高FPGA的PROG_B管脚使FPGA复位,以清除配置存储器;接着,等待FPGA的INIT_B管脚变高,CPLD开始从FLASH相应的地址读取bit文件数据写入FPGA的被动并行加载数据端口D[7:0];最后,待bit文件全部写入FPGA的D[7:0]端口后,等待FPGA的DONE管脚变高,如果在超时以前变高,则FPGA重构成功,FPGA进入正常工作状态,CPLD将FPGA重构标志寄存器置为成功,否则FPGA重构失败,CPLD将FPGA重构标志寄存器置为失败。

图1 基于CPLD的FPGA快速动态重构原理框图

图2 基于CPLD的FPGA快速动态重构流程图

基于CPLD的FPGA快速动态重构方法具有较高的动态重构速度,但是特定场景下重构速度还是不能满足系统要求,分析发现其重构速度的瓶颈是FLASH的读取时间[5],而读取时间主要与FLASH芯片类型和FPGA程序文件的大小有关。因此要提高重构速度,要么选用速度更快的FLASH芯片,要么减小存储在FLASH中的FPGA程序文件的大小。选用速度更快的FLASH芯片成本较高,而且不适用已有设备,即使更换速度更快的FLASH芯片,还是可通过减小存储在FLASH中的FPGA程序文件的大小进一步提高重构速度,因此,减小存储在FLASH中的FPGA程序文件的大小的方法从经济和技术角度具有更广泛的实用性。无损压缩FPGA的bit文件正是减小存储在FLASH中的FPGA程序文件大小最直接的方法。

2 改进型游程编码的FPGA动态重构

游程编码是一种简单、易于实现无损压缩算法。游程编码的原理十分简单:将一行中数值相同的相邻点用一个计数字节和一个表示该数据值的数据字节来代替[8]。如果连续相同的字节很多,游程编码具有很高的压缩效率,但是孤立字节(与前后相邻字节值均不同的字节)会导致增加一个字节(长度字节)开销,影响压缩效率。

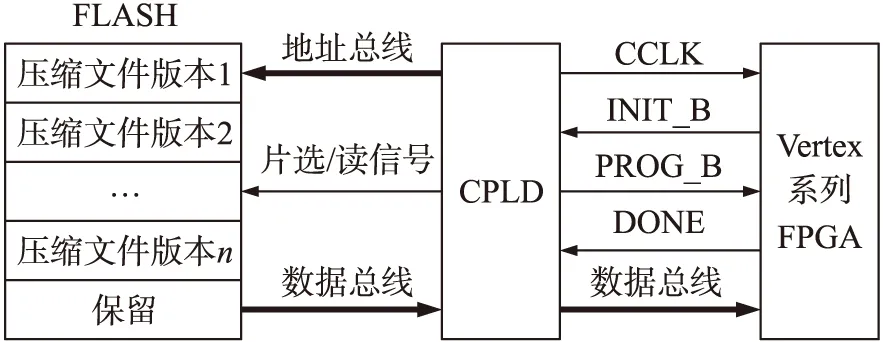

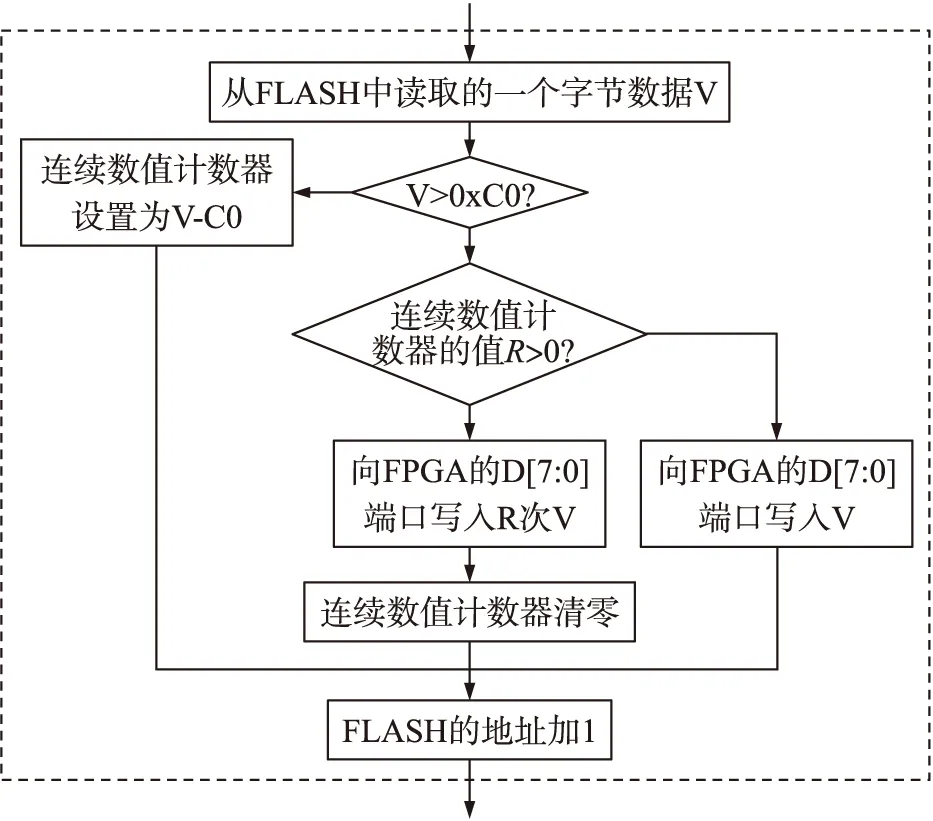

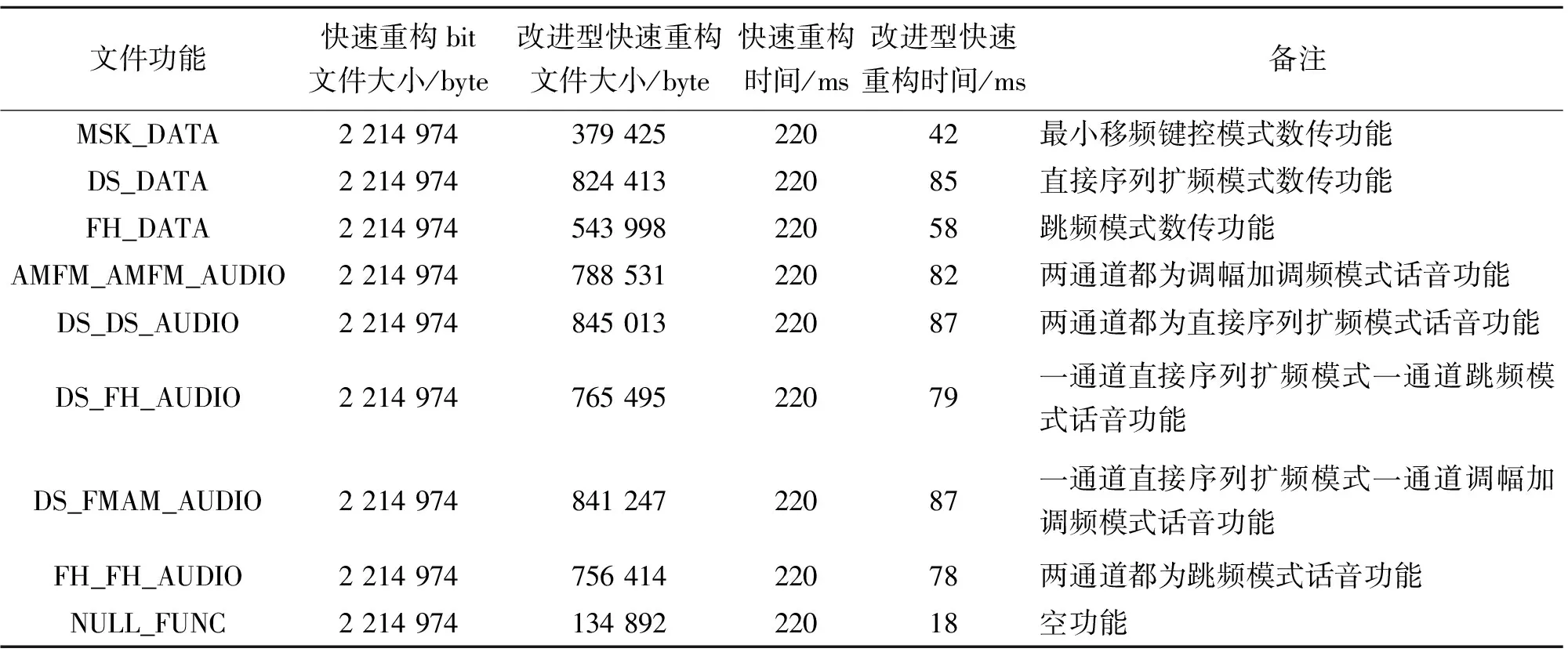

为了减小孤立字节对压缩效率的影响,改进型游程编码的长度字节用C0+N(N为连续相同字节的个数,当N>63时需要分多次压缩),对于值为YZ的孤立字节,只有当YZ≥C0时,才插入长度字节C1,编码数据为C1YZ,当YZ 基于改进型游程编码的FPGA动态重构相对于基于CPLD的FPGA快速动态重构主要不同就是存储在FLASH中的bit文件变成了经过改进型游程编码编码后的压缩文件,原理框图如图3所示。FPGA被配置为被动并行加载模式,CPLD接收到文件版本切换信号后,读取对应的压缩文件并送入FPGA的被动并行加载数据端口D[7:0],完成对FPGA的加载。 图3 基于改进型游程编码的FPGA动态重构原理框图 基于改进型游程编码的FPGA动态重构流程与基于CPLD的FPGA快速动态重构流程除了图2虚线框中的内容(对从FLASH中读取出的数据后续处理)不同外,其他都相同。虚线框中的内容变为了改进型游程编码解码过程,流程如图4所示。 图4 改进型游程编码解码流程图 初始化时连续数值计数器的值为0,从FLASH读取一个字节的数据V,首先需要判断V是否大于0xC0以判断该字节是否为长度字节,如果大于0xC0,则该字节为长度字节,长度为V-0xC0,需要将长度写入连续数据计数器;如果小于等于0xC0,则需要判断连续数值计数器的值R是大于0,如果大于0,则需要将该值向FPGA的被动并行加载数据端口D[7:0]连续写入R次,否则,直接将该值写入到FPGA的D[7:0]端口。每次从FLASH中读取一个字节后,FLASH的地址都要增加1。 性能测试选用的FPGA目标器件为XILINX Virtex Ⅳ XC4VLX60,功能文件为各种调制模式的数传或话音功能文件。测试结果如表1所示,表中快速重构是指基于CPLD的FPGA快速动态重构,改进型快速重构是指基于改进型游程编码的FPGA动态重构。可以看到,基于CPLD的FPGA快速动态重构方法的重构时间都相同为220 ms,这是由同一型号FPGA的bit文件大小一致并且重构处理流程相同造成的。而基于改进型游程编码的FPGA动态重构的重构时间波动较大,原因在于压缩后的文件大小不一致以及游程编码的解码复杂度不同,但时间均不大于87 ms,速度提高60.4%以上。同时,基于改进型游程编码的压缩文件的对存储空间占用大幅减小,存储空间利用率提高61.8%以上。 表1 重构时间测试结果 提出了一种基于改进型游程编码的FPGA动态重构方法,较传统的FPGA动态重构方法有更快的重构速度和更高的FLASH存储空间利用率。虽然该加载方法是针对FPGA全局重构设计实现,但是该方法是通过减小FPGA程序文件大小实现重构速度提高的,因此,对FPGA部分重构同样适用。这种FPGA动态重构方法已在航空电子系统上得到应用,实践证明该方法是一种高效可靠的FPGA动态重构方法。 参考文献: [1]谷銮,徐贵力,王友仁.FPGA动态可重构理论及其研究进展[J].计算机测量与控制,2007,15(11):1415-1418. [2]范斌,常青.基于DSP 的FPGA动态重构系统研究与设计[J].信息与电子工程,2010,8(2):123-127. [3]覃祥菊,朱明程,张太镒,等.FPGA动态可重构技术原理及实现方法分析[J].电子器件,2004,27(2):277-282. [4]周盛雨,孙辉先,陈晓敏,等.基于FPGA的动态可重构系统实现[J].电子器件,2007,30(2):646-650. [5]王鹏,向厚振,张志杰.基于FPGA的动态可重构边缘检测系统设计[J].电视技术,2012,36(7):32-34. [6]李燕斌,李燕春.用XCF32P实现FPGA的高速动态配置[J].电讯技术,2006,46(6):199-202. [7]李燕春.基于CPLD的FPGA快速动态重构设计[J].电讯技术,2008,48(7):87-89. [8]吴乐南.数据压缩的原理与应用[M].北京:电子工业出版社,1995. 邵龙(1982-),男,汉族,四川通江人,硕士研究生。现任中国电子科技集团公司第十研究所工程师。研究方向为信号处理,shaolong1223@163.com。 AnApproachtoDynamicReconfigurationofFPGABasedonImprovedRun-LengthCoding SHAOLong* (The 10th Institute of China Electronic Technology Group Corporation,ChengDu,610036) Abstract:Based on the analysis of shortages in the conventional dynamic reconfiguration method,a novel approach based on improved run-length coding was advanced to improve the performance of dynamic reconfiguration of FPGA.The design and implementation of the approach were also described in detail.The performance results compared with the conventional dynamic reconfiguration method show that not only the speed of dynamic reconfiguration of FPGA can be improved but also the requirement of the storage capacity can be reduced by this approach.Now,it has already been proved in the major projects. Key words:FPGA;dynamic reconfiguration;global reconfiguration;run-length coding;speed of dynamic reconfiguration doi:EEACC:6120B10.3969/j.issn.1005-9490.2014.05.045 中图分类号:TN791 文献标识码:A 文章编号:1005-9490(2014)05-1009-04 收稿日期:2013-10-10修改日期:2013-10-26

3 性能对比

4 结论