SOPC在μC/OS-II系统下的实时调试功能研究*

屈环宇,屈百达

(江南大学 轻工过程先进控制教育部重点实验室,无锡 214122)

SOPC在μC/OS-II系统下的实时调试功能研究*

屈环宇,屈百达

(江南大学 轻工过程先进控制教育部重点实验室,无锡 214122)

随着微电子技术的飞速发展,越来越多的产品选择基于FPGA的SOPC系统设计。本文针对SOPC系统的硬件设计及软件的安全性、实时性、可移植性等方面的需求,在SOPC系统上移植μC/OS-II操作系统,并实现基于时间戳的调试功能。

SOPC;μC/OS-II;时间戳; FPGA

引 言

SOPC技术涵盖嵌入式系统设计全部内容,它是由单个集成芯片完成整个嵌入式系统的主要逻辑设计功能,通过逻辑编程实现硬件和软件上的裁减、扩充、升级。硬件技术是以PCB和电磁兼容性分析、信号完整性分析为基础的高速电路设计技术。软件技术是以RTOS和驱动程序为中心的软件设计技术。本文以CYCLONE IV芯片为载体,设计了基于FPGA的SOPC系统,移植μC/OS-II实时系统,并实现时间戳功能,以利于系统实时调试。

1 SOPC硬件系统的设计

在FPGA上实现SOPC硬件系统的设计,此系统主要是由软核系统、硬实时部分、逻辑电路组成。本文设计了基于NIOS-II软核与μC/OS-II结合的最小实时调试系统。

NIOS-II软核的硬件设计主要在Quartus软件的SOPC Builder模块中实现,它是由NIOS-II微处理器作为CPU,NIOS-II微处理器体系结构支持某些用户自定义功能的指令,并用硬件电路实现这些指令功能,其地位与NIOS-II微处理器内部自带指令集中的指令地位等价。NIOS-II可以根据应用的需要配置不同资源、不同速度级别的CPU、Debug单元、可配置大小的数据Cache、指令Cache、MMU、MPU、中断及通用寄存器。

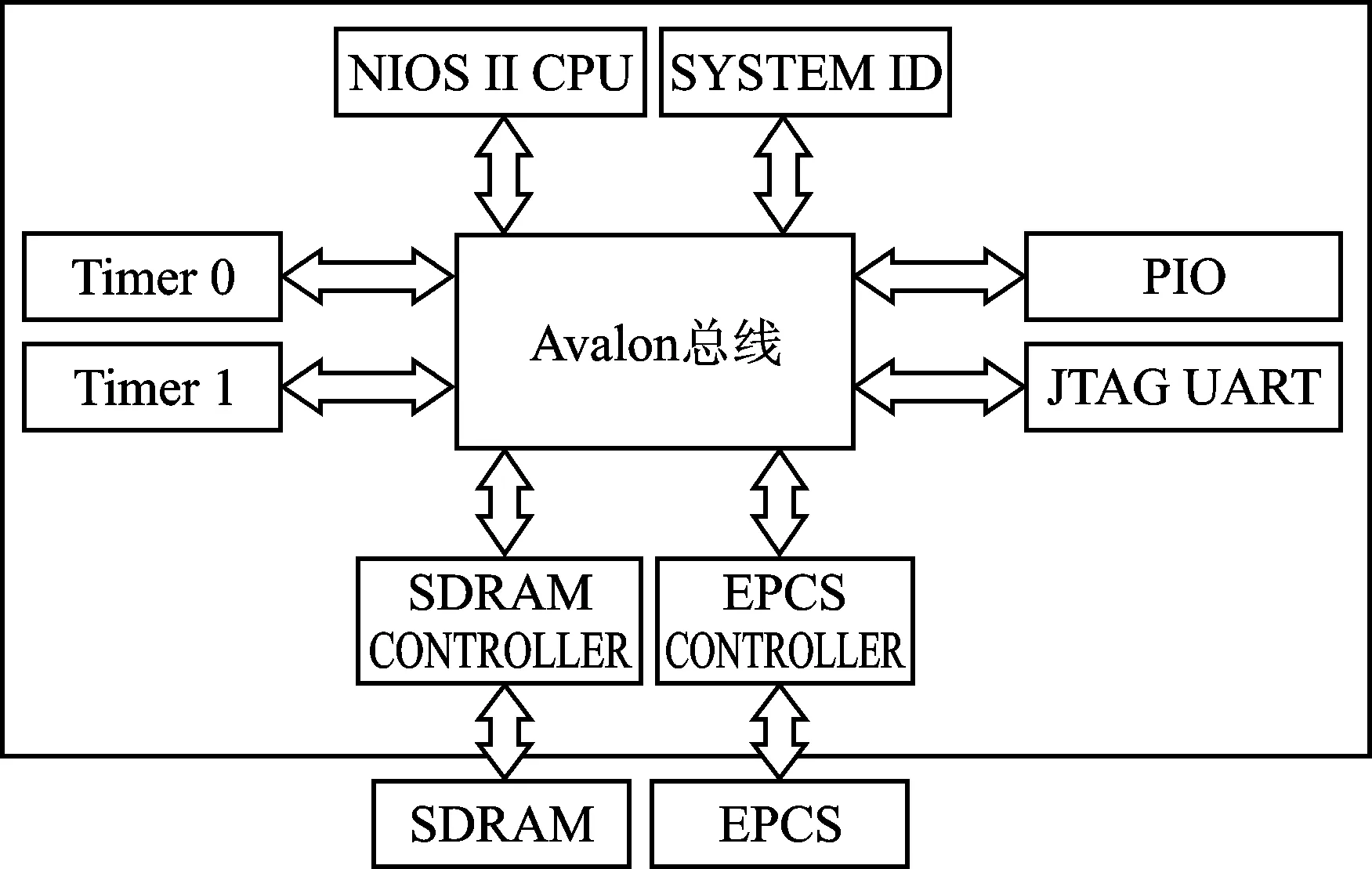

Avalon总线是NIOS-II硬件系统设计中的重要组成部分,它为CPU与外设之间指令与数据的通信提供了一种互联规范,实现CPU指令总线、数据总线与外设的主从关系以及冲突裁决等功能。SOPC硬件系统如图1所示。

图1 SOPC硬件系统

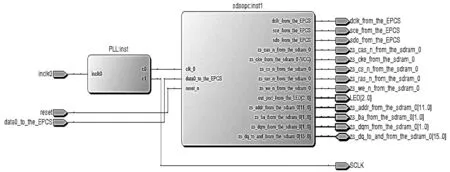

CYCLONE IV系列FPGA芯片每个时钟输入经过一个PLL后,可产生5路时钟输出,每个输出均可配置相应的分频、倍频、相移。本文用了2路输出,一路提供CPU的主频时钟,另一路经过相移后作为SDRAM的主频。该SOPC系统的RTL级视图如图2所示。

图2 SOPC的RTL级视图

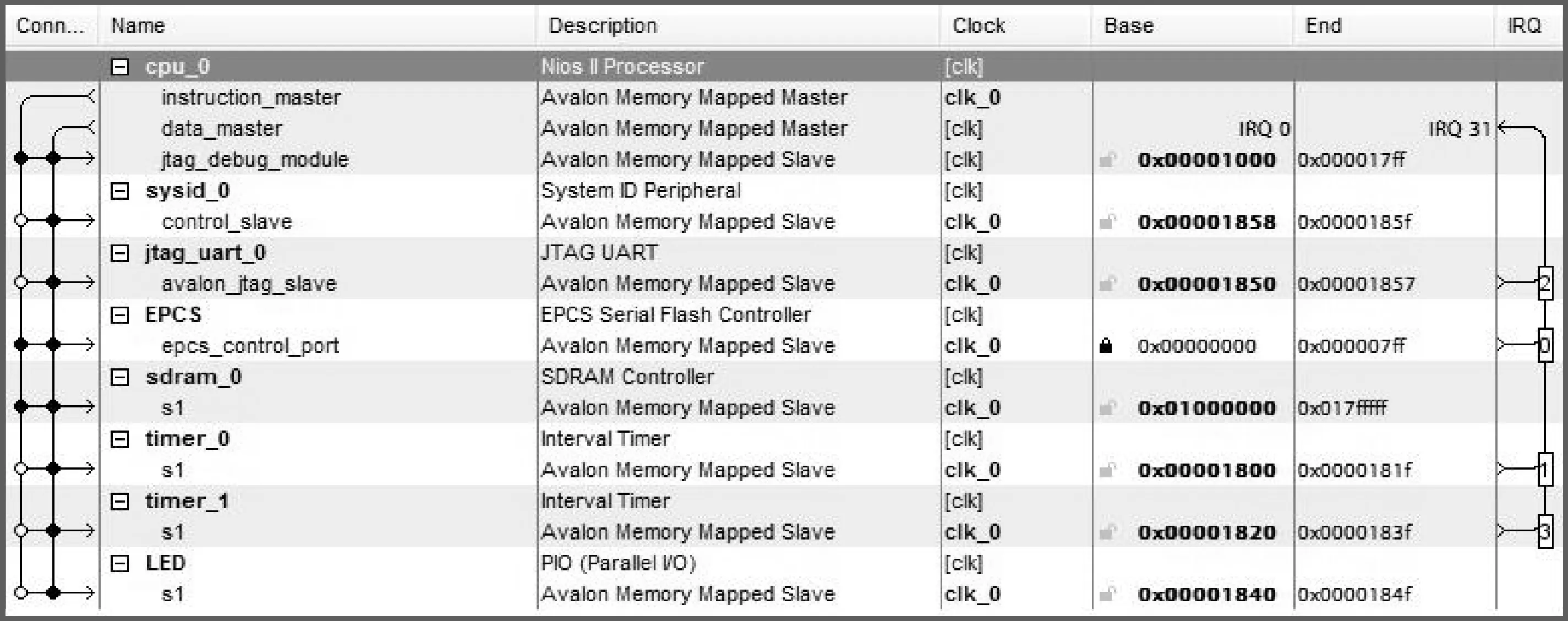

系统在SOPC Builder中的CPU与外设之间指令总线、数据总线、时钟源、寻址地址范围、中断优先级等设置如图3所示。

图3 CPU与外设的系统关系图

基于NIOS-II的SOPC主从关系建立好后,生成对应的硬件系统描述文件,该描述文件为NIOS-II IDE提供系统对应的硬件寻址范围等相关内容,建立并运行TCL脚本文件,将FPGA的引脚与SOPC的硬件电路引脚相匹配。文件进行分析、综合等操作后得到系统级的硬件配置文件。

2 SOPC软件系统的设计

SOPC的软件可在NIOS-II IDE平台上开发,根据之前生成硬件系统描述文件创建相应的工作空间。每个工作空间主要由2个工程组成,一个工程主要存放SOPC的软件代码,另一个工程主要存放SOPC的板级硬件描述。

为方便用户的使用,NIOS-II IDE提供了一些工程模板,其中有一个是Hello MicroC/OS-II的工程模板,创建了这个模板,就基本实现了μC/OS-II系统在ALTER NIOS-II软核上的建立。对于实时性很强的应用,在NIOS-II IDE中可以创建一个硬件定时器,并利用时间戳来进行实时测量,从而实现CPU输入时钟级的实时调试。

在SOPC的硬件系统设计中,创建了两个定时器:第一个定时器为μC/OS-II提供时基中断,中断间隔为1 ms;第二个定时器用于为时间戳计数提供时钟。这两项功能在BSP Editor中设置。

#defineALT_SYS_CLK TIMER_0

#defineALT_TIMESTAMP_CLK TIMER_1

时间戳功能的相关函数申明在sys/alt_timestamp.h头文件中,在使用时间戳功能之前,先要调用alt_timestamp()函数开启时间戳功能。

在μC/OS-II系统中共建立了两个任务,任务体的代码分别为:

t1 = alt_timestamp();

printf("时间戳(t1) = %ld ", t1);

IOWR_ALTERA_AVALON_PIO_DATA(LED_BASE, 1);

OSTimeDly(1000);

t2 = alt_timestamp();

printf("时间戳(t2) = %ld ", t2);

IOWR_ALTERA_AVALON_PIO_DATA(LED_BASE, 2);

OSTimeDly(2000);

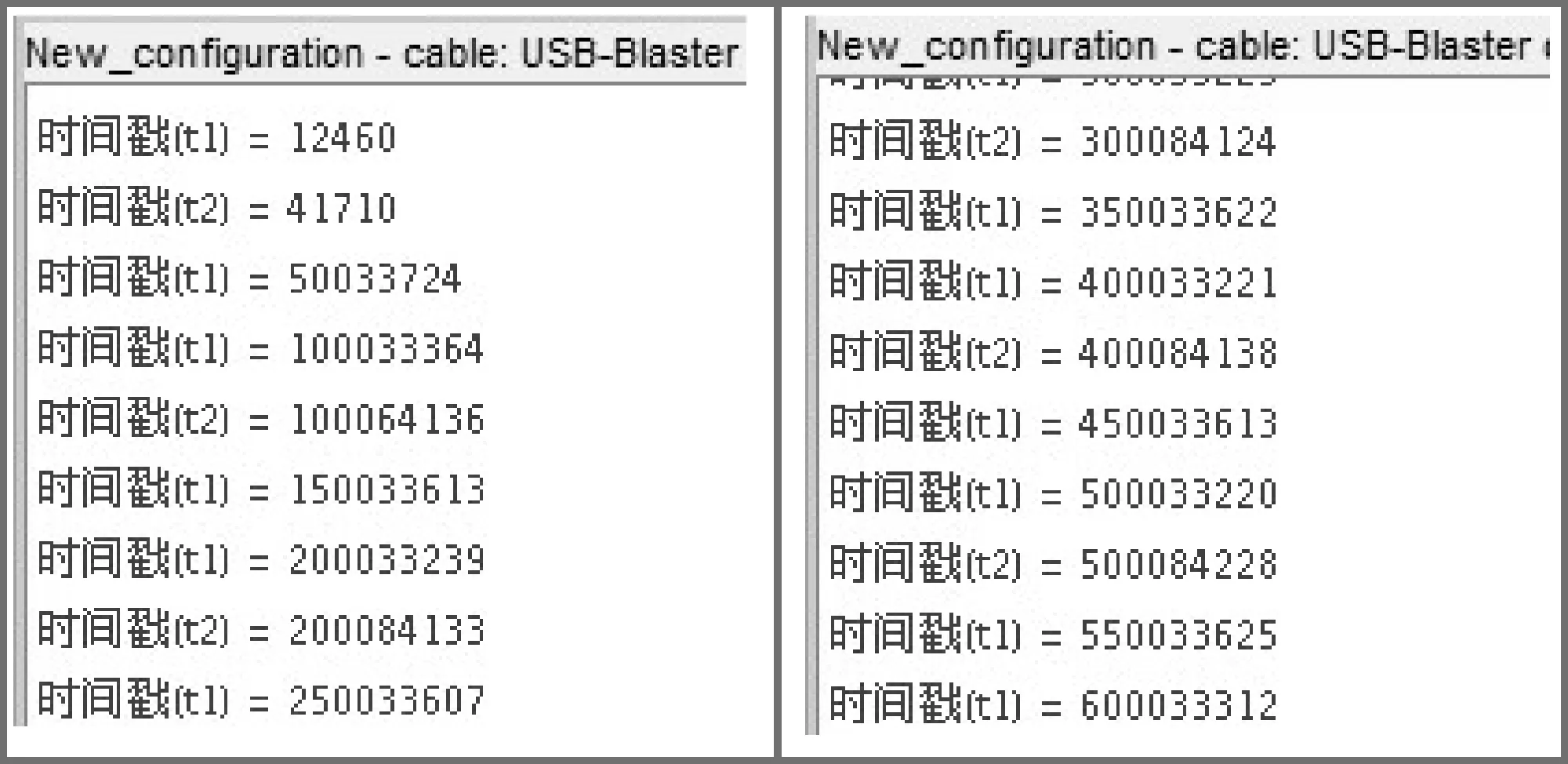

SOPC系统的输入频率为f=50 MHz。故时间戳的计数值每秒增量为50M,时基中断F1=1 000 Hz。

时间戳计算方式如下:

其中,T1、T2分别为任务1和任务2每次执行的时间间隔。

编译程序并配置运行模式为NIOS-II-HARDWARE,下载在Eclipse的Console显示了从UART中接收到的字符输出。由图4可以看出,时间戳值与理想值的偏差非常微小。

结 语

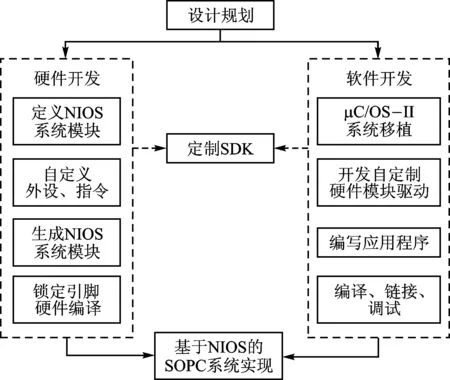

基于FPGA的SOPC系统设计涉及到硬件开发与软件开发两部分,其基本流程图如图5所示。

基于NIOS-II的SOPC发挥了软核嵌入式微处理器的性能,用户可以获得超过200DMIPS的性能,在超过60

图4 时间戳值反馈表

图5 SOPC开发的流程图

[1] Corporation A. SOPC Builder User Guide [EB/OL]. (2010-10)[2013-10-04]. http://www.altera.com.cn/literature/ug/ug_sopc_builder.pdf.

[2] Corporation A. Using MicroC/OS-II RTOS with the Nios II Processor Tutorial[EB/OL]. (2011-05)[2013-10-12].http://www.altera.com.cn/literature/tt/tt_nios2_MicroC_OSII_tutorial.pdf.

[3] 王刚,张潋. 基于FPGA的SOPC嵌入式系统设计与典型实例[M]. 北京:电子工业出版社, 2009.

[4] 宋彩利. 数字系统设计与SOPC技术[M]. 西安:西安交通大学出版社, 2012.

屈环宇(嵌入式系统设计师),主要从事检测技术及自动化装置的研究;屈百达(教授),主要从事PLC应用技术及最新器件应用技术研发与实验。

Research of μC/OS-II with Real-time Debugging in SOPC System

Qu Huanyu, Qu Baida

(Key Lab of Advanced Process Control for Light Industry, Jiangnan University ,Wuxi 214122,China)

With the rapid development of microelectronic technology, more and more products chooses SOPC system based on FPGA. In this paper, with the needs of security real-time, portability of SOPC system's hardware and software design, the research transplantates μC/OS-II operating system in the SOPC system,and realizes the debugging functions based on timestamp.

SOPC;μC/OS-II;timestamp;FPGA

国家级-高等学校学科创新引智计划基金(B12018)。

TP332.2

A

迪娜

2013-10-22)