随钻井下32位信号采集系统设计

贾衡天,管 康,范锦辉,彭 浩,邓 乐,高文凯

(中石油勘探开发研究院,北京 100083)

对地层有源激励模拟信号采集是对发射到不同地层中的电信号状态进行采集量化和保存的过程。它是随钻近钻头电阻率[1]测量系统中不可缺少的重要设备。信号采集系统各个单元必须能够保证稳定可靠地工作在井下高温环境,并能够准确地采集信号。

1 32位模数转换芯片简介

整个数据采集系统性能的关键是ADC芯片的选择。经过比较分析并基于高精度、大动态范围和低噪声的考虑,本系统选用TI公司的ADS1282作为核心ADC器件[2]。ADS1282的主要特征有:具有高分辨率,并且在高精度模式,数据输出率达到250 S/s时具有130 dB信噪比(SNR),甚至在低功耗模式,数据输出率相同时信噪比(SNR)也可达 127 dB;高精度特性,总谐波失真(THD)为-122 dB,积分非线性(INL)为 0.5 ppm;可编程放大器(PGA)具有低噪声:5 nV/,放大倍数为 1~64倍;在高精度模式下其功耗为25 mW,在低功耗模式下的功耗为17 mW,待机模式下为 90 μW,而掉电模式下仅为10 μW,这能帮助系统在井下以电池为能源的情况下发挥更高效能。ADS1282有多种片内数字滤波器,可选择Sinc+FIR+IIR滤波的不同组合方式,其中FIR滤波方式可通过编程设置为线性或最小相位响应。

ADS1282的内部由多路选择器(MUX)、4阶△-Σ调制器、可编程增益放大器(PGA)、增益和失调校准模块、超量程检测电路、控制器、可编程数字滤波器及SPI串行总线接口等组成[3]。

2 高精度数据采集电路设计

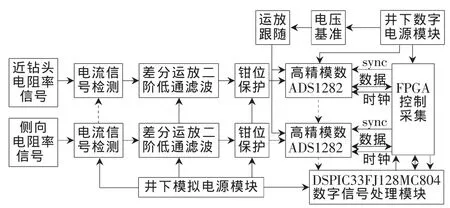

本系统数据采集模块的设计结构框图如图1所示。由于需要采集的是传感器输出的电流信号,而ADS1282要求输入是全差分电压信号,所以输入的电流信号需要转换为一个与电流成正比的电压信号[4]。这可由一个高精度低温漂的采样电阻和跟随器来实现该功能。所得到的电压信号输入给一个二阶模拟低通滤波器,该低通滤波器由一个全差分输出运算放大器构成,在此起到滤去高频噪声的功能。其输出经过钳位保护后,直接输入到高精度的模数转换器的差分输入端。钳位保护由钳位二极管构成,用于保护ADSl282的输入信号瞬时超载。当输入信号电平超出二极管的额定值时,该钳位二极管可对输入进行钳位,实现电平保护的功能。电压基准源芯片和运放跟随器组成的ADS1282的基准源,这样的组合可提高电压基准源芯片携带负载的能力。井下电源模块将电源的电压变换成各个芯片单元所需要的电压。模数转换器的数字通信接口直接接至FPGA,由FPGA构建的SPI总线来读取转换得到的数据[5]。

图1 数据采集模块结构框图

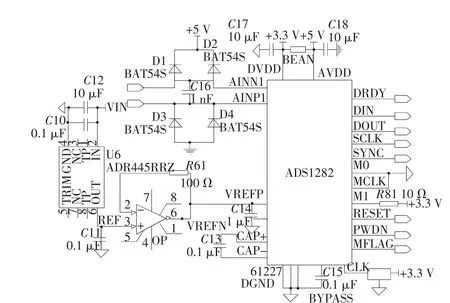

2.1 ADS1282信号采集单元电路

图2 ADS1282功能单元电路

ADS1282为该采集系统的核心,其单元电路如图2所示,ADSl282的信号输入端为差分输入,可以有效地抑制共模噪音。为保护A/D输入端,需要在输入端放置钳位二极管 D1、D2、D3和D4,这样如果输入电压超过从AVDD到AVSS的范围时就会被钳位在这个范围内。VREFP和VREFN分别连接到参考电压和AVSS。ADS1282使用ADR445B来提供基准电压。该芯片具有极低的噪声,极低的温飘(1 ppm/℃),宽的工作温度范围(-40℃~+125℃)。由于参考电压源携带负载的能力有限,为防止ADS1282的参考输入端瞬时电流输入较大,拉低参考电压,造成参考电压不稳定并影响测量,需要在其后接入运放跟随器,增强基准电压的输出电流并提高携带负载能力,以减少因负载变化而产生的纹波噪声。由于ADS1282的调制器直接输出端M0、M1和MCLK不能悬空,因此必须接入固定电平,保持其工作稳定。ADS1282的SCLK、DOUT和DIN输入端,与FPGA内部编程形成的SPI数据总线模块连接。DRDY引脚由FPGA检测,当A/D的数据采样转换完成时该引脚为低电平,FPGA检测到该引脚为低电平时,开始从SPI总线上读取数据。RESET、PWDN和SYNC被FPGA内部的控制模块控制,完成重启、低功耗待机和同步采集功能。

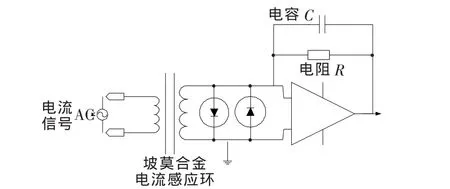

2.2 前模拟检测电路

由于反应地层电阻率的电流信号非常微弱,对其检测精度的要求很高,因此前级处理电路结构和器件选择很重要。运算放大器需选用高共模抑制比、高精度、低漂移和低噪声的器件。

电流检测电路如图3所示,近钻头电阻率的最前端为电流互感器,其输出为微弱电流信号。输入的电流信号经过一个I/V转换电路后得到与之成正比的电压信号[6]。I/V转换电路中运放的反馈采样电阻R选择非常重要,其性能直接影响所得的电压信号的稳定性和精度。

图3 电流检测电路

选用VISHAY公司生产的VSMP系列超精密金属箔电阻,它具有极好的稳定性,并且其温漂接近于零,具有极低的噪声和极高的阻值精度。调节电阻R的值可以改变运算放大器输出的电压值,而电容C用来补偿相位差,调节运放带宽增益积范围内的相位裕度,其也可去除干扰尖峰信号。由于电流互感器次级和初级线圈数比非常大,当有意外大电流流入初级时,为避免次级产生过高的电压对电子元器件产生有害(或不良)的影响,采用了两个反向并联的二极管。

该跟随缓冲运放选用AD829,该芯片同样具有极低的 噪 声 (1.7 nV /Hz)、 高 压 摆 率 (230 V/μs)、 宽 通 频 带(50 MHz以上)、很高的共模抑制比(120 dB)、高开环增益、低输出偏置电压、极低的温度漂移和宽的电源电压(±15 V)等特性。工作温度范围为-55℃~+125℃,完全适合于井下高温工作环境。

2.3 ADS1282信号调理电路

ADS1282的输入是采用差分电压输入形式,差分输入最明显的优势在于其抗干扰能力强,并能有效抑制自身对外界的电磁干扰。当环境存在电磁噪声干扰时,噪声会同时被耦合到两条信号线上,再经两信号差值后,电磁干扰噪声信号几乎被抵消。并且全差分两根信号线上的电信号对其他电路辐射的电磁场也可以相互抵消[7]。

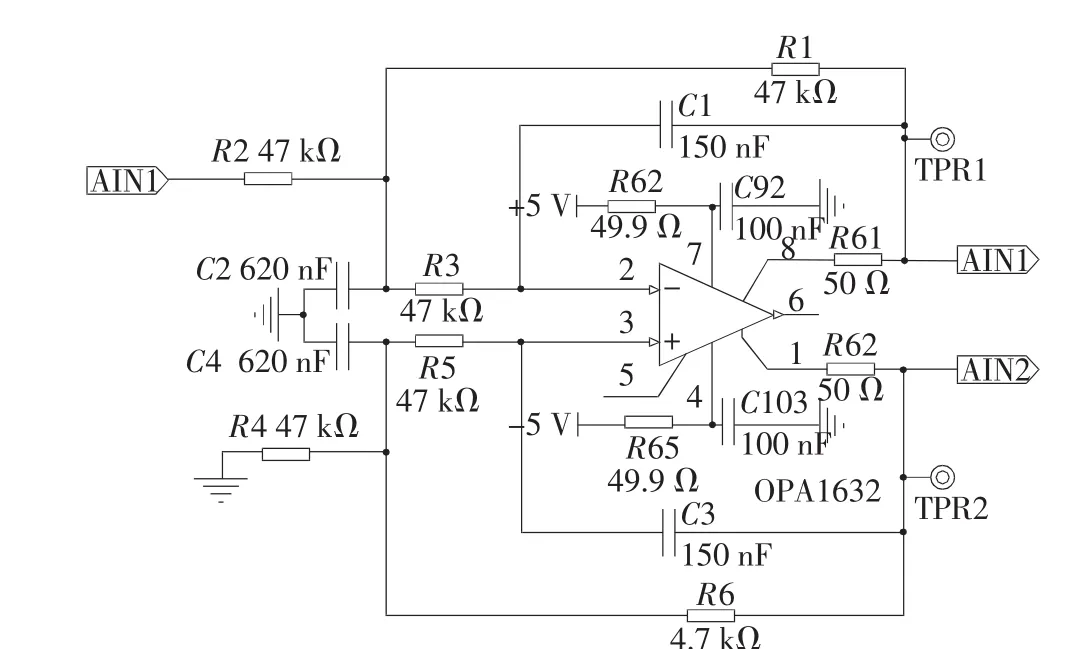

由于模数转换器的输入端是差分形式,而前端模拟检测电路是单端输出的,因此,需要一个低噪声的单端输入差分输出的模拟信号调理电路来连接。单端转差分电路主要有两种方式,一是用多个运算放大器构成差分输出;二是使用全差分运放芯片。第一种方法使用多个运放,运放的性能和温漂指标会有一定差距,不可避免地引入了更多的噪声。而专用全差分运放芯片外围结构简单,所用的分立器件很少,因此本系统选取单片全差分运算放大器OPA1632,并用其构成滤波功能和模拟信号调理电路。

OPA1632是一款高性能和低噪声的全差分运算放大器。信号失真低,芯片噪声降低至1.3 nV/Hz。使用OPA1632构成二阶巴特沃斯低通滤波器,通过选取不同的电阻电容组合可以实现滤波器通频带宽的改变,如图4所示。二阶巴特沃斯滤波器可以在通频带内达到频率响应曲线的最大平坦度,而在阻频带则逐渐下降为零。

图4 全差分二阶低通滤波器

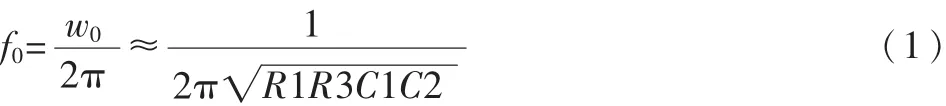

由于全差分运算放大器构成的对称性,在电路设计中 R1=R6,R2=R4,R3=R5,C1=C3,C2=C4, 该二阶巴特沃斯滤波器电路的特征频率为:

增益为:

滤波器Q值是:

设计中 A0=1,所以 R1=R2,令 R1=R2=R3=R,于是

3 高精度数据采集软件设计

3.1 ADS1282读写控制

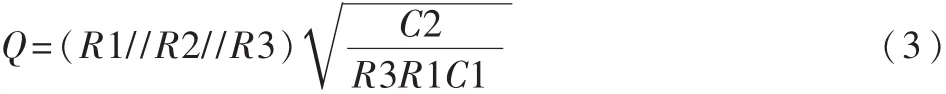

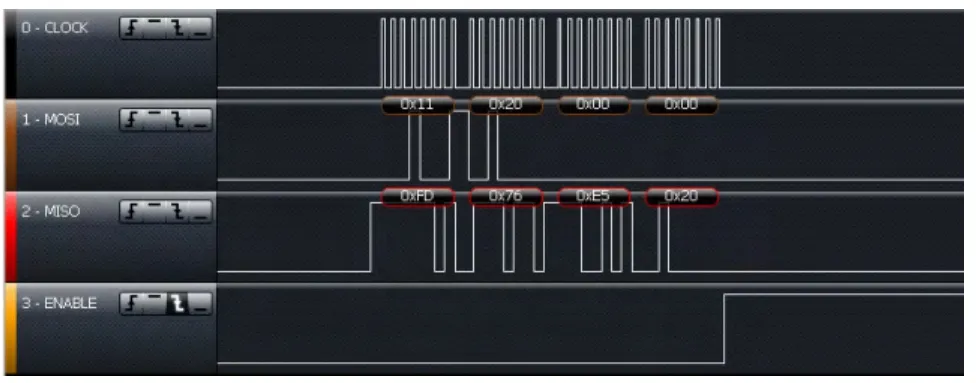

在ADS1282上电后,其开始自动采集,在数据采集转换完成后DRDY引脚会产生低电平脉冲,需要在ADC工作前对其进行读取器件ID操作和初始化操作,用以验证SPI总线上工作时序是否正确并对ADC进行初始化设置。通过逻辑分析仪可以记录SPI数据总线上的时钟和数据信息并进行分析。

读取器件ID首先发送停止自动采集命令(0X11),时序图如图5所示,从逻辑分析仪采集的结果可以看出ADS1282接收到该命令后就停止了自动采集 (MISO自动输出停止)。

图5 停止自动采集命令时序图

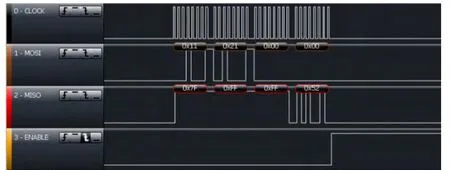

读取ID命令时序图如图6所示。发送读寄存器指令+寄存器地址(0X21),发送 0X00代表只读取一个寄存器。最后 ADS1282返回ID:0X20,证明SPI时序正确并与ADS1282成功进行通信。

图6 读取ID命令时序图

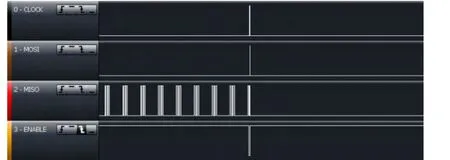

初始化设置ADS1282的配置寄存器0,其主要设置配置寄存器0的第6位为MODE=1,采用高分辨率模式,DR[2:0]=010:数据输出率为 1 000 S/s,Digital Filter Select FILTR[1:0]=10:Sinc+LPF filter blocks数字滤波器选择。然后对ADS1282配置寄存器0数据读回判断配置结果是否正确,读回数据如图7所示。

图7 读寄存器0命令时序图

首先发送停止自动采集命令(0X11),然后发送读寄存器指令+寄存器地址(0X21),发送 0X00代表读取从地址0X01开始的一个寄存器。最后ADS1282返回config0:0X052,证明初始化配置寄存器0成功。

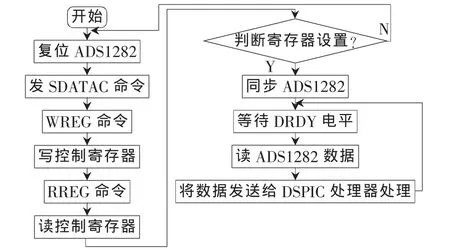

3.2 FPGA控制ADSl282工作流程

外部器件通过串行接口(SPI)来访问ADSl282的数据和设置寄存器。ADSl282输出的转换数据是32 bit宽的二进制补码的格式,其中最高位是符号位,“0”表示正数,“1”表示负。SPI接口引脚包括SCLK、DIN及DOUT三路基本信号引脚。数据在时钟引脚SCLK的上升沿移入数据输入引脚DIN,在时钟引脚SCLK的下降沿移出数据输出引脚DOUT。DRDY引脚是输出信号,当其为低电平时,新的转换数据已准备好可以被外部器件读出了。FPGA可以通过判断该引脚电平的状态来决定读取数据时刻。当SPI总线时钟引脚SCLK无效时需保持低电平。

FPGA芯片通过SPI通信总线和相关控制引脚对ADS1282进行初始化设置和读写控制,对ADS1282的操作流程如图8所示,具体操作如下。

图8 ADS1282的读写操作流程

(1)对数模转换芯片进行复位操作,即在复位引脚RESET施加低电平脉冲,芯片对内部寄存器进行复位操作,并且是内部寄存器的值恢复到出厂默认设置。复位脉冲结束后需要至少100 ms的延时间隔,再进行其他操作,保证芯片内部寄存器初始化工作完毕。

(2)向数模转换芯片发送停止连续读数据命令(SDATAC、0X11),使芯片停止向外部器件发送采集转换完成的数据,读写时序如图5所示。

(3)向数模转换芯片发送写寄存器命令(WREG),然后配置需要设置的寄存器位形成相应的命令字,并通过SPI数据总线写入配置寄存器中,完成芯片工作前工作方式的设置,保证芯片按照编程的方式工作。

(4)向数模转换芯片发送读寄存器命令(RREG),把写入到芯片寄存器中的数据读出来,并与写入寄存器时的数据进行对比。不一致时则需要重新开始第一步操作。

(5)通过外部引脚(SYNC)同步 ADC工作时序,使得两路ADC同时开始采集数据。

(6)等待数据采集转换完成,信号引脚(DRDY)的低电平脉冲到来,FPGA通过SPI总线读取采集到的数据,然后把读取的数据通过串口发送给DSPIC33FJ128MC804数字信号处理芯片,用于进一步对数据进行分析。数据发送完成后,返回判断DRDY引脚的状态,等待下一个采样转换完成的数据,如此循环工作。

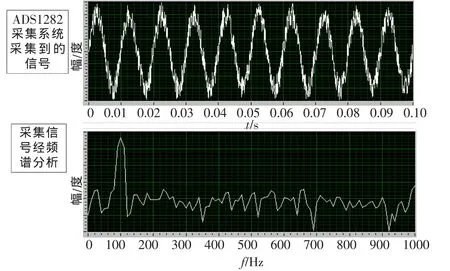

在对该采集系统进行井下试验后,由于发射到地层中的100 Hz正弦电流信号经过地层后被接收端接收并放大,如图9所示,该信号含有大量的噪声,但经过傅里叶频谱分析可以看到该信号的基频与发射信号频率相同。该采集系统可准确采集流经地层的电流信号。

图9 信号采集与频谱分析

本文根据实际应用中对高精度数据采集处理的要求,设计出了一个应用于井下的基于FPGA以及32位高精度ADC为核心的高精度数据采集系统。提出了采用TI公司的32位高精度ADC芯片ADS1282为数据转换核心的高精度数据转换模块。根据设计方案对整个系统的各个功能电路进行详细设计,并最终研制完成了该系统。

[1]苏义脑,窦修荣.随钻测量、随钻测井与录井工具[J].石油钻采工艺,2005,27(1):15-17.

[2]王琳,商周,王学伟.数据采集系统的发展与应用[J].电测与仪表,2004,41(8):4-8.

[3]张春燕.用于数据采集的Sigma-Delta调制器的设计与实现[D].上海:上海大学,2007.

[4]于丽霞,王福明.微弱信号检测技术综述[J].信息技术,2007(2):115-116.

[5]牛清红,张春熹,宋凝芳.用A/D和FPGA实现的加速度计数据读出系统[J].中国惯性技术学报,2006,14(1):63-64.

[6]林春方,社先彬,郭立.基于 I/F变换的弱电流测量仪的研制[J].上海交通大学学报,2006,40(9):1517-1518.

[7]李素芬,李刚,孙景发.模数转换技术及其发展[J].电子技术应用,2002,28(4):72-74.