基于MicroBlaze的AXI总线实时时钟IP核设计

萨其日娜

(内蒙古鲁电电力工程有限公司,内蒙古 010000)

基于MicroBlaze的AXI总线实时时钟IP核设计

萨其日娜

(内蒙古鲁电电力工程有限公司,内蒙古 010000)

应用MicroBlaze软核作为CPU的硬件平台,在此平台上设计了基于AXI总线的通用实时时钟IP核。给出了创建IP核的过程和导入IP核的方法。介绍了实时时钟的IP核结构,给出了IP核的结构框图。介绍了实时时钟的原理,给出了实时时钟各个模块的核心代码。

AXI;IP核;实时时钟;MicroBlaze

引 言

MicroBlaze是可以嵌入到FPGA中的RISC处理器软核,具有运行速度快、占用资源少、可配置性强等优点,广泛应用于通信、军事、高端消费市场等领域。Xilinx公司的MicroBlaze 32位软处理器核是支持CoreConnect总线的标准外设集合。MicroBlaze处理器运行在150 MHz时钟下,适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

AXI是ARM公司提出的AMBA3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。AXI 总线技术不但使片上系统面积更小功耗更低,同时还获得了更加优异的性能。AXI 能达到这样的技术指标的一个主要原因,就是它的单向通道体系结构。单向通道体系结构使得片上的信息流只以单方向传输,减少了延时。AXI 技术满足超高性能和复杂的片上系统设计的需求,因此AXI的与应用也越来越广泛[1]。随着ARM公司与Xilinx公司的合作逐步加强,Xilinx开始逐步在FPGA产品中大力推广AXI总线技术。AXI在Xilinx公司的MicroBalze等CPU上面得到越来越重要的支持,必将成为未来的主流技术。

1 IP核的创建与导入

Xilinx的MicroBlaze软核为用户提供了大量的可用IP核,方便用户开发缩短开发周期,降低成本。但是用户的需求千差万别,官网提供的IP核不可能满足所有人的需求。因此开发环境支持用户自定义IP核,根据用户的不同需求,用户可以通过定制的方式开发自己需要的IP核。在测控装置的研发过程中,笔者发现插件上设计的RTC时钟芯片,虽然具有掉电保持时间的功能。但是在完成装置界面对时等功能时,对RTC芯片的读写操作显示到界面上后,会有一定的延时,界面无法精确的显示当前的时间。因此设计一个通过自定制IP核的形式,实现实时时钟时钟的功能解决上述问题。开发环境中的Xilinx Platform Studio为IP核的定值与导入提供了向导。

创建IP核的步骤如下:选择Hardware→Create or Import Peripheral Wizward来打开创建和引入外设向导。单击Next按钮。选择Create templates for a new peripheral。默认情况下新的外设将被存在pcores文件夹中方便查找。然后再次单击Next按钮。在Create Peripheral-Name and Version对话框中,输入定制的IP核的名字,这里输入本次定制IP核名称为soft_rtc。下面是版本控制,可以根据需要修改。界面如图1所示。

图 1

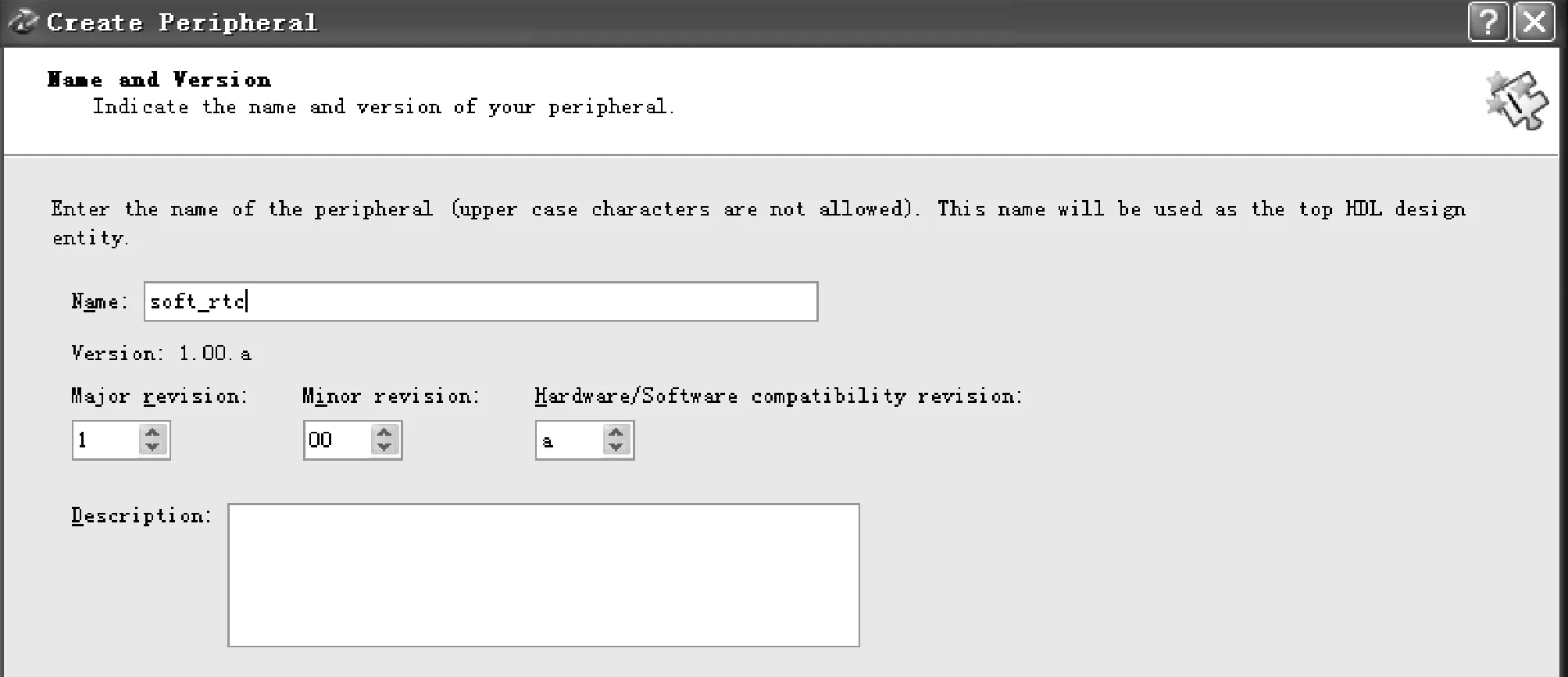

单击Next按钮,在Create Peripheral-Bus Interface 对话框中,选择AXI4,这是新的外设将要连接的总线。对于简单设计可以选择AXI4_Lite;下一步在IPIF (IP 接口) 配置,这里配置接口的一些属性,如是否是AXI 主/从设备等。所定制的IP是一个从设备,因而不需要使用主设备接口。数据宽度选择默认的32位,下一步选择需number of use memory ranges数量,这里选1。界面如图2所示。

图 2

接下来就是IPIC(IP 互联),也就是IP的接口信号。接下来需要使用需要使用BFM总线功能模型对外设进行仿真,本例不要使用。最后,需要选择HDL类型、ISE工程支持和软件驱动模板。此处使用Verilog模板,选择后需IP接口仍然是VHDL编写,只是用户逻辑改用Verilog。如果不需要使用软件驱动模板,可以不选。最后给出了外设的信息summary。完成上述步骤后,自定制的soft_rtc IP核的模版创建完成,只需根据需求对user_logic文件索要实现的功能编写应用代码,并配置相应的引脚。

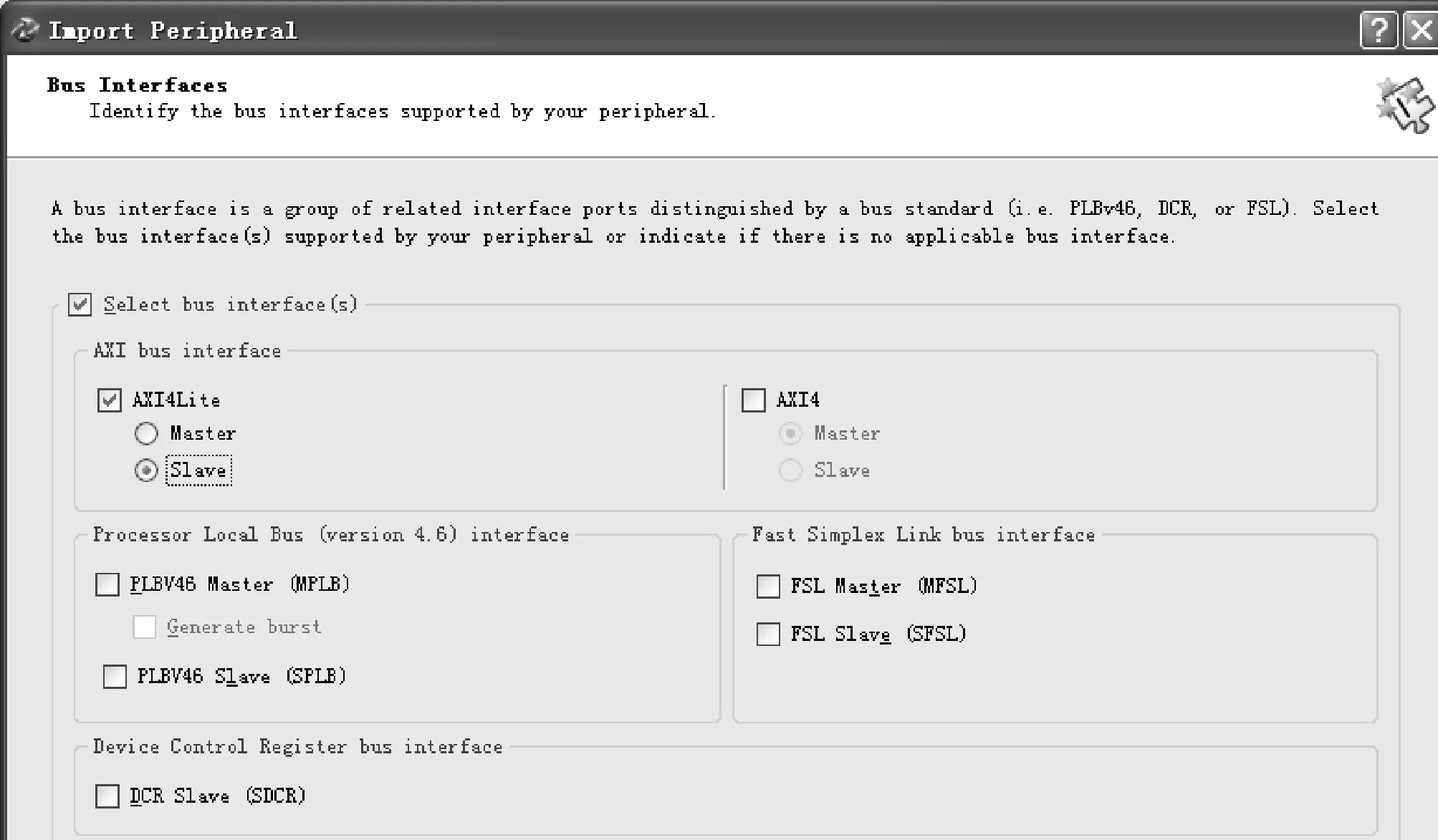

完成user_logic的代码编写后,需要将完成的IP核导入工程。大致步骤如下:再次使用Hardware Create or Import Peripheral, 并单击Next按钮。选择Import existing peripheral项,单击Next按钮再次输入名称soft_rtc,单击Next按钮,选择Yes按钮。下一步选中第一项HDL source files单击Next按钮,然后下一步骤选中第二项Use existing Peripheral Analysis Order files(*pao), Browse到相应的目录下,选中.pao文件,单击打开,然后单击Next按钮;出现图3所示的窗口时,选中左侧AXI4Lite选项,然后单击Next按钮后面都选择默认选项直到出现结束窗口时选择结束按钮Finish按钮。 这样通过上述步骤完成了IP核的创建与导入。最后将IP核加入到工程中与AXI4Lite总线连接。完成IP核模版的创建与导入后,下一步就要进行完成IP核user_logic文件的代码设计。

图 3

2 soft_rtc IP核的设计

soft_rtc IP核中主要分为与上层接口的寄存器管理模块、为IP核提供精确时钟的 Clock分频模块和RTC的核心逻辑模块[2]。IP核接口如图4所示。

图 4

开发板上提供有25 MHz的晶振和16.384 MHz的晶振。为了计时的精度,将16.384 MHz的输入信号引入soft_rtc模块。Clock 分频模块将输入的16.384 MHz准晶振时钟4分频得到4.096 MHz的时钟信号。分频核心代码如下:

always @(posedge clk_in)

begin

if(clk_div == 4'b0011)

clk_div <= 4'b0110;

else if(clk_div == 4'b0110)

clk_div <= 4'b1100;

else if(clk_div == 4'b1100)

clk_div <= 4'b1001;

else

clk_div <= 4'b0011;

end

寄存器控制模块的主要功能是实现对RTC 模块内部各个寄存器的读写控制并为整个IP 模块提供控制信号。提供上层应用代码与IP核代码之间的接口。在这个模块内部包含对每个内部功能寄存器的读写进行控制的子模块和对各个子模块时钟的总体分布控制[3]。本设计中一共定义了16个寄存器,主要有控制寄存器、状态寄存器以及毫秒的读寄存器、毫秒的写寄存器;秒的读寄存器、秒位写寄存器、分位的读寄存器、分位的写寄存器、小时位的读寄存器、小时位的写寄存器、以及年月日的读与写寄存器等。

设置RTC核心代码如下:

always @(posedge Bus2IP_Clk)

begin

if(Bus2IP_CS[0] && Bus2IP_WrCE[0] && (Bus2IP_Addr[9:2] == SETSECOND_Addr))

SetSecondRegister <= Bus2IP_Data[5:0];

……

end

读RTC核心代码如下:

assign IP2Bus_Data[15:0] = (Bus2IP_CS[0] && Bus2IP_RdCE[0] && (Bus2IP_Addr[9:2] == MSECOND_Addr))?{6'h00,GetMsecondRegister}:16'hzzzz;

……

RTC的核心逻辑模块主要完成的功能就是精确计时。IP核中通过计数器的控制,毫秒逢1000进位,秒、分和小时逢60进位,月逢12进位。设计时要全面考虑实际情况,注意对闰年以及不同月份天数不一样等情况的处理。RTC计时的核心代码如下:

always @(posedge SETTIME or posedge clk_jg)

begin

if(SETTIME)

SecondRegister <= SetSecondRegister;

else if((SecondRegister_B < 59) && Msecond_Carry)

SecondRegister <= SecondRegister + 1;

else if(Msecond_Carry)

SecondRegister <= 6'h00;

else

SecondRegister <= SecondRegister;

end

……

当时钟上升沿到来或者应用程序发出设置时间指令后,进行判断:秒位如果小于59并且毫秒位有进位,此时秒位计数器加1;如果秒位计数器大于或等于59时毫秒位有进位则将秒位清零。其他情况秒位计数器保持原来数值。 其他的分、小时、日月年等计数依次类推。

结 语

[1] 田泽,曹庆年,刘天时,等. 嵌入式处理器S3C2440 Windows CE的RTC模块设计与实现[J]. 计算机应用与软件,2007,24(3):31-33.

[2] 周飚, 谢晓阳. 有限状态机在RTC设计中的分析与应用[J].计算机系统应用,2008,17(5):77-80.

[3] 戚战锋. RTC技术在系统集成中的应用研究 [J].信息通信,2012(6):37-38.

萨其日娜(工程师),从事电网自动化研究。

Real-time Clock IP Core Based on AXI Bus and MicroBlaze

Saqirina

(Inner Mongolia Ludian Electric Power Engineering Corp. Ltd., Nei Menggu 010000, China)

MicroBlaze was used as embedded hardware system. In this embedded hardware system, the real time clock IP core was based on AXI bus. The method of creating and importing the IP core was provided. The structure of the IP core was introduced. At the same time the structured flowchart of the IP core was provided. The theory of the real time clock was introduced, and the core code of the modules was provided.

AXI; IP core;real time clock;MicroBlaze

TP399

A

2014-02-25)