嵌入式PCI总线主模式应用中时序转换模块设计※

王传申,董高森

(江苏自动化研究所,连云港 222061)

王传申(高级工程师),主要从事嵌入式系统设计。

引 言

工业用CPCI总线板卡测试环境一般配备计算机主模块,以实现总线读写控制。已有的测试环境中,选择外购的PC/104-PLUS系列计算机作为主模块,它具有体积小、功能全、适合工业应用场合等优点,但作为测试环境组成部分也存在以下不足:

① 价格高。一块PC/104-PLUS系列计算机模块价格在3000~4000元。

② 状态不确定。作为商用产品,该计算机模块升级更新较快,这可能给使用方带来停产、状态变化等问题。

③无法进行特殊处理。由于模块不属于自主研发,无相关的技术图纸,故无法进行三防等特殊处理,使得测试环境的应用范围受限。

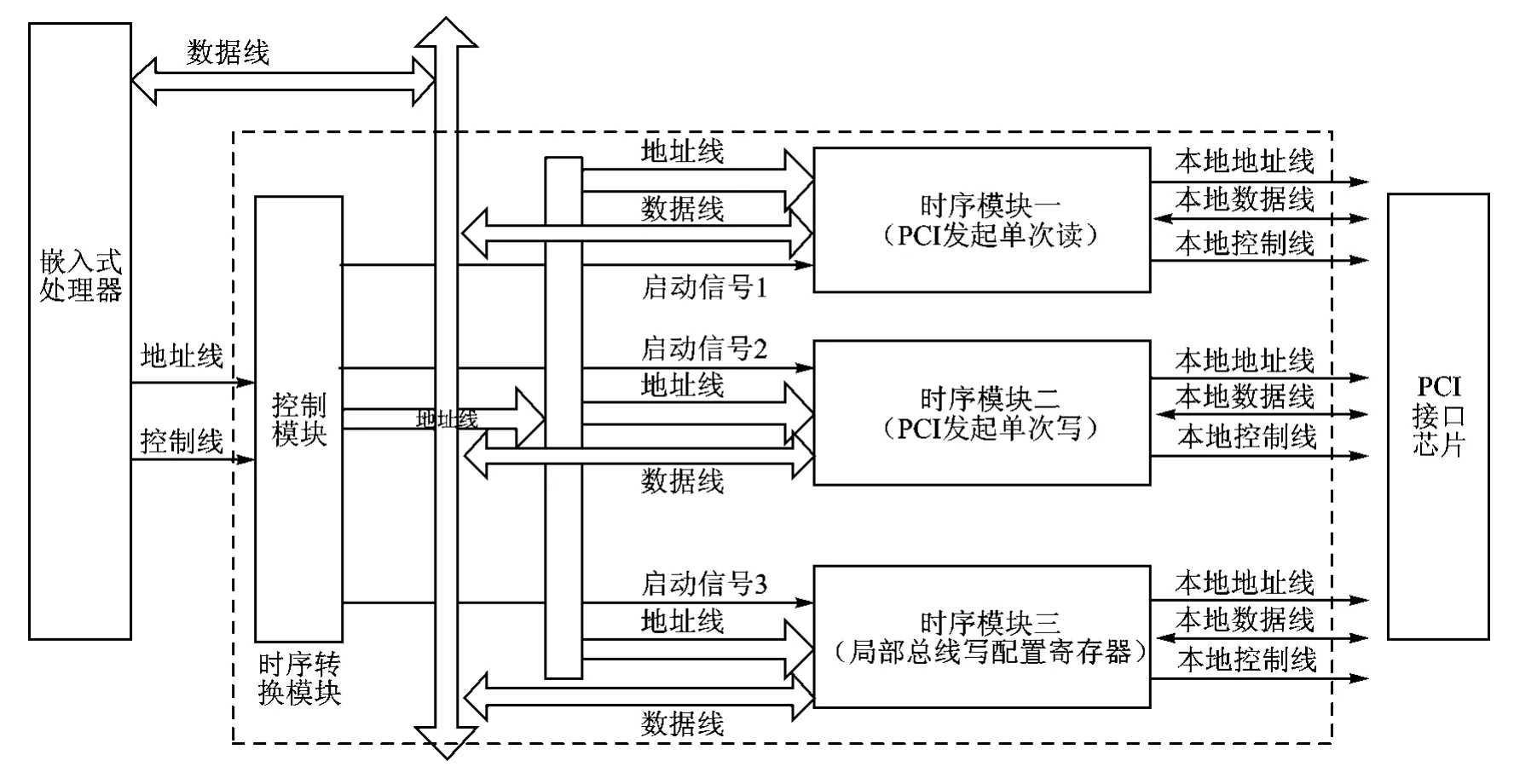

鉴于测试应用下对计算机主模块的资源要求不高,设计以嵌入式处理器为核心的主控模块,替代外购的PC/104-PLUS系列计算机模块,实现对被测板卡的PCI总线读写控制,完成测试任务。主控模块硬件组成如图1所示。

其工作原理是:嵌入式处理器接收计算机的测试命令并控制PCI接口芯片实现对被测板卡的读写控制及初始化操作。其中,由于嵌入式处理器外部存储器总线与PCI局部总线接口不兼容,因此设计时序转换模块,通过该模块完成两种总线之间的信号转换。目前,已有研制单位在工业控制系统的升级改造中使用51系列单片机控制PCI接口芯片实现ISA总线控制系统向PCI总线的升级[1]。但是,作为板卡测试环境主控模块核心,51系列单片机在内部资源及接口种类上略显不足,同时考虑到以后功能扩展的可能性,项目中选用ARM系列微处理器为核心开发主控模块,并基于该处理器设计时序转换模块。

1 外围芯片及时序

主控模块的嵌入式处理器选择NXP公司的LPC2478,该芯片具有以下主要特点[2]:

① 具有网口、USB接口、串口等多种接口方式,方便与系统计算机连接;

② 具有外部存储器访问接口(包括24位地址线、32位数据线及读、写等控制信号),利用该接口可实现对PCI接口芯片的控制;

③ 工作频率可达72MHz。

PCI接口芯片选择PLX公司的PCI9054。PCI9054是常用的PCI总线接口芯片,局部总线工作频率可达50 MHz、PCI总线工作频率为33MHz。该芯片在PCI接口端支持主、从两种工作模式,在局部总线端支持M、J、C三种工作模式。主控模块设计中选择PCI主模式+局部总线C模式的组合工作方式。

在进行PCI总线板卡测试过程中,嵌入式处理器需要通过PCI局部总线控制PCI接口芯片完成以下操作:主控模块PCI配置寄存器写;被测板卡PCI配置寄存器读、写;被测板卡I/O(存储器)读、写。

对于嵌入式处理器,以上操作按读、写两种状态分类,分别对应LPC2478的外部存储器读(External Memory Read Access)、外部存储器写(external Memory Write Access)两种时序过程[2]。

2 时序转换模块设计

时序转换模块在硬件上是一片可编程芯片,设计时通过使用硬件描述语言及相关开发环境进行内部逻辑设计。逻辑设计采用模块化方法,各模块的设计如下各节所述。

2.1 顶层模块设计

时序转换模块的总体设计思路是:针对不同的本地总线时序,分别设计子模块产生相应读写状态下的输出时序。子模块初始处于“空闲”态,由上一级控制模块启动,同一时刻只有一个子模块处于工作状态,转换完成,子模块再次进入“空闲”态,并等待下一次启动信号的到来。

由PCI9054数据手册可以发现,PCI9054五种局部总线时序过程中“PCI发起配置读”与“PCI发起单次读”在时序上完全一致,可以采用同一个子模块实现转换;同样道理,“PCI发起配置写”与“PCI发起单次写”也可以采用同一个子模块。时序转换模块的内部逻辑如图2所示。

图2 时序转换模块内部逻辑框图

2.2 子模块设计

2.2.1 时序模块设计

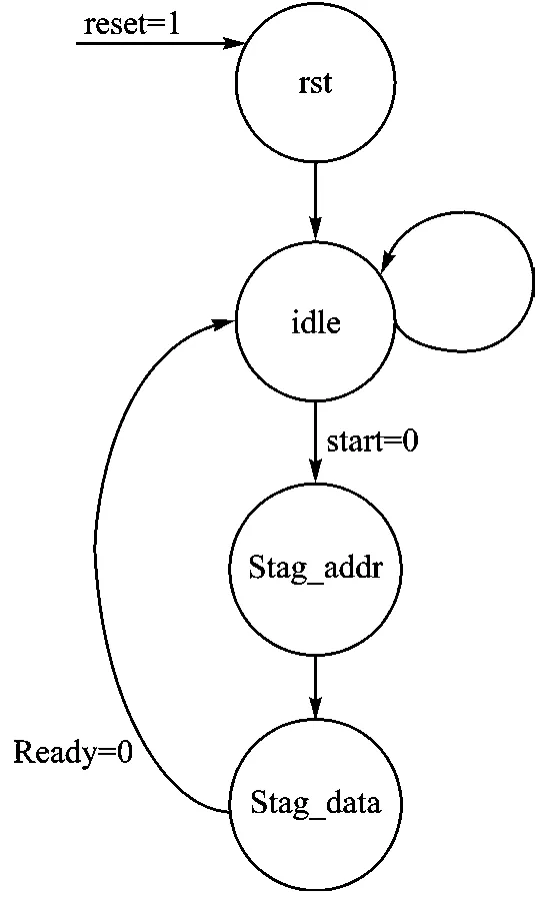

时序模块(包括时序模块一、时序模块二、时序模块三)接收来自控制模块的启动信号、地址信号及外部数据信号,通过内部逻辑综合,产生符合PCI9054局部总线时序的完整的信号输出。下面以图2中时序模块二为例,介绍具体设计(本文中的三个时序模块均采用状态机[4]实现)。

分析PCI9054数据手册中“PCI Initiator Single Write”时序图,将整个时序过程划分为3个状态:idle状态(总线周期开始前或结束后)、Stag_addr状态(ADS#信号下降沿,总线周期开始)、Stag_data状态(ADS#信号上升沿,数据信号有效)。根据以上划分,模块的状态机设计如图3所示。

图3 时序模块二状态转移图

根据状态转移图,模块二复位后处于idle状态,等待控制模块的启动命令;当start信号有效时进入Stag_addr状态,继而直接进入Stag_data状态,然后等待PCI9054的准备好命令;当ready信号有效时,模块重新进入idle状态,然后等待下一次启动到来。

各个状态下产生的输出如下:

◆Stag_addr状态。ADS#有效、LBE[3:0]有效、LW/R有效、LA[31:2]有效。

◆Stag_data状态。ADS#无效、BLAST#有效、LD[31:0]有效。

◆idle状态。上述信号均无效。

2.2.2 控制模块设计

控制模块的主要功能是产生启动信号和进行地址转换。控制模块接收来自嵌入式处理器的地址信号、片选信号及读写控制信号,通过内部逻辑综合,产生时序模块的启动信号,同时将嵌入式处理器的24位地址信号转换为30位地址信号,以便供给时序模块使用。

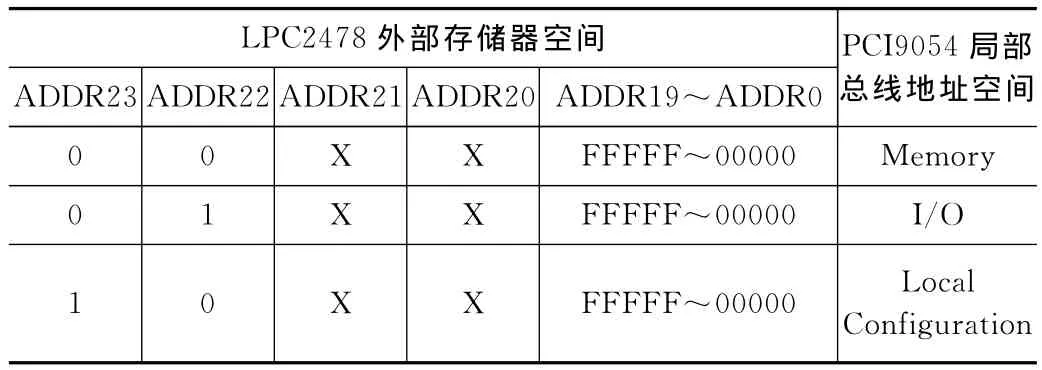

嵌入式处理器通过时序转换模块访问的PCI9054局部总线地址空间包括3类:PCI存储器空间(PCI memory space)、PCI I/O空间(PCI I/O configuration space)及本地配置寄存器空间(local configuration space)。通过将LPC2478的外部存储器可寻址空间[2]划分成若干个区域及控制模块的译码,实现外部存储器空间与局部总线地址空间的一一对应。

具体设计中对LPC2478外部可寻址空间的一个静态存储区进行空间划分,该存储区容量为16MB(地址范围为0x8000 0000~0x80FF FFFF),为PCI9054局部总线3类地址空间各分配1MB的容量,每类地址空间以LPC2478外部地址总线的最高两位进行区分,分配后的各空间地址范围如表1所列。

启动信号的产生主要通过对嵌入式处理器总线信号的状态判断来实现。3个时序模块中,1个实现局部总线读操作,2个实现局部总线写操作。对于第1个模块,控制模块通过对“读”控制信号的状态判断来决定是否产生启动信号;对于后2个模块,控制模块在对“写控制信号状态判断的基础上还要结合输入地址范围来决定产生时序模块二或时序模块三的启动信号。总线信号与启动信号的对应关系如表2所列。

表1 LPC2478外部存储器空间分配

表2 总线信号与启动信号关系真值表

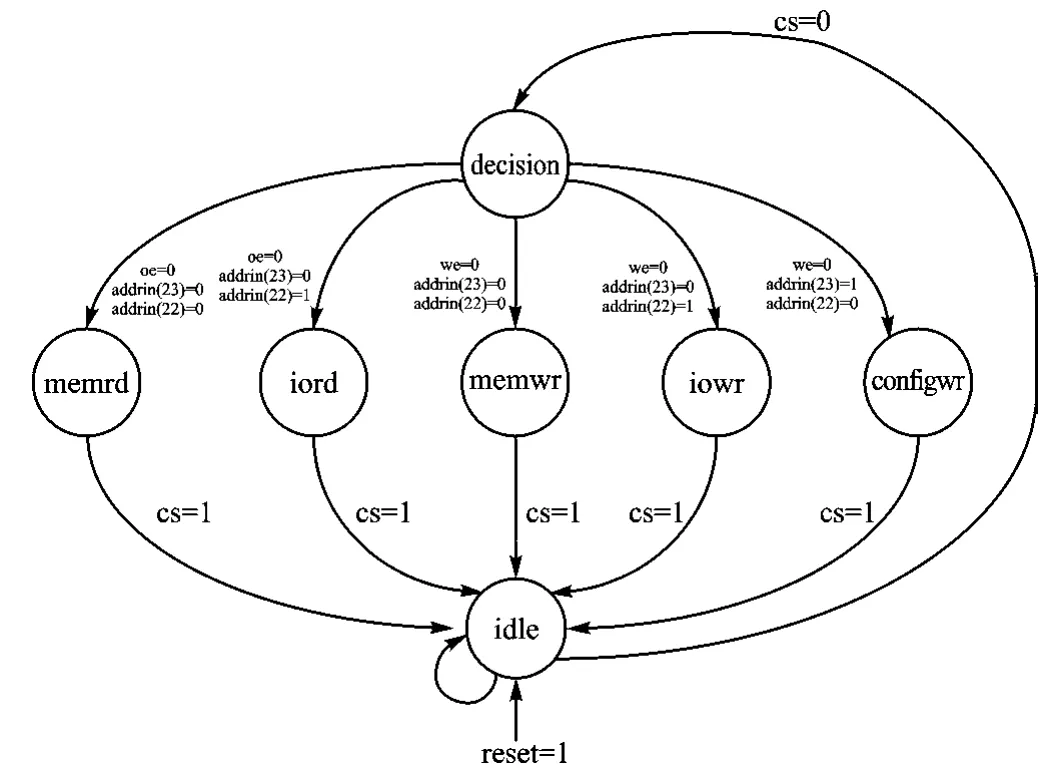

控制模块的逻辑设计同样采用状态机实现,分析LPC2478数据手册中“外部存储器读/写操作(External Memory Read Access/Write Access)”时序图,将控制模块的工作过程分为7个状态:idle状态(总线周期开始前或结束后)、decision状态(片选信号有效,总线周期开始)、memrd状态(读 Memory空间)、iord状态(读I/O空间)、memwr状态(写 Memory空间)、iowr状态(写I/O空间)、configwr状态(写Local Configuration寄存器)。根据以上划分,模块的状态机设计如图4所示。

图4 控制模块状态转移图

根据状态转移图,模块二复位后处于idle状态,等待总线上的片选信号;当cs信号有效时进入decision状态,然后根据oe(读)、we(写)、addin[23]及addin[22]等信号是否有效,选择进入下一级各状态;当cs信号无效时,模块重新进入idle状态,然后等待下一次总线周期到来。

3 仿真结果

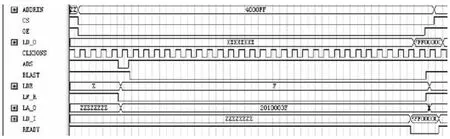

3.1 PCI发起单次读操作

图5为主控模块向被测板卡进行PCI读操作时,时序转换模块输出波形的仿真结果。图中各信号的定义如下:ADDRIN/OE为嵌入式处理器的24位地址信号/写信号;LA_O为时序转换模块输出的30位地址信号;LD_I为转换前的数据(PCI9054局部总线数据);LD_O为转换后的数据(嵌入式处理器读取的数据)。

图5 PCI发起单次读操作仿真结果

通过与PCI9054数据手册时序图比较,仿真结果符合要求。“PCI Initiator Single Read”时序图略——编者注。

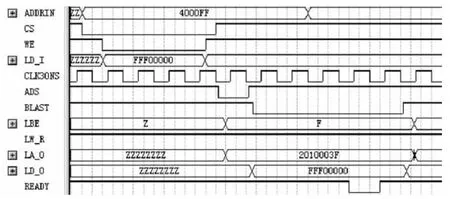

3.2 PCI发起单次写操作

图6为主控模块向被测板卡进行PCI写操作时,时序转换模块输出波形的仿真结果。图中各信号的定义如下:ADDRIN、LD_I、WE为嵌入式处理器的24位地址信号、32位数据信号、写信号;LA_O、LD_O为时序转换模块输出的30位地址信号、32位数据信号。

图6 PCI发起单次写操作仿真结果

通过与PCI9054数据手册“PCI Initiator Single Write”时序图比较,仿真结果符合要求。“PCI Initiator Single Write”时序图略——编者注。

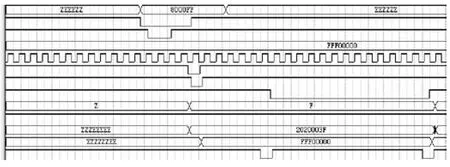

3.3 局部总线写配置寄存器操作

图7为嵌入式处理器写PCI9054配置寄存器时,时序转换模块输出波形的仿真结果。图中各信号的定义如下:ADDRIN、WE为嵌入式处理器的24位地址信号、写信号;CCS为配置寄存器片选;LA_O、LD_O为时序转换模块输出的30位地址信号、32位数据信号。

图7 局部总线写配置寄存器仿真结果

通过与PCI9054数据手册“Local Bus Write to configuration Register”时序图比较,仿真结果符合要求。“Local Bus Write to configuration Register”时序图略——编者注。

结 语

时序转换模块实现了LPC2478嵌入式处理器通过局部总线控制PCI接口芯片的功能。通过该模块的设计,解决了该型嵌入式处理器与PCI接口芯片局部总线兼容的问题,具有借鉴意义。实际应用中,时序转换模块已作为嵌入式PCI总线单板计算机的组成部分,用于板卡测试,工作状况稳定。

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

[1]金显峰,邱春玲,田地.嵌入式PCI总线主模式设计[J].计算机测量与制,2005,13(8):821-823.

[2]NXP.LPC2478Preliminary data sheet Rev.01 [EB/OL].(2007-07)[2013-10].http://www.nxp.com/.1-3,60,28.

[3]PLX Technology,Inc.PCI9054Data Book V2.1 [EB/OL].(2000-01)[2013-10].http://www.plxtech.com/.

[4]雷伏容.VHDL电路设计[M].北京:清华大学出版社,2006:247-248.