基于FPGA的电梯控制系统设计与实现

张志霞,陈宇轩,刘艳昌

(1.河南科技学院,河南 新乡 453003;2.电子科技大学,四川 成都 610054)

基于FPGA的电梯控制系统设计与实现

张志霞1,陈宇轩2,刘艳昌1

(1.河南科技学院,河南 新乡 453003;2.电子科技大学,四川 成都 610054)

针对传统单片机、PLC等方式设计的电梯控制系统外围电路复杂、性能不稳等缺点,提出一种基于FPGA的电梯控制系统的设计与实现方案.系统采用Altera公司的Cyclone II系列FPGA芯片EP2C8Q208C8作为主控芯片,利用自顶向下的模块化编程思想和Verilog HDL编程语言设计了一个6层电梯控制系统.经软件仿真和硬件实现,结果表明该控制系统能够满足设计要求,并能扩展到多层电梯,具有很强的适应性和实用性.

FPGA;电梯控制系统;Verilog HDL;控制模块

针对传统电梯控制系统中的PLC、单板机、单片机、单微机、多微机和人工智能等控制方式存在电路设计复杂、芯片使用多、出现问题不易查找、功能扩展困难、设计不灵活、效率低等问题[1-2],使用FPGA器件作为主控制器芯片,利用自顶向下的模块化编程思想和verilog HDL编程语言设计了一个6层电梯控制系统.该系统具有信号处理速度快、设计灵活、维护方便、升级容易、可在线编程、开发周期短、设计成本低等优点.另外,若对电梯控制模块和按键模块程序稍加修改,则系统可实现任意楼层的电梯控制.

1 电梯控制系统的总体设计

1.1 系统功能要求

系统实现的功能要求如下:

(1)各层电梯外部设有上升下降请求按键,电梯内部设有乘客所要到达1~6层楼的数字按键,电梯内外所在楼层数分别用一位数码管来显示,电梯运行状态分别用一块5×7点阵来表示.

(2)能够存储并指示电梯内外所有请求信号,并按照方向优先原则到达离电梯最近的楼层后,消除该请求信号,该层指示灯点亮,延迟1 s后,开门指示灯点亮电梯门自动打开,门开后等待5 s开门指示灯熄灭电梯门自动关闭,继续执行后面楼层请求信号.

(3)电梯停止后再启动运行规则为:首先考虑正在运行方向上是否有请求,有则继续运行,其次考虑反方向上是否有请求,有则转向运行,若都没有请求信号,则电梯停到当前楼层,处于等待状态.

(4)电梯具有超载报警和故障提示功能.

1.2 系统结构设计

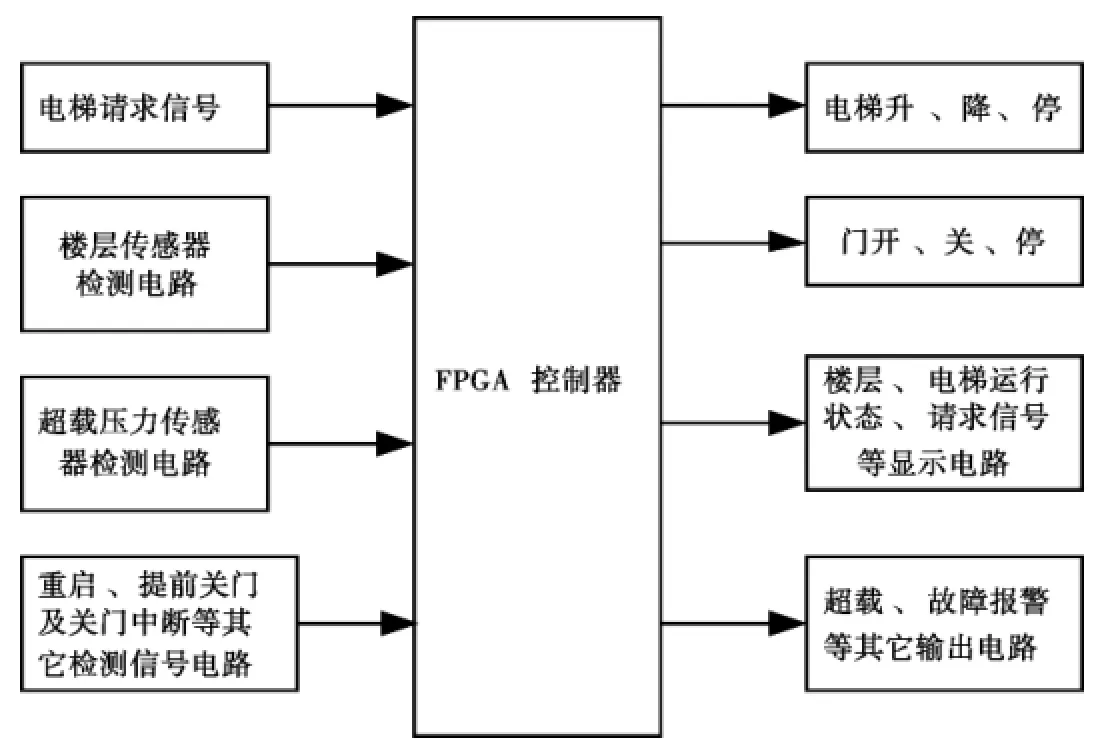

由于FPGA处理速度快,具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改[3-5],所以本文电梯控制器的硬件设计主要由FPGA控制器、各输入信号检测电路、各输出信号控制电路、显示驱动电路和其他电路组成.系统硬件结构如图1所示.

图1 系统结构Fig.1 System structure

2 电梯控制器的设计与实现

控制器设计使用Altera公司Cyclone II系列的EP2C8Q208C芯片,以Quartus II为软件开发平台[6-7],采用自上而下的设计方法,并运用Verilog HDL语言对各底层模块进行设计,实现了以软件替代硬件的模块化设计思想,以便程序的维护和升级.

2.1 底层各模块设计与实现

控制器底层模块主要由分频模块、电梯控制模块、按键消抖模块、按键处理模块、数码管驱动模块和点阵驱动模块等组成.

2.1.1 分频模块设计 分频模块的主要功能是把系统输入的50 MHz的时钟信号经分频后变为1 Hz的脉冲信号,作为控制模块的状态转移时钟信号.在Quartus II环境下,利用Verilog HDL语言编程,实现分频功能,并生成目标文件,编译验证其正确性,然后生成分频模块的元件符号.创建的分频模块电路符号如图2所示.

图2 分频模块电路符号Fig.2 Frequency module circuit symbol

2.1.2 控制模块设计 由于电梯控制模块是该控制系统的核心,主要实现对各存储信号进行比较、判断,对电梯运行情况进行处理来驱动系统的各状态流转,并控制其输出显示.所以系统采用有限状态机来设计电梯控制器,此算法简单,编程思路清晰,具体状态定义如下:

S0:WAIT表示等待状态,电梯处于运行停止后的某一楼层;

S1:UP表示上升状态,电梯处于上升过程;

S2:UPSTOP表示上升停止状态,电梯处于有效请求楼层并停止;

S3:OPENDOOR表示开门状态,电梯执行到某一楼层停止后处于开门状态;

S4:CLOSEDOOR表示关门状态,电梯开门5 s后,自动关门;

S5:DOWN表示下降状态,电梯处于下降过程;

S6:DOWNSTOP表示下降停止状态,电梯处于有效请求楼层并停止.

各状态在满足一定条件下转换,其状态转化如图3所示.

图3 电梯控制器状态转换Fig.3 State chart of elevator controller

图3中的状态转换条件如表1所示.

表1 电梯控制器状态转换条件Tab.1 State change condition of elevator controller

表1中,up_all可以实时地对各个向上请求信号合并,由于6楼为顶层,故将向上请求信号第6位置0.down_all可以实时地对各个向下请求信号合并,由于1楼为低层,故将向下请求信号第1位置0.request_all可以将各停靠请求信号实时地合并.

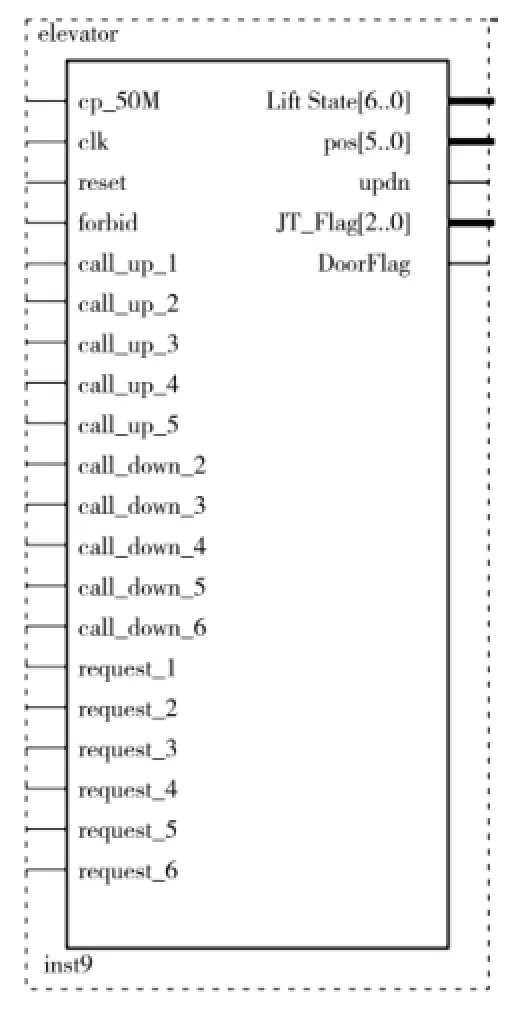

根据上述算法,在Quartus II环境下,利用Verilog HDL语言编程,实现电梯控制功能,并生成目标文件,编译验证其正确性,然后生成电梯控制模块的元件符号.创建的电梯控制模块电路符号如图4所示.

图4 电梯控制模块电路符号Fig.4 Elevator control module circuit symbol

图4中clk为各状态转移时钟1 Hz;cp_50 M为全局时钟50 MHz;reset为复位信号,低电平有效,使当前楼层停在第一层且处于等待状态;forbid为电梯强制禁止运行信号,高电平有效;call_up_1~5分别为电梯外部1~5楼上升请求信号按键,高电平有效,因为总共6层,所以6楼不设上升请求信号按键;call_down_2~6分别电梯外部2~6楼下降请求信号按键,高电平有效,因为没有负楼层,所以1楼不设下降请求信号按键;request_1~6分别为电梯内部1~6楼的停靠请求信号按键;LiftState[6..0]为电梯7种输出状态;Pos[5..0]为输出当前电梯所在楼层;updn为电梯上升和下降状态,高电平为上升,低电平为下降;JT_Flag[2..0]为点阵图形控制信号输出,其中取值3'b000~3'b100分别代表电梯等待状态时箭头图形灭、电梯上升及上升停止状态时箭头图形向上且滚动、电梯下降及下降停止状态时箭头图形朝下且滚动、电梯在上升状态开门时箭头向上且静止、电梯在下降状态开门时箭头朝下且静止;DoorFlag为电梯开、关门控制信号,其中“1”代表开门,“0”代表关门.

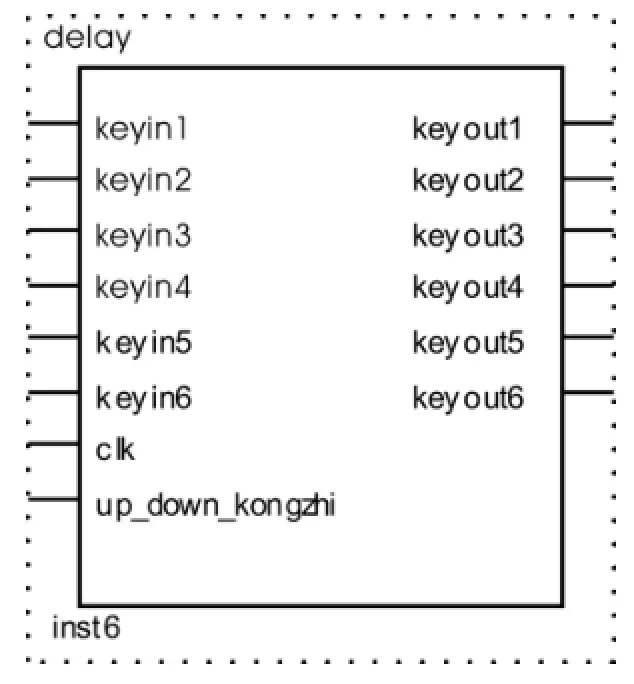

2.1.3 按键消抖模块设计 由于电梯的请求信号是通过按键产生,但是在按键请求的过程中会存在物理抖动现象,因此,本系统设计了按键消抖模块.在Quartus II环境下创建的按键消抖模块的电路符号如图5所示.其中clk为50MHz,keyin1~keyin6为电梯内部1~6层按键,key_out1~key_out6为经软件消抖处理的输出信号.

图5 按键消抖模块电路符号Fig.5 Press-key shaking disappears module circuit symbol

2.1.4 按键处理模块设计该模块主要实现对电梯各请求信号进行存储、并按照方向优先、循环执行的原则,在各请求信号中提取离电梯下一站最近的请求信号并输出.其中keyin1~keyin6为电梯内部1~6层按键经消抖处理后的输出信号,其对应按键的高电平有效;keyout1~keyout6为对应请求信号经过算法处理后的输出信号,高电平代表有请求,低电平代表无请求;up_down_kongzhi为电梯上升和下降运行状态控制信号,1代表上升,0代表下降.图6为Quartus II环境下创建的按键处理模块电路符号.

图6 按键处理模块电路符号Fig.6 Press-key processing module circuit symbol

2.1.5 数码管驱动模块设计 该模块用来驱动数码管显示当前楼层数.Quartus II环境下创建的数码管驱动模块电路符号如图7所示.其中a位数码管位选信号,b[6..0]数码管段选信号.

图7 数码管驱动模块电路符号Fig.7 Nixie tube the driver module circuit symbol

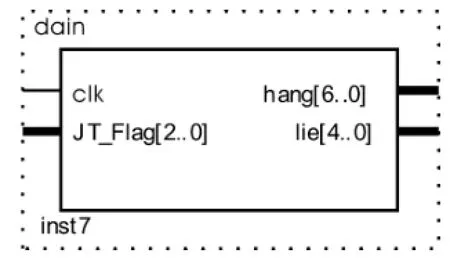

2.1.6 点阵驱动模块设计 该模块采用5*7点阵,用来对电梯当前运行状态进行显示.Quartus II环境下创建的点阵驱动模块电路符号如图8所示.其中,JT_Flag[2..0]为点阵图形控制输入信号;hang[6..0]为点阵的行选信号输出;lie[4..0]为点阵的列选信号输出.

图8 点阵驱动模块电路符号Fig.7 Dot-Matrix the driver module circuit symbol

2.2 顶层电路设计与实现

2.2.1 顶层电路设计 将上文所创建的各底层模块添加到原理图中,并对各个端口标记网络连接符,即可实现顶层电路设计原理图,如图9所示.

图9 电梯控制系统顶层电路设计Fig.9 Top-level circuit design of elevator control system

2.2.2 顶层电路软件仿真 对系统设计的电梯控制系统的顶层电路以10 ps代替1 s进行仿真,并假设每楼层间运行时间为1 s,电梯的初始状态为处于1楼关门等待状态,要求当电梯外部同时出现5楼和6楼的下楼按键请求信号时,电梯控制器根据方向优先和循环执行原则,先上升到最高请求层6楼并执行上升后停1s开门、开门后等待5s、关门后等1s,然后反向下降到5楼后,执行停1 s开门、开门后等待5 s、关门后等1 s继续下降,最终回到目标层1楼.仿真波形如图10所示.由仿真波形图10可以看出,电梯输出楼层pos[5..0]、电梯状态LiftState[6..0]、电梯运行方向标致输出JT_Flag[2..0]、电梯门开、关门状态DoorFlag和电梯上升、下降状态updn的变化及运行完全协调一致,验证系统设计的正确性.

图10 电梯控制系统程序仿真Fig.10 Procedure simulation chart of elevator control system

2.2.3 顶层电路硬件验证 将顶层电路设计文件通过JTAG模式下载到ASK2CB型FPGA开发板的核心芯片EP2C8Q208C8中,经过多次各楼层按键请求实验,整个系统运行正常,性能良好.

图11 电梯控制系统的硬件实现Fig.11 Hardware Implementation of elevator control system

图11为电梯控制系统获得4楼发出向下请求信号后,电梯处于该层开门等待状态时的硬件实现图.图中数码管显示为4表明电梯位于第4层,点阵图标箭头向下且被静止点亮表明电梯处于下降且等待状态,上面的第一个LED灯点亮表示电梯处于开门状态.

3 小结

本文设计了一个6层电梯控制系统.该系统采用方向优先控制方式,能有效缩短响应时间,提高用户请求率.软件仿真和硬件验证表明,电梯控制系统能够较好地控制电梯完成6层楼的载客服务,可靠性高,只要稍加修改采集模块和主控器模块中的参数配置就可实现任意楼层的电梯控制.系统可拓展性好、灵活性强、工作效率高、体积小、成本低,具有广阔的应用前景.

[1] 张汉杰.现代电梯控制技术[M].哈尔滨:哈尔滨工业大学出版社,2006.

[2] 刘岩飞.基于Altera FPGA/CPLD的电子系统设计与工程实践[M].北京:人民邮电出版社,2009.

[3] 华清远见嵌入式培训中心.FPGA应用开发入门与典型实例[M].北京:人民邮电出版社,2008:148-160.

[4] 高迎慧,侯忠霞,杨成林.基于FPGA的自动升降电梯控制器设计[J].辽宁工程技术大学学报,2007,25(2):242-244.

[5] 田红光.FPGA在电梯控制系统中的应用[J].微型机与应用,2011,30(24):15-17.

[6] 夏宇闻.Verilog数字系统设计教程[M].2版.北京:北京航空航天大学出版社,2008.

[7] 罗杰.Verilog HDL与数字ASIC设计基础[M].武汉:华中科技大学出版社,2008:188-196.

(责任编辑:卢奇)

Design and implementation of elevator control systembased on FPGA

Zhang Zhixia1,Chen Yuxuan2,Liu Yanchang1

(1.Henan Institute of Science and Technology,Xinxiang 453003,China;2.University of Electronic Science and Technology of China,Chengdu 610054,China)

A newFPGA-based elevator control systemwas designed and implemented in order to overcome the defects of traditional single-chip microcomputer,PLC-based control mode,such as the complexity of peripheral circuit and the instability of the performance.Using the FPGA chip EP2C8Q208C8 in Cyclone II series of Altera company as the main control chip,the systemdesigned a six-floor-elevator control systemwith the modular design method,and the Verilog HDL hardware description language.The software simulation and hardware implemention showed that the control systemcan meet the design requirements,and could extend to multi-floors elevator,and also has strong adaptability and practicality.

FPGA;elevator control system;Verilog HDL;control module

TP386

A

1008-7516(2014)03-0065-07

10.3969/j.issn.1008-7516.2014.03.015

2014-04-20

张志霞(1982-),女,河南平顶山人,硕士,助教.主要从事智能信号和图像处理技术研究.