高速单端同步总线模块中同步时钟的设计方法

李云彬

(中国电子科技集团公司 第四十一研究所,山东 青岛 266555)

0 引言

高速单端同步总线模块主要用于实现多通道的单端同步总线的数据通信[1]。通道数目最大支持512个,速率最大支持133Mbps,采用可配置的原则,支持数据的发送和接收。在高速的数据发送与接收过程中,高精度、高准确度、高稳定度、宽范围的相位/幅度可调的同步采样时钟成为影响多通道数据通信可靠性、抗干扰能力、通信速率等的一个关键因素。

在数据通信过程中,现有方法获取的同步采样时钟都是通过参考时钟直接来产生[2]。从一个参考时钟获得多个不同采样时钟,会导致每个采集板上的相位同步没有直接用采样时钟那样精度高,并且稳定性同样没有直接用采样时钟的高,直接影响了多通道数据通信的准确性和稳定性。

本文提出了一种适用于高速单端同步总线模块的同步时钟设计方法,它基于ADI公司高性能、动态特性优异、可双路输出的DDS芯片 AD9958BCPZ[3-4]来实现。

1 基于AD9958BCPZ的同步时钟设计

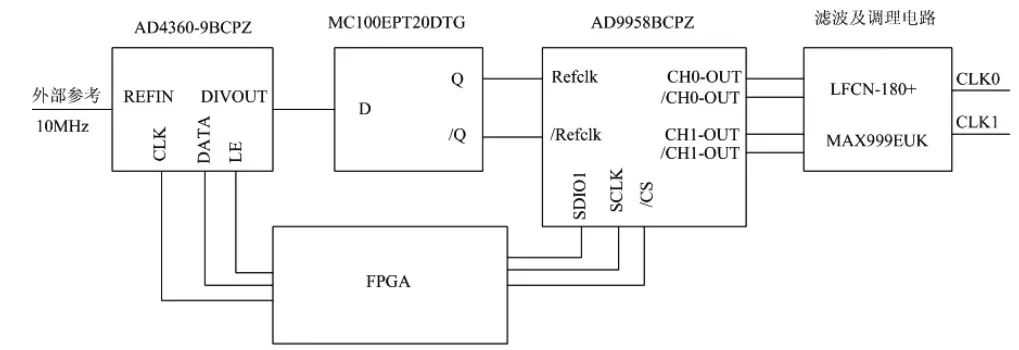

图1为基于AD9958BCPZ的同步时钟产生电路实现框图。

图1 基于AD9958BCPZ的同步时钟产生电路实现图

图1中,基于AD9958BCPZ的同步时钟设计方法主要包括精确参考时钟的获取、高性能同步时钟的产生、同步时钟的滤波及调理电路和FPGA控制四个部分。

1.1 精确参考时钟的获取

精确参考时钟的获取主要采用ADI公司的频率合成器ADF4360-BCPZ和ON Semiconductor公司的高速PECL逻辑门电路MC100EPT20DTG共同来实现。

ADF4360-BCPZ有3个24位的寄存器R、C、N,其中寄存器R、N中的控制字共同决定了VCO端输出频率,寄存器C决定了DIVOUT端的输出模式。

VCO端输出频率公式为:

其中,fVCO是VCO端输出频率;fREFIN是外部参考输入频率,范围10M-250MHz;R为14位分频计数器,由寄存器R控制,范围为1-16383;B为13倍频计数器,由寄存器N控制,范围为3-8191。

DIVOUT端选择A CNTR/2 OUT输出模式下的输出频率为:

其中,A为5位分频计数器,由寄存器N控制,范围为2-31。

为了在DIVOUT端得到稳定的25MHz时钟,由公式 (2)可知,VCO 端输出频率必须为(50A)MHz,这里取 A=2,即 fVCO=100MHz。选择鉴相频率为200kHz,环路带宽为10kHz,通过ADIsimPLL软件仿真得R=50, 即 B=500, 最终寄存器设置为 R=0x3000C9,C=0x31A4,N=0x1F40A。

高速PECL逻辑门电路MC100EPT20DTG把ADF4360-BCPZ得到的稳定的25MHz单端参考时钟转换为同频率的差分信号,提高抗干扰能力,提供一个波形稳定、干净的满足频率合成器AD9958BCPZ参考时钟要求的频率信号。

1.2 同步时钟发生

本文采用ADI公司的频率合成器AD9958BCPZ来实现高性能同步时钟的产生。AD9958BCPZ是一款高性能、动态特性优异、可双路输出的DDS芯片,每路可单独控制频率、相位/幅度;两个通道之间有固定的同步性,可支持多个设备的同步,并且产生最高频率为200MHz的双路信号;具有32位频率累加器、14位相位累加器、10位输出幅度累加器等,可实现高精度、高准确度、高稳定度、宽范围的相位/幅度可调的同步采样时钟,其电路结构简单、通道间隔离度高、功耗小。

输出信号频率的计算公式为:

其中,FTW为输出信号的频率控制字,范围为0-231。输出信号相位的计算公式为:

其中,POW为输出信号的相位控制字,范围为0-214。

输出信号频率的计算公式为:

其中,ACR为输出信号的幅度控制字,范围为0-210,Vmax与外接电阻RSET有关。

选择可编程串口操作模式为1位串行2线模式,串口控制器能自动识别被访问的寄存器字节地址;选择双通道;选择先高位后低位的数据传输模式;通过公式(3)、(4)、(5)计算出输出信号的频率、相位、幅度控制字。寄存器配置,使AD9958BCPZ输出相位/幅度可调的1KHz-133MHz的频率信号。寄存器设置为CSR=0xF0,FR1=0xCC0000,CFR=0x300,CFTW0=0x7FFFFFFF-0,CPOW0=0x3FFF-0,ACR=0x13FF-1000。

1.3 输出滤波器及比较器电路

滤波器及调理电路由陶瓷低通滤波器LFCN-180+和MAXIM公司的超高速轨迹比较器MAX999UK组成。

LFCN-180+有效滤除由相位截断、相位/幅度量化误差引起的AD9958BCPZ输出频率信号杂散,得到杂波抑制性能好的频率信号。

AD9958BCPZ输出的正弦波频率信号经过比较器MAX999UK转化为方波,得到所需要的同步时钟,同时MAX999UK也降低了频率信号的输出杂散。

1.4 FPGA控制

在本文中FPGA有以下3种主要作用:

1)产生标准的3线SPI读写时序对ADF4360-BCPZ的寄存器R、C、N进行配置,使ADF4360-BCPZ稳定锁定,输出稳定精确的参考时钟信号。

2)与上位机通信,接收上位机的命令字。

3)产生标准的3线SPI读写时序,按照接收到的命令字对AD9958BCPZ进行配置,控制输出1kHz-133MHz的频率信号。

2 结束语

本文是一种高速单端同步总线模块的同步时钟设计方法,实现高精度、高准确度、高稳定度、宽范围的相位/幅度可调的同步时钟的产生,频率分辨率可以达到0.116Hz,相位控制精度可以达到0.0220,使多通道数据通信更加高效准确。方法简单实用,同时简化了电路复杂程度和控制流程,更重要的是便于调试,大大缩短了调试周期;加上AD9958BCPZ自身卓越的通道间隔离度、高达16阶频率/相位/幅度调制能力提高了信号的抗干扰能力,使相邻信道的信号干扰降到最低,对多通道数据通信可靠性、抗干扰能力、通信速率等有显著提高。

[1]张庆民,安琪,等.高速同步总线的时序设计[J].系统工程与电子技术,2000.Vol.22(11).

[2]汤继星.基于DSP的直接数字频率合成(DDS)技术研究[D].南京理工大学,2008.

[3]赵云娣,杨小献.基于AD9958的双通道直接频率合成器的设计[J].无线电工程,2006.Vol.36,No.3.

[4]Analog Device,Inc.AD9958BCPZ 2-Channel,500MSPS DDS with 10-Bit DACs[OL].www.analog.com.